Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Семейства 32-разрядных МК с RISC-архитектуройСодержание книги

Поиск на нашем сайте

Семейство ColdFire. Основанный на концепции переменной длины команд, Co/dFire сочетает архитектурную простоту стандартного 32-разрядного RISC-процессора с экономией памяти. Использование архитектуры с инструкциями переменной длины дает значительные преимущества по сравнению со стандартной RISC-архитектурой с инструкциями фиксированной длины. Уплотненный двоичный код процессора ColdFire занимает меньшие объемы памяти, чем код RISC-процессора с инструкциями фиксированной длины. Это позволяет более эффективно использовать память системы для прикладной программы, а также выбирать более медленную и менее дорогостоящую память для достижения заданного уровня производительности. Интегрированные периферийные функции обеспечивают высокую эффективность и гибкость. Стандартная конфигурация предполагает наличие последовательного интерфейса, двух многофункциональных таймеров, программируемого сторожевого таймера и системной интеграции: управления внешними шинами, системной защиты, прерываниями, встроенного отладчика. Процессорное ядро MCF5204 имеет производительность 13,5 MIPS при тактовой частоте 33 МГц, при этом большинство команд выполняются за 1 цикл. Команды управления потреблением позволяют снижать интегральный показатель потребляемой мощности. Системный интерфейс обеспечивает прямое подключение ОЗУ, ПЗУ и внешних устройств с разрядностью 8 или 16, а также обработку прерываний и системную защиту (имеется 16-битный сторожевой таймер с предделителем, отслеживаются двойные ошибки шины, превышение времени отклика устройства на шине и т.д.). MCF5204 содержит встроенный кэш команд объемом 512 байт и быстрое статическое ОЗУ того же объема, что обеспечивает 1-цикловый доступ к наиболее критичным командам и данным. Асинхронный последовательный интерфейс обеспечивает дуплексную работу с поддержкой модемных сигналов управления (CTS, RTS). Двухканальный 16-битный универсальный таймер с 8-битным предделителем имеет разрешение 30 нс при тактовой частоте 33 МГц. MCF5206 имеет производительность 17 MIPS при частоте 33 МГц, содержит встроенный контроллер DRAM, а также синхронный последовательный интерфейс M-bus для подключения ЖК-дисплеев, последовательного EEPROM и других устройств с последовательным доступом. Семейства МК на базе PowerPC. Архитектура микропроцессора PowerPC основывается на архитектуре POWER (Performance Optimization With Enhanced RISC – оптимизация производительности с расширенной RISC-архитектурой), первоначально предложенной фирмой IBM. Архитектура была переопределена фирмой Motorola для того, чтобы обеспечить более эффективные однокристальные решения. Процессоры PowerPC позволяют реализовать на их основе различные системы – от недорогих портативных устройств до мультипроцессорных суперкомпьютеров. Они стали основой RISC-ядра мощных высокопроизводительных микроконтроллеров и интегрированных процессоров семейств MPC 500 и MPC 800. Основной особенностью МК с ядрами PowerPC является суперскалярная RISC-архитектура. В состав ядра PowerPC входят исполнительные блоки процессора, кэш-память и блоки управления памятью. Исполнительные блоки, работающие параллельно, представлены целочисленным блоком, выполняющим все команды целочисленной арифметики, блоком загрузки/хранения, выполняющим операции перемещения данных регистровым блоком, содержащим 32 32-разрядых регистров общего назначения, а также блоки данных с историей последних операций, блоком переходов, состоящим из формирователя следующего адреса, очереди предварительной выборки команд и системы обработки прерываний, а также фонового отладчика, позволяющего подробно прослеживать работу процессора, включая работу конвейера и кэш-памяти. Двунаправленный ассоциативный кэш команд объемом 4К организован в виде 128 наборов по две линии из четырех слов в каждом. Физически адресуемый кэш данных объемом 4К, также организованный в виде двунаправленных ассоциативных наборов, имеет 1-цикловый доступ при попадании и 1-цикловую задержку при непопадании. Блок управления памятью, осуществляющий трансляцию логических адресов в физические, содержит раздельные 32-входовые буферы трансляции для памяти команд и данных.

Специализированные микропроцессоры. Цифровые процессоры обработки сигналов. DSP-процессоры предназначены для осуществления цифровой обработки сигнала — математических манипуляций над оцифрованными сигналами. Они широко применяются в беспроводных системах, аудио- и видеообработке, системах управления. С ростом числа приложений, использующих DSP, и сложности алгоритмов обработки увеличивается и требования к ним в плане повышения быстродействия и оснащенности интерфейсными и другими специализированными узлами. К настоящему времени появилось множество типов DSP, как универсальных, так и ориентированных на достаточно узкий круг задач. Естественно, ни один из процессоров не может подойти для всех приложений. Например, для таких портативных устройств, как мобильные телефоны, портативные цифровые плееры, стоимость, степень интеграции и потребляемая мощность являются первостепенными, а максимальная производительность зачастую не нужна (т.к. обычно влечет за собой значительное повышение потребляемой мощности, не давая преимуществ при обработке относительно низкоскоростных аудиоданных). В то же время для гидроакустических или радиолокационных систем определяющими параметрами являются скорость работы, наличие высокоскоростных интерфейсов и удобная система разработки, а стоимость является второстепенным критерием. Кроме того, во многих случаях имеет смысл учитывать и место на рынке, занимаемое поставщиком процессора, т.к. далеко не все производители могут предоставить в ваше распоряжение спектр процессоров, покрывающих все ваши потребности. Сложившееся к настоящему времени распределение рынка между ведущими поставщиками (см. табл. 1) показывает, что 4 компании, стоящие в начале списка, поставляют более 80% всех используемых в мире DSP. Именно эти компании наиболее известны и на российском рынке, и их продукция часто упоминается.

Таблица 25. Основные производители DSP и принадлежащие им доли рынка

Следует помнить, что производители DSP, проектируя новые микросхемы, достаточно четко позиционируют их для использования в тех или иных приложениях. Это оказывает влияние и на их архитектуру, и на быстродействие, и на оснащение процессора тем или иным набором периферийных модулей. В таблице 2 показано позиционирование DSP с точки зрения их создателей.

Таблица 26. Области применения семейств сигнальных процессоров разных производителей

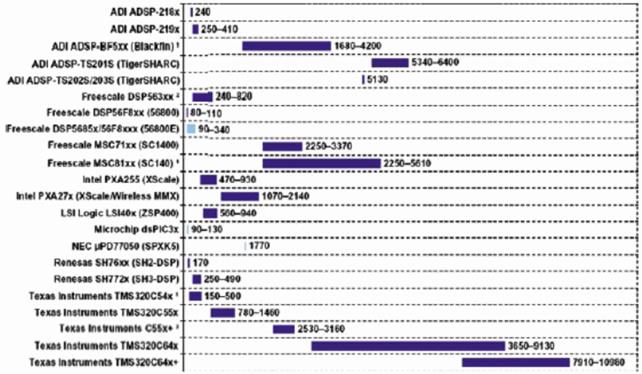

Формат данных и разрядность Одна из основных характеристик цифровых сигнальных процессоров — формат обрабатываемых данных. Все DSP работают либо с целыми числами, либо с числами в формате с плавающей точкой, причем для целых чисел разрядность составляет 16 или 32, а для чисел с плавающей точкой она равна 32. Выбирая формат данных, необходимо иметь в виду следующее: DSP с целочисленными данными (или данными с фиксированной точкой) обычно дешевле и обеспечивают большую абсолютную точность при равной разрядности (т.к. на мантиссу в 32-битном процессоре с фиксированной точкой отводятся все 32 бита, а в процессоре с плавающей точкой — только 24). В то же время динамический диапазон сигналов, с которыми могут без искажений работать процессоры, у процессоров с фиксированной точкой значительно уже (на несколько десятичных порядков). При относительно простых алгоритмах обработки это может быть неважно, т.к. динамический диапазон реальных входных сигналов чаще всего меньше, чем допускает DSP, однако в некоторых случаях возможно возникновение ошибок переполнения при выполнении программы. Это приводит к принципиально неустранимым нелинейным искажениям выходного сигнала, аналогичным искажениям из-за ограничения в аналоговых схемах. Следовательно, при выборе DSP необходимо тщательно анализировать алгоритм обработки и входные сигналы для правильного выбора разрядности и типа арифметики. Иногда при невозможности подобрать подходящий процессор с плавающей точкой (из-за большей его стоимости или энергопотребления) используют DSP с фиксированной точкой и сжатие динамического диапазона обрабатываемых сигналов (компрессию), однако это приводит к увеличению сложности алгоритма обработки сигнала и повышает требования к быстродействию. Конечно, можно эмулировать операции с плавающей точкой и на процессоре с целочисленной арифметикой или перейти к обработке чисел удвоенной разрядности, однако это также значительно усложняет программу и значительно снижает быстродействие. Несмотря на все ограничения, большинство встроенных приложений используют процессоры с фиксированной точкой из-за меньшей цены и энергопотребления. Увеличение количества разрядов повышает стоимость, размер кристалла и число необходимых выводов процессора, а также необходимый объем внешней памяти. Поэтому разработчики стремятся использовать кристалл с минимально возможной разрядностью. Стоит заметить, что разрядность данных и разрядность команд процессоров не всегда эквивалентны. Скорость Ключевой параметр при выборе процессора — это скорость. Она влияет на время выполнения обработки входного сигнала и, следовательно, определяет его максимальную частоту. Одна из самых частых ошибок разработчика — отождествление тактовой частоты и быстродействия, что в большинстве случаев неправильно. Очень часто скорость работы DSP указывают в MIPS (миллионах инструкций в секунду). Это наиболее просто измеряемый параметр. Однако проблема сравнения скорости различных DSP состоит в том, что процессоры имеют различные системы команд, и для выполнения одного и того же алгоритма разными процессорами требуется разное число этих команд. Кроме того, иногда для выполнения различных команд одним процессором требуется различное количество тактов синхронизации. В результате процессор со скоростью 1000 MIPS вполне может оказаться в разы медленнее процессора со скоростью 300 MIPS, особенно при различной их разрядности. Одно из решений этой проблемы — сравнивать процессоры по скорости выполнения определенных операций, например, операции умножения с накоплением (MAC). Скорость выполнения таких операций критична для алгоритмов, использующих цифровую фильтрацию, корреляцию и преобразования Фурье. К сожалению, такая оценка также не дает полной информации о реальном быстродействии процессора. Наиболее точной является оценка скорости исполнения определенных алгоритмов — например, КИХ- и БИХ-фильтрации, однако это требует разработки соответствующих программ и тщательного анализа результатов тестирования. Существуют компании, занимающиеся анализом и сравнением процессоров по основным характеристикам, в том числе и по скорости. Лидером среди таких компаний является BDTI — Berkeley Design Technology. В качестве примера на рисунке 58 показано сравнение по скорости современных DSP разных производителей.

Рис. 58 – Пример сравнения быстродействия различных DSP с фиксированной точкой

Организация памяти Организация системы памяти процессора влияет на производительность. Это связано с тем, что ключевые команды DSP являются многооперандными и ускорение их работы требует одновременного чтения нескольких ячеек памяти. Например, команда MAC требует одновременного чтения 2 операндов и самой команды для того, чтобы ее можно было выполнить за 1 такт. Это достигается различными методами, среди которых применение многопортовой памяти, разделение на память программ и память данных (Гарвардская архитектура), использование кэша команд и т.д. Необходимый объем памяти определяется приложением. Необходимо учитывать, что встроенная в процессор память обычно имеет значительно большую скорость работы, чем внешняя, однако увеличение ее объема увеличивает стоимость и энергопотребление DSP, а ограниченный объем памяти программ не позволяет хранить сложные алгоритмы. В то же время при достаточности этого объема для ваших целей наличие встроенной памяти позволяет значительно упростить конструкцию в целом и понизить ее размеры, энергопотребление и стоимость. Большинство DSP с фиксированной точкой, применяющиеся во встраиваемых приложениях, предполагают малый объем внутренней памяти, обычно от 4 до 256 Кбайт и невысокую разрядность внешних шин данных. В то же время DSP с плавающей точкой обычно предполагают работу с большими массивами данных и сложными алгоритмами и имеют либо встроенную память большого объема, либо большую разрядность адресных шин для подключение внешней памяти (а иногда и то, и другое). Еще раз подчеркнем — выбор типа и объема памяти должен быть результатом тщательного анализа приложения, в котором используется DSP.

|

||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-12; просмотров: 292; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.139.235.177 (0.014 с.) |