Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Организация стековых (магазинных) запоминающих устройствСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

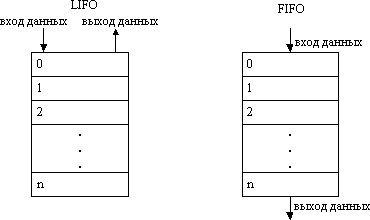

ЗУ со стековой организацией широко используется при построении системы прерываний ЭВМ, а также при программировании алгоритмов, связанных с обработкой данных типа вектор, массив (переменных с индексами). Магазинная (стековая) память организуется по принципу “последний пришел, первый вышел” (LIFO), или “первый пришел, первый вышел” (FIFO). Такая организация памяти является фактически безадресной. Однако регистр адреса в такой памяти имеется и называется указателем стека (УС) (SP-SteakPointer).

Рисунок - Принцип организации стековой памяти

В первом типе памяти новое слово заносится в верхнюю ячейку, ранее занесенные данные проталкиваются вниз. При считывании наоборот, последнее слово выталкивается вверх первым. В случае организации типа FIFO новое слово заносится в верхнюю ячейку, ранее записанные слова выталкиваются вниз. Чаще используют память типа “последний пришел, первый вышел”. Одна из основных проблем магазинных ЗУ – переполнение стека, которое ведёт к потере информации, поэтому не допустимо. Следить за возможным переполнением должен сам программист. Недостаток ЗУ магазинного типа – большие затраты оборудования и, следовательно, высокая удельная стоимость: сдвиговые регистры сложнее обычных.

10. Организация оперативной памяти. Многоблочная память

Оперативная память ЭВМ (ОЗУ (оперативное запоминающее устройство) или RAM (randomaccessmemory — память с произвольным доступом) — энергозависимая часть системы компьютерной памяти, в которой временно хранятся данные и команды, необходимые процессору для выполнения им операции. Особенности работы ОЗУ: Оперативная память может сохранять данные лишь при включенном компьютере. Поэтому при его выключении обрабатываемые данные следует сохранять на жестком диске или другом носителе информации. При запуске программ информация поступает в ОЗУ, например, с жесткого диска компьютера. Пока идет работа с программой она присутствуют в оперативной памяти (обычно). Как только работа с ней закончена, данные перезаписываются на жесткий диск. Другими словами, потоки информации в оперативной памяти очень динамичны. ОЗУ представляет собой запоминающее устройство с произвольным доступом. Это означает, что прочитать/записать данные можно из любой ячейки ОЗУ в любой момент времени. Для сравнения, например, магнитная лента является запоминающим устройством с последовательным доступом.

Типы оперативной памяти: Принято выделять два вида оперативной памяти: статическую (SRAM) и динамическую (DRAM). SRAM используется в качестве кэш-памяти процессора, а DRAM - непосредственно в роли оперативной памяти компьютера. Внешне оперативная память персонального компьютера представляет собой модуль из микросхем (8 или 16 штук) на печатной плате. Модуль вставляется в специальный разъем на материнской плате. Основными характеристиками ОЗУ являются информационная емкость и быстродействие. Емкость оперативной памяти на сегодняшний день выражается в гигабайтах. Основной особенностью ОП является её многоблочная организация. Связано это с тем, что ёмкость отдельных БИС ЗУ ограничена, поэтому для построения ОП необходимого объёма приходится использовать несколько ЗУ, организованных в единое целое. ОП строится по многоблочной схеме по двум причинам: технической и экономической. Технические причины: ёмкость ОП при многоблочной организации можно наращивать практически неограниченно без дополнительного проектирования БИС и без уменьшения быстродействия, т.к. время обращения к многоблочной памяти будет практически таким же, как и время обращения к отдельным её блокам. Экономическая причина: из однотипных блоков ЗУ, выпускаемых серийно, можно строить память необходимой ёмкости, стоимости и быстродействия. В противном случае необходимо было бы выпускать целую гамму ЗУ различных типов и размеров. При этом стоимость ОП будет выше, чем для случая однотипных блоков. Многоблочная память (multibunkmemory) — вид оперативной памяти, организованной из нескольких независимых блоков, допускающих одновременное обращение к ним, что повышает ее пропускную способность.

В функциональном отношении многоблочная память рассматривается как одно ЗУ с емкостью, равной сумме емкостей блоков, и быстродействием, примерно равным быстродействию одного блока.

11. Организация оперативной памяти с многоканальным доступом. Схема анализа приоритета при подключении каналов

Алгоритм выдачи сигнала приоритета:

12. Организация памяти. Иерархические уровни. Двух- и трехуровневая организация памяти Структура памяти ЭВМ:

13. Организация прямого доступа к памяти Одним из способов обмена данными с ПУ(программное устройство) является обмен в режиме прямого доступа к памяти (ПДП). В этом режиме обмен данными между ПУ и основной памятью микроЭВМ происходит без участия процессора. Обменом в режиме ПДП управляет не программа, выполняемая процессором, а электронные схемы, внешние по отношению к процессору. Обычно эти схемы размещаются в специальном контроллере, который называется контроллером прямого доступа к памяти. Режим ПДП обычно используется при начальной загрузке программ в основную память микроЭВМ из устройств ввода и для организации обмена данными с быстродействующими внешними запоминающими устройствами (дисковыми накопителями). Контроллер ПДП подключается к основной памяти посредством системного интерфейса. При этом возникает проблема совместного использования шин системного интерфейса процессором и контроллером ПДП. Существует два основных способа решения этой проблемы: 1. Реализация обмена в режиме ПДП с захватом цикла. 2. Реализация обмена в режиме ПДП с блокировкой процессора. Наиболее простой способ организации ПДП с захватом цикла состоит в использовании контроллером ПДП тех машинных циклов процессора, когда процессор не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора и не снижая его производительности. Однако при использовании такого способа организации ПДП обмен возможен только в случайные моменты времени и одиночными байтами, что не всегда является удобно. Поэтому на практике чаще используется режим ПДП с захватом цикла и принудительным отключением процессора от шин системного интерфейса. Для реализации такого режима системные интерфейс дополняется двумя линиями для передачи управляющих сигналов: «Запрос прямого доступа к памяти» (ЗПДП) и «Подтверждение прямого доступа к памяти» (ППДП). Управляющий сигнал ЗПДП формируется контроллером ПДП. Процессор, получив этот сигнал, приостанавливает выполнение очередной команды, не дожидаясь ее завершения, выдает в системный интерфейс управляющий сигнал ППДП и отключается от шин системного интерфейса. С этого момента управление шинами системного интерфейса передается контроллеру ПДП. Контроллер по шинам системного интерфейса осуществляет обмен одним байтом или словом данных с памятью микроЭВМ, а затем, сняв сигнал ЗПДП, возвращает управление системным интерфейсом процессору. Как только контроллер ПДП будет готов к обмену следующим байтом, он вновь захватывает цикл процессора. Эта процедура будет продолжаться до тех пор, пока не будут переданы все данные. В промежутках между сигналами ЗПДП процессор продолжает выполнять команды программы. Тем самым выполнение программы процессора замедляется, но в меньшей степени, чем при обмене в режиме прерывания. Прямой доступ в память с блокировкой процессора отличается от ПДП с захватом цикла тем, что управление системным интерфейсом передается контроллеру ПДП на все время обмена блоком данных. Такой режим ПДП необходим в тех случаях, когда процессор не успевает выполнить хотя бы одну команду между очередными операциями обмена в режиме ПДП, и поэтому режим захвата цикла не имеет смысла. Такая ситуация возникает тогда, когда время обмена одним байтом между ПУ и памятью сопоставима с циклом процессора из-за малой производительности последнего.

Для организации обмена данными между памятью и ПУ контроллер должен иметь в своем составе регистр адреса для обращения к памяти и счетчик байт для подсчета числа переданных байт. Перед началом обмена процессор должен загрузить в регистр начальный адрес выделенной ПУ области памяти, а в счетчик байт – размер этой области. Таким образом, контроллер подготавливается к выполнению операции ввода данных в режиме ПДП. Далее в процессе передачи данных содержимое регистра адреса и счетчика байт изменяется. После передачи очередного байта в память содержимое регистра адреса увеличивается на единицу, а из содержимого счетчика байт вычитается единица. Как только содержимое счетчика станет равно нулю, контроллер прекратит передачу данных от ПУ в память, поскольку нужное количество байт уже передано и выделенная область памяти заполнена. К одному контроллеру ПДП можно подключать несколько ПУ, которые получают право обмена данными с памятью в соответствии с их приоритетами. Контроллеры ПДП обычно реализуются в виде одной микросхемы, к которой подключаются несколько ПУ.

14. Принципы защиты информации. Защита информации при страничной адресации ЗИ необходима когда машина имеет дело с более чем 1 задачей одновременно и/или более чем с 1 оператором для того, чтобы обеспечить ЗИ, принадлежащей первой задаче (оператору) от воздействия программ другой задачи (операторов).

В больших сложных устройствах аппаратуры защиты устанавливаются разные статусы для разных устройств памяти. Пример, некоторым пользователям могут быть разрешены произвольные обращения к одним участкам памяти, обращения только для чтения информации в качестве программы к 3-им, любого обращения к 4-м. Цепи защиты памяти являются частью устройств формирования исполнительных адресов и рассматриваются вместе с этим устройствами. При реализации функции защиты на месте аппаратной относительной адресации могут быть дополненными специальными цепями защиты. ЗИ при страничной адресации Может быть обеспечена любым вариантом страничной организации памяти без каких либо дополнений. Перед тем как передать управление программой пользователю операционная система расставляет в дискретных регистрах физический номера страниц. Это физические номера тех страниц, к которым программа пользователя разрешено обращаться. ОС расставляет их в дискретные регистры, соответственно тем материальным адресам, по которым программа пользователя будет к ним обращаться. Если по сведениям ОС некоторым материальным номера не должен использоваться в данной программе пользователя и ОС не выделило под него никакой физический страницы, то в соответственный дискртеторных регистр ОС занесет пустой номер физической страницы.

Единственное дополнение, которое было бы желательно сделать в дешифратор, присоединенный к разрядом физические номера страницы в используемом адресе, который обнаруживая бы появления в этих разрядах пустого номера и.те. формировался бы сигнал прерывания или вызова супервайзера в случае попытки программы пользователя обращаться к закрытой странице памяти.

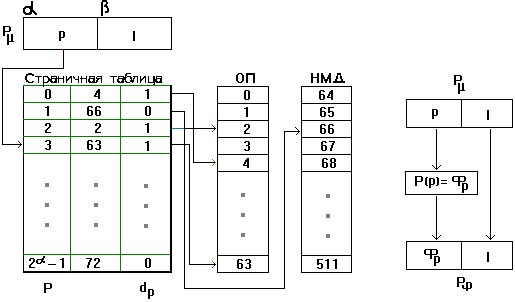

15. Организация виртуальной памяти Виртуальная память – технология управления памятью ЭВМ, разработанная для многозадачных операционных систем. При использовании данной технологии для каждой программы используются независимые схемы адресации памяти, отображающиеся тем или иным способом на физические адреса в памяти ЭВМ. Позволяет увеличить эффективность использования памяти несколькими одновременно работающими программами, организовав множество независимых адресных пространств, и обеспечить защиту памяти между различными приложениями. Также позволяет программисту использовать больше памяти, чем установлено в компьютере, за счет откачки неиспользуемых страниц на вторичное хранилище. При использовании виртуальной памяти упрощается программирование, так как программисту больше не нужно учитывать ограниченность памяти, или согласовывать использование памяти с другими приложениями. Для программы выглядит доступным и непрерывным все допустимое адресное пространство, вне зависимости от наличия в ЭВМ соответствующего объема ОЗУ. Применение механизма виртуальной памяти позволяет: · упростить адресацию памяти клиентским программным обеспечением; · рационально управлять оперативной памятью компьютера (хранить в ней только активно используемые области памяти); · изолировать процессы друг от друга (процесс полагает, что монопольно владеет всей памятью). В настоящее время эта технология имеет аппаратную поддержку на всех современных бытовых процессорах. В то же время во встраиваемых системах и в системах специального назначения, где требуется либо очень быстрая работа, либо есть ограничения на длительность отклика (системы реального времени) виртуальная память используется относительно редко. ВП разделена на аппаратно-независимую и аппаратно-зависимую части. Коротко рассмотрим, что и каким образом входит в аппаратно-зависимую часть подсистемы управления виртуальной памятью. При работе машины с ВП, используются методы страничной, сегментной и сегментно-страничной организации памяти. Рассмотрим первую форму организации ВП – страничную организацию (СО). При СО, все ресурсы памяти, как оперативной, так и внешней представляются для пользователя единым целым. Пользователь работает с общим адресным пространством. Виртуальная память разбивается на равные страницы, которые содержат определённое фиксированное количество ячеек памяти. Передача информации между памятью и диском всегда осуществляется целыми страницами. Страницы имеют фиксированную длину, обычно являющуюся степенью числа 2, и не могут перекрываться. На рисунке 1 изображена схема Страничной организации виртуальной памяти.

Рис.1 Страничная организация Виртуальной Памяти. Виртуальные адреса делятся на страницы (page), соответствующие единицы в физической памяти образуют страничные кадры (pageframes), а в целом система поддержки страничной виртуальной памяти называется пейджингом (paging). Виртуальный адрес в страничной системе упорядоченная пара (p,d), где p - номер страницы в виртуальной памяти, а d - смещение в рамках страницы p, где размещается адресуемый элемент. Система отображения виртуальных адресов в физические сводится к системе отображения виртуальных страниц в физические и представляет собой таблицу страниц, которая адресуется при помощи специального регистра процессора и позволяет определить номер кадра по виртуальному адресу. В большинстве современных компьютеров со страничной организацией виртуальной памяти все таблицы страниц хранятся в основной памяти, а быстрота доступа к элементам таблицы текущей виртуальной памяти достигается за счет наличия сверхбыстродействующей буферной памяти (кэша). Сегментно-страничная организация памяти требует более сложной аппаратурно-программной организации. На рисунке 2 подробно показан способ организации ВП с ССО. Адрес ячейки в данном случае складывается из 3х частей: первая содержит номер самого сегмента (S egment), по этому номеру машина обращается к сегментной таблице. Вторая часть адреса содержит номер искомой страницы (p age), которая находится внутри выбранного сегмента и третья смещение (l ength), по которому находится требуемый адрес. Pµ, обведенное в двойную рамку показывает математический адрес, а P ф физический. Как и при СО, смещение l переписывается в ячейку физического адреса без изменений. Вверху рисунка, аббревиатурой N обозначен номер какой-нибудь программы пользователя. А0с индексом 1 обозначает конкретный начальный адрес сегментной таблицы для данной программы. Сначала берется этот адрес и номер сегмента S из регистра математического адреса. Оба этих адреса складываются в сумматоре, который изображен в виде обведенного плюса. Получившийся адрес А1 + S является входом в сегментную таблицу (изображен в первой колонке сегментной таблицы). Далее, благодаря этому адресу, отыскивается соответствующий адрес страничной таблицы (А0 с индексом 2), который в свою очередь суммируется с номером искомой страницы p в сумматоре. Результирующая сумма есть вход в страничную таблицу. Структура страничной таблицы нам уже знакома.

|

|||||||||

|

Последнее изменение этой страницы: 2016-08-06; просмотров: 907; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.152.168 (0.015 с.) |