Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Дизъюнкция (логическое сложение). Операция ИЛИСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

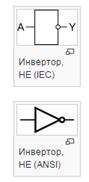

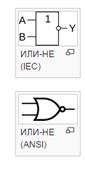

Инверсия функции конъюнкции. Операция И-НЕ (штрих Шеффера) Инверсия функции дизъюнкции. Операция ИЛИ-НЕ (стрелка Пирса) Эквивалентность (равнозначность), ИСКЛЮЧАЮЩЕЕ_ИЛИ-НЕ Сложение (сумма) по модулю 2 (Исключающее_ИЛИ, неравнозначность). Инверсия равнозначности.

Комбинационная схема (КС), или схема «без памяти», состоит из логических элементов (ЛЭ), соединенных между собой (выходы одних ЛЭ соединены со входами других ЛЭ), причем обратные связи отсутствуют. Под комбинационной схемой (КС) понимают схему, комбинация сигналов на выходе которой в любоймомент времени однозначно определяется комбинацией сигналов на её вход Примером КС могут служить разнообразные шифраторы, дешифраторы, преобразователи кодов,сумматоры и целый ряд других схем, не содержащих элементов памяти. ЛЭ как физическое устройство: Физически логические элементы могут быть выполнены · механическими, · электромеханическими (на электромагнитных реле), · электронными (на диодах и транзисторах), · пневматическими, · гидравлическими, · оптическими и др. С развитием электротехники от механических логических элементов перешли к электромеханическим логическим элементам (на электромагнитных реле), а затем к электронным логическим элементам на электронных лампах, позже — на транзисторах. 17. Обратная связь. Бистабильная ячейка–триггер. RS-триггер. D-триггер. Т-триггер. Обратная связь – зависимость текущих воздействий на объект от его состояния, обусловленного предшествующими воздействиями на этот же объект. Триггер – электронная схема, обладающая двумя устойчивыми состояниями. Переход из одного устойчивого состояния в другое происходит скачкообразно под воздействием управляющих сигналов. При этом также скачкообразно изменяется уровень напряжения на выходе триггера. В отличие от комбинационных схем состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент времени, но и предыдущим состоянием триггера. Триггеры служат основой для построения регистров, счетчиков и других элементов, обладающих функцией хранения. Главной частью любого триггера является запоминающая ячейка (ЗЯ). Схема запоминающей ячейки на элементах "И-НЕ" представлена на рис. 1.5. RS-триггер

Это Reset Set триггер (RS триггер) Входной сигнал S (Set) служит для установки ЗЯ в состояние " 1" (Q=1, Q=0). Сигнал R (Reset) устанавливает ЗЯ в состояние " 0 " (Q=0, Q=1). Активными значениями для них являются сигналы низкого уровня. Пусть на входы ЗЯ поданы сигналы: S=0, R=1. Тогда при любом исходном состоянии ЗЯ на выходе элемента 1 установится высокий уровень напряжения. Так как на входы элемента 2 поступают значения Q и R, то на его выходе будет сигнал низкого уровня. Таким образом, ЗЯ перейдет в состояние " 1 ". Аналогично при S=1, R=0 запоминающая ячейка перейдет в состояние Q=0, Q=1, то есть в " 0 ". Если S=1, R=1, то состояние ЗЯ будет определяться ее предыдущим состоянием. Если ЗЯ находилась в состоянии " 1 ", то сигнал Q=0, поступая на вход элемента 1, подтвердит состояние его выхода Q=1. На входы элемента 2 поступят сигналы только высокого уровня. Поэтому его выход будет находиться в состоянии Q=0, то есть не изменится. Если ЗЯ находилась в состоянии " 0 ", то сигнал Q=0, поступая на вход элемента 2, подтвердит состояние его выхода Q=1. В свою очередь, выход элемента 1 также останется без изменения. Таким образом, эта комбинация входных сигналов соответствует режиму хранения. Если на входы S и R поданы сигналы низкого уровня (S = R = 0), то сигнал на выходах элементов 1 и 2 будет высоким (Q = Q = 1). При переводе ЗЯ в режим хранения (S = R = 1), выходы элементов 1 и 2 могут установиться в произвольное состояние. Поэтому комбинация сигналов S = R = 0 на управляющих входах не используется. Работа триггерной схемы определяется не таблицей истинности, как для комбинационной логической схемы, а таблицей переходов. Таблица переходов показывает изменение состояния триггера при изменении состояния входных сигналов в зависимости от его текущего состояния. Таблица переходов запоминающей ячейки, показанной на рис. 1.5, представлена в табл. 1.3.

D-триггер (защелка):

D-триггер, также как и другие типы триггеров имеют два устойчивых состояния. D-триггеры имеет в своем составе два входа: информационный — D и вход синхронизации C, т.е. D-триггер всегда синхронный. Асинхронных D-триггеров не существует. Принцип работы D-триггера заключается в том, что при поступлении синхросигнала в триггер записывается значение, которое в этот момент установлено на информационном входе D. В другое время (при отсутствии синхросигнала) изменение значений на входе D никакого воздействия на состояние триггера не оказывает. Т-триггер. Т — триггер называют счетным триггером, или как его еще называют — счетчиком до двух, или делителем на 2 — так как он делит входную частоту на 2. T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.

Выводы T-триггеры широко применяются в схемах деления и умножения частоты. Без них было бы невозможна реализация синтезаторов частот, которые применяются в качестве задающих генераторов в передатчиках и гетеродинов в приемниках раций, мобильных телефонов или GSM навигаторов. Не менее важна роль T-триггеров в формировании тактовой частоты цифровых микросхем, таких как центральные процессоры компьютеров, планшетов или цифровых фотоаппаратов. Самое распространенное применение Т-триггера — делитель частоты на 2. Для использования его в таком качестве на вход Т подают лог. 1, а на вход С подают исходную частоту. С выхода Q снимаю частоту в два раза меньше. 18. Синхронный триггер. Понятие о синхронизации Триггеры в цифровой электронике занимают особое место. Триггеры – это электронные устройства с несколькими устойчивыми состояниями и способные скачкообразно изменять свое состояние при изменении управляющих сигналов. На основе триггеров строятся многие другие цифровые элементы. Триггеры подразделяются на:

Асинхронные триггеры – это такие триггеры, которые изменяют свое состояние при изменении сигналов на управляющих входах. В отличии от асинхронных триггеров, синхронные триггеры изменяют свое состояние только после прихода синхросигнала, независимо от того, когда изменились сигналы на других управляющих входах. Триггеры, как правило, имеют два выхода — один прямой и один инверсный. Количество входов определяется типом триггера и выполняемой им функцией.

У синхронных триггеров смены сигналов на информационных входах еще недостаточно для срабатывания. Необходим дополнительный командный импульс, который подается на синхронизирующий, или, как его чаще называют, тактирующий вход. Синхронизирующие (тактирующие) сигналы вырабатываются специальным генератором тактовых импульсов, которые и задают частоту смены информации в дискретном времени t1, t2, …, tn-1, tn, tn+1. В эти моменты обновляется информация на выходах триггера, которая поступает на входы последующих устройств.

Синхронизация обеспечивает привязку ко времени и объединяет в общем ритме работу многих узлов аппаратуры, что позволяет во многих случаях ее существенно упростить.

Для асинхронного триггера тактом считается интервал времени между очередными сменами входных сигналов, причем длительность тактов не регламентируется. Асинхронные триггеры воспринимают непрерывный входной сигнал (1 или 0), независимо от его длительности, как один сигнал.

В случае синхронного триггера входной сигнал неизменного уровня, длящийся n тактов, обрабатывается как последовательность нескольких n отдельных сигналов одного знака. Например, код 11001, поступающий последовательно на вход синхронного триггера, за счет тактирования будет так и воспринят. Этот же код на входах асинхронного триггера будет воспринят как 101, так как без временной привязки последовательность логических 1 или 0 не отличить от одиночных логических 1 и 0.

Синхронные триггеры, сравнительно с асинхронными, обладают также более высокой помехоустойчивостью. Опрокидывание синхронных триггеров происходит только при участии тактовых импульсов, длительность которых намного меньше периода следования. В остальное время входные сигналы, равно как и помехи различного происхождения, на триггер не влияют. В случае же асинхронного управления опрокидывание может произойти в любой момент времени, будь то полезный сигнал на входе или помеха.

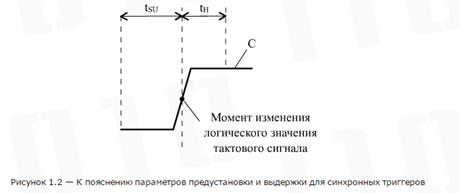

С синхронизацией (тактированием) триггера связаны два важных параметра — время предустановки tSU (Set-Up Time) и время выдержки tH (Hold Time). Важность этих параметров обуславливается еще и тем, что они свойственны не только триггерам, но и другим устройствам. Время tSU — это интервал до поступления синхросигнала, в течение которого информационный сигнал должен оставаться неизменным (Рисунок 1.2). Время выдержки tH — это время после поступления синхросигнала, в течение которого информационный сигнал должен оставаться неизменным. Соблюдение времен предустановки и выдержки обеспечивает правильное восприятие триггером входной информации.

19. Узлы ЭВМ. Регистры. Счетчики. Сумматоры. Шифраторы и дешифраторы. Мультиплексоры. АЛУ. Элемент ЭВМ – наименьшая конструктивная и функциональная часть ЭВМ, которая используется при ее логическом проектировании и технологической реализации. По назначению они различаются на логические, запоминающие и вспомогательные. Логические элементы реализуют логические операции и применяются как для построения сложных логических схем (узлов), так и для управления работой отдельных блоков и устройств ЭВМ. Запоминающие элементы предназначены для хранения и выдачи двоичной информации. Вспомогательные элементы используются чаще всего для энергетического обеспечения и согласования работы различных блоков ЭВМ. Регистры Регистр хранения – внутреннее запоминающее устройство процессора или внешнего устройства, предназначенное для временного хранения обрабатываемой или управляющей информации. Регистры представляют собой совокупность триггеров, количество которых равняется разрядности регистра, и вспомогательных схем, обеспечивающих выполнение некоторых элементарных операций. Набор этих операций, в зависимости от функционального назначения регистра, может включать в себя · одновременную установку всех разрядов регистра в " 0 ", · параллельную или последовательную загрузку регистра, · сдвиг содержимого регистра влево или вправо на требуемое число разрядов, · управляемую выдачу информации из регистра (обычно используется при работе нескольких схем на общую шину данных) и т.д. Регистры хранения используются для приема, хранения и выдачи многоразрядного кода. Они представляют собой совокупность одноступенчатых триггеров (как правило, D -типа) с общим входом синхронизации. Иногда в регистре имеется также и общий вход асинхронной установки всех триггеров в " 0 ".

Регистр сдвига Регистр сдвига – регистр, обеспечивающий помимо хранения информации, сдвиг влево или вправо всех разрядов одновременно на одинаковое число позиций. При этом выдвигаемые за пределы регистра разряды теряются, а в освобождающиеся разряды заносится информация, поступающая по отдельному внешнему входу регистра сдвига. Обычно эти регистры обеспечивают сдвиг кода на одну позицию влево или вправо. Но существуют и универсальные регистры сдвига, которые выполняют сдвиг как влево, так и вправо в зависимости от значения сигнала на специальном управляющем входе или при подаче синхросигналов на разные входы регистра. Регистр сдвига может быть спроектирован и таким образом, чтобы выполнять сдвиг одновременно не на одну, а на несколько позиций. Регистры сдвига строятся на двухступенчатых триггерах. Счетчики Счетчиком называется электронная схема, предназначенная для подсчета числа сигналов, поступающих на его счетный вход. Счетчики используются в устройстве управления компьютера при построении · распределителей импульсов и · организации циклов, · в счетчиках команд для формирования адреса выполняемой команды при естественном порядке выполнения и · в некоторых других устройствах ЭВМ. · Также счетчики широко применяются в качестве самостоятельных узлов в различных системах цифровой автоматики. Суть работы счетчика заключается в изменении на единицу зафиксированного в нем значения с приходом каждого счетного сигнала. Счетчики принято подразделять на суммирующие, вычитающие и реверсивные. Суммирующие счетчики увеличивают свое значение, вычитающие – уменьшают, а реверсивные могут работать как на прибавление, так и на вычитание в зависимости от сигналов управления. Параметром, определяющим информационную емкость счетчика, является модуль пересчета, равный числу внутренних состояний. Это значение проставляется на УГО после аббревиатуры CT. Пример асинхронного трехразрядного двоичного суммирующего счетчика приведен на рис. 2.1, а его условно-графическое обозначение – на рис. 2.2. Для построения этого счетчика использованы JK-триггеры с динамической синхронизацией по спаду синхросигнала. Каждый JK-триггер в счетчике включен в режим инвертирования своего состояния при переключении синхросигнала с высокого уровня на низкий (см. табл. 1.5). Идеализированная временная диаграмма работы этого счетчика показана на рис. 2.3.

Обычно счетчик имеет вход установки в нулевое состояние (асинхронный сброс составляющих его триггеров в " 0 "). Некоторые счетчики имеют цепи установки в произвольное начальное состояние, с которого уже будет начинаться операция счета. Сумматор Сумматор - это узел, в котором выполняется арифметическая операция суммирования цифровых кодов двух двоичных чисел.

Используя одноразрядные сумматоры можно построить многоразрядные сумматоры. Шифраторы и дешифраторы Дешифратором называется комбинационная схема, имеющая n входов и 2n выходов и преобразующая двоичный код на своих входах в унитарный код на выходах. Унитарным называется двоичный код, содержащий одну и только одну единицу, например 00100000. Условно-графическое обозначение дешифратора на три входа приведено на рис. 1.1.

Номер разряда, в котором устанавливается " 1 " на выходе дешифратора, определяется кодом на его входах. Ниже приведена таблица истинности трехвходового дешифратора (таблица 1.1). Шифратор Шифратор – схема, имеющая 2n входов и n выходов, функции которой во многом противоположны функции дешифратора (рис. 1.4). Эта комбинационная схема в соответствии с унитарным кодом на своих входах формирует позиционный код на выходе (таблица 1.2).

Мультиплексоры Мультиплексоры - это узлы, преобразующие параллельные цифровые коды в последовательные. В этом устройстве выход соединяется с одним из входов в зависимости от значения адресных входов. Мультиплексоры широко используются для синтеза комбинационных устройств, так как это способствует значительному уменьшению числа используемых микросхем.

Демультиплексоры - это узлы, преобразующие информацию из последовательной формы в параллельную. Информационный вход D подключается к одному из выходов Qi определяемый адресными сигналами A0 и A1.

|

||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 544; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.119.133.214 (0.009 с.) |