Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Информационная система. Информация. История развития компьютераСтр 1 из 11Следующая ⇒

Информационная система. Информация. История развития компьютера Информационная систем а - система, предназначенная для сбора, передачи, обработки, хранения и выдачи информации потребителям и состоящая из следующих основных компонентов: • программное обеспечение, • информационное обеспечение, • технические средства, • обслуживающий персонал. Информация наряду с материей и энергией является первичным понятием нашего мира и поэтому в строгом смысле не может быть определена. Можно лишь перечислить ее основные свойства, например: 1) информация приносит сведения, об окружающем мире, которых в рассматриваемой точке не было до ее получения; 2) информация не материальна, но она проявляется в форме материальных носителей дискретных знаков или первичных сигналах; 3) знаки и первичные сигналы несут информацию только для получателя, способного ее распознать. Информация – мера разрешения неопределенности. · 1 бит (1 bit, binary digit) -Разрешает неопределенность при выборе одного из двух возможных вариантов (минимальную неопределенность). · 1 байт (1 byte) = 8 bit -Разрешает неопределенность при выборе одного из 28 = 256 вариантов История компьютера 1000 – 500 до н.э. изобретен абак 1500 - Леонардо да Винчи Механический калькулятор 1642 - Блез Паскаль «Паскалина» 1822 Чарльз Бэббидж - Дифференциальная машина 1830 Чарльз Бэббидж - Аналитическая машина 1847-54 Джордж Буль - Булева алгебра 1930-е – 1940-е годы

Первый транзистор Первый действующий транзистор создали в 1947 году американские физики Уильям Шокли, Джон Бардин и Уолтер Браттейн в лабораториях Bell Labs.

Первая микросхема Первая микросхема была изготовлена в компании Texas Instruments под руководством Джека Килби (JackKilby) в 1958 году (Нобелевская премия 2000 г.). Независимо от Килби приблизительно в то же время Роберт Нойс (RobertNoyce) в основанной им вместе c Гордоном Муром (GordonMoore) и еще шестью коллегами компанииFairchildSemiconductorобъединил полупроводниковые элементы на едином кристалле кремния.

Первый микропроцессор Первый микропроцессор выпущен в 1971 году фирмой Intel Corp. Это был Intel 4004. Микросхема включала в себя 2250 транзисторов и имела тактовую частоту около 100 кГц.В серию 4xxxвходили и другие м/с (4001, 4002 и др.).

Мэйнфреймы Мэйнфрейм - большой универсальный компьютер. Доминировали системы фирмы IBM. IBMSystem/360 IBMSystem/370

Суперкомпьютеры Суперкомпьютер – универсальный компьютер большой вычислительной мощности. Сегодня это обычно многопроцессорные системы или компьютерные кластеры. Cray-1 (133MFLOPS), также -2, -3, -4 Сайт «Топ-500» ( www.top500.org ): Nebulae, Fermi, Sequoia, Tianhe, Jaguar, …

Первые ПК

Apple& IBM Apple I выпущен в 1976 году. Процессор 6502 (MOS Technology). Apple II – 1977 год. IBM PC – 1981 год. Процессор 8088 ( Intel ). IBM PC/XT – 1983 год.

2. Позиционные системы счисления. Перевод чисел из одной системы счисления в другую. Система счисления – это совокупность правил для обозначения и наименования чисел. Непозиционной называется такая система счисления, в которой количественный эквивалент каждой цифры не зависит от ее положения (места, позиции) в записи числа. Система счисления называется позиционной, если значение цифры зависит от ее места (позиции) в записи числа. Основанием системы счисления называется количество знаков или символов, используемых для изображения числа в данной системе счисления. Наименование системы счисления соответствует ее основанию (например, десятичной называется система счисления так потому, что ее основание равно 10, т.е. используется десять цифр).

Преимущества · Упрощён вывод чисел на индикацию — вместо последовательного деления на 10 требуется просто вывести на индикацию каждый полубайт. Аналогично, проще ввод данных с цифровой клавиатуры. · Для дробных чисел (как с фиксированной, так и с плавающей запятой) при переводе в человекочитаемый десятичный формат и наоборот не теряется точность. · Упрощены умножение и деление на 10, а также округление. По этим причинам двоично-десятичный формат применяется в калькуляторах — калькулятор в простейших арифметических операциях должен выводить в точности такой же результат, какой подсчитает человек на бумаге.

Недостатки · Требует больше памяти. · Усложнены арифметические операции. Так как в 8421-BCD используются только 10 возможных комбинаций 4-х битового поля вместо 16, существуют запрещённые комбинации битов: 1010(1010), 1011(1110), 1100(1210), 1101(1310), 1110(1410) и 1111(1510).

Представление текстовой информации. ASCII В современных ЭВМ, в зависимости от типа операционной системы и конкретных прикладных программ, используются 8-разрядные и 16-разрядные (Windows 95, 98, NT) коды символов. Использование 8-разрядных кодов позволяет закодировать 256 различных знаков, этого вполне достаточно для представления многих символов, используемых на практике. При такой кодировке для кода символа достаточно выделить в памяти один байт. Так и делают: каждый символ представляют своим кодом, который записывают в один байт памяти. В персональных компьютерах обычно используется система кодировки ASCII (American Standard Code for Information Interchange - американский стандартный код для обмена информации). Он введен в 1963 г. и ставит в соответствие каждому символу семиразрядный двоичный код. Легко определить, что в коде ASCII можно представить 128 символов. В системе ASCII закреплены две таблицы кодирования базовая и расширенная. Базовая таблица закрепляет значения кодов от 0 до 127, а расширенная относится к символам с номерами от 128 до 255. Первые 32 кода базовой таблицы, начиная с нулевого, отданы производителям аппаратных средств. В этой области размещаются управляющие коды, которым не соответствуют ни какие символы языков. Начиная с 32 по 127 код размещены коды символов английского алфавита, знаков препинания, арифметических действий и некоторых вспомогательных символов. Кодировка символов русского языка, известная как кодировка Windows-1251, была введена "извне" - компанией Microsoft, но, учитывая широкое распространение операционных систем и других продуктов этой компании в России, она глубоко закрепилась и нашла широкое распространение. Универсальная система кодирования текстовых данных. Если проанализировать организационные трудности, связанные с созданием единой системы кодирования текстовых данных, то можно прийти к выводу, что они вызваны ограниченным набором кодов (256). В то же время, очевидно, что если, кодировать символы не восьмиразрядными двоичными числами, а числами с большим разрядом то и диапазон возможных значений кодов станет на много больше. Такая система, основанная на 16-разрядном кодировании символов, получила название универсальной - UNICODE. Шестнадцать разрядов позволяют обеспечить уникальные коды для 65 536 различных символов - этого поля вполне достаточно для размещения в одной таблице символов большинства языков планеты. 11. Алгебра логики. Переменные и константы алгебры логики Алгебра логики рассматривает высказывания и их взаимосвязь только с точки зрения их истинности либо ложности. Если x – это высказывание, то в алгебре логики Два элемента булевой алгебры, а именно событие истинно и событие ложно, называются ее константами. Будем понимать под ними значения соответственно лог. 1 и лог. 0.

Для упрощения записей значения «Ложь» и «Истина» обозначают нулем и единицей (0 и 1). Логические переменные могут принимать только эти два значения. Примеры: x = 0, x1 = 0, x2 = 1, y = 0, Alpha = 1 Переменные – как обычные переменные. А вообще, булева алгебра оперирует ансамблями, где каждая из переменных либо 1 либо 0. Любое значение может быть представлено при помощи ансамбля. 12. Законы и аксиомы алгебры логики. Логические функции Аксиомы алгебры логики:

Законы алгебры логики: Законы рефлексивности a ∨ a = a a ∧ a = a Законы коммутативности a ∨ b = b ∨ a a ∧ b = b ∧ a Законы ассоциативности (a ∧ b) ∧ c = a ∧ (b ∧ c) (a ∨ b) ∨ c = a ∨ (b ∨ c) Законы дистрибутивности a ∧ (b ∨ c) = (a ∧ b) ∨ (a ∧ c) a ∨ (b ∧ c) = (a ∨ b) ∧ (a ∨ c) Закон отрицания отрицания (a) = a Законы де Моргана (a ∧ b) = a ∨ b (a ∨ b) = a ∧ b Законы поглощения a ∨ (a ∧ b) = a a ∧ (a ∨ b) = a

Независимые высказывания называют аргументами. Высказывания, истинность либо ложность которых зависит от истинности либо ложности других высказываний, называют логическими функциями, зависящими от своих аргументов: y = f(x), y = f(x1, x2, x3) и т.п. ИЛИ-НЕ Функция ИЛИ-НЕ – это функция двух или более аргументов (другие названия: функция Вебба, стрелка Пирса, NOR). Значения Данная функция является инверсией функции ИЛИ

14. Формы представления ЛФ. Таблица истинности. СДНФ и СКНФ. Переход от одной формы к другой. Отрицание, НЕ RS-триггер

Это Reset Set триггер (RS триггер) Входной сигнал S (Set) служит для установки ЗЯ в состояние " 1" (Q=1, Q=0). Сигнал R (Reset) устанавливает ЗЯ в состояние " 0 " (Q=0, Q=1). Активными значениями для них являются сигналы низкого уровня. Пусть на входы ЗЯ поданы сигналы: S=0, R=1. Тогда при любом исходном состоянии ЗЯ на выходе элемента 1 установится высокий уровень напряжения. Так как на входы элемента 2 поступают значения Q и R, то на его выходе будет сигнал низкого уровня. Таким образом, ЗЯ перейдет в состояние " 1 ". Аналогично при S=1, R=0 запоминающая ячейка перейдет в состояние Q=0, Q=1, то есть в " 0 ". Если S=1, R=1, то состояние ЗЯ будет определяться ее предыдущим состоянием. Если ЗЯ находилась в состоянии " 1 ", то сигнал Q=0, поступая на вход элемента 1, подтвердит состояние его выхода Q=1. На входы элемента 2 поступят сигналы только высокого уровня. Поэтому его выход будет находиться в состоянии Q=0, то есть не изменится. Если ЗЯ находилась в состоянии " 0 ", то сигнал Q=0, поступая на вход элемента 2, подтвердит состояние его выхода Q=1. В свою очередь, выход элемента 1 также останется без изменения. Таким образом, эта комбинация входных сигналов соответствует режиму хранения.

Если на входы S и R поданы сигналы низкого уровня (S = R = 0), то сигнал на выходах элементов 1 и 2 будет высоким (Q = Q = 1). При переводе ЗЯ в режим хранения (S = R = 1), выходы элементов 1 и 2 могут установиться в произвольное состояние. Поэтому комбинация сигналов S = R = 0 на управляющих входах не используется. Работа триггерной схемы определяется не таблицей истинности, как для комбинационной логической схемы, а таблицей переходов. Таблица переходов показывает изменение состояния триггера при изменении состояния входных сигналов в зависимости от его текущего состояния. Таблица переходов запоминающей ячейки, показанной на рис. 1.5, представлена в табл. 1.3.

D-триггер (защелка):

D-триггер, также как и другие типы триггеров имеют два устойчивых состояния. D-триггеры имеет в своем составе два входа: информационный — D и вход синхронизации C, т.е. D-триггер всегда синхронный. Асинхронных D-триггеров не существует. Принцип работы D-триггера заключается в том, что при поступлении синхросигнала в триггер записывается значение, которое в этот момент установлено на информационном входе D. В другое время (при отсутствии синхросигнала) изменение значений на входе D никакого воздействия на состояние триггера не оказывает. Т-триггер. Т — триггер называют счетным триггером, или как его еще называют — счетчиком до двух, или делителем на 2 — так как он делит входную частоту на 2. T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.

Выводы T-триггеры широко применяются в схемах деления и умножения частоты. Без них было бы невозможна реализация синтезаторов частот, которые применяются в качестве задающих генераторов в передатчиках и гетеродинов в приемниках раций, мобильных телефонов или GSM навигаторов. Не менее важна роль T-триггеров в формировании тактовой частоты цифровых микросхем, таких как центральные процессоры компьютеров, планшетов или цифровых фотоаппаратов. Самое распространенное применение Т-триггера — делитель частоты на 2. Для использования его в таком качестве на вход Т подают лог. 1, а на вход С подают исходную частоту. С выхода Q снимаю частоту в два раза меньше. 18. Синхронный триггер. Понятие о синхронизации Триггеры в цифровой электронике занимают особое место. Триггеры – это электронные устройства с несколькими устойчивыми состояниями и способные скачкообразно изменять свое состояние при изменении управляющих сигналов. На основе триггеров строятся многие другие цифровые элементы.

Триггеры подразделяются на:

Асинхронные триггеры – это такие триггеры, которые изменяют свое состояние при изменении сигналов на управляющих входах. В отличии от асинхронных триггеров, синхронные триггеры изменяют свое состояние только после прихода синхросигнала, независимо от того, когда изменились сигналы на других управляющих входах. Триггеры, как правило, имеют два выхода — один прямой и один инверсный. Количество входов определяется типом триггера и выполняемой им функцией.

У синхронных триггеров смены сигналов на информационных входах еще недостаточно для срабатывания. Необходим дополнительный командный импульс, который подается на синхронизирующий, или, как его чаще называют, тактирующий вход. Синхронизирующие (тактирующие) сигналы вырабатываются специальным генератором тактовых импульсов, которые и задают частоту смены информации в дискретном времени t1, t2, …, tn-1, tn, tn+1. В эти моменты обновляется информация на выходах триггера, которая поступает на входы последующих устройств.

Синхронизация обеспечивает привязку ко времени и объединяет в общем ритме работу многих узлов аппаратуры, что позволяет во многих случаях ее существенно упростить.

Для асинхронного триггера тактом считается интервал времени между очередными сменами входных сигналов, причем длительность тактов не регламентируется. Асинхронные триггеры воспринимают непрерывный входной сигнал (1 или 0), независимо от его длительности, как один сигнал.

В случае синхронного триггера входной сигнал неизменного уровня, длящийся n тактов, обрабатывается как последовательность нескольких n отдельных сигналов одного знака. Например, код 11001, поступающий последовательно на вход синхронного триггера, за счет тактирования будет так и воспринят. Этот же код на входах асинхронного триггера будет воспринят как 101, так как без временной привязки последовательность логических 1 или 0 не отличить от одиночных логических 1 и 0.

Синхронные триггеры, сравнительно с асинхронными, обладают также более высокой помехоустойчивостью. Опрокидывание синхронных триггеров происходит только при участии тактовых импульсов, длительность которых намного меньше периода следования. В остальное время входные сигналы, равно как и помехи различного происхождения, на триггер не влияют. В случае же асинхронного управления опрокидывание может произойти в любой момент времени, будь то полезный сигнал на входе или помеха.

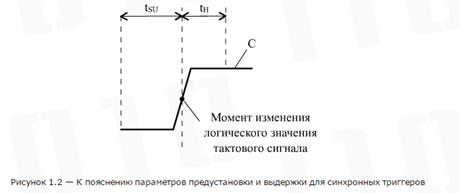

С синхронизацией (тактированием) триггера связаны два важных параметра — время предустановки tSU (Set-Up Time) и время выдержки tH (Hold Time). Важность этих параметров обуславливается еще и тем, что они свойственны не только триггерам, но и другим устройствам. Время tSU — это интервал до поступления синхросигнала, в течение которого информационный сигнал должен оставаться неизменным (Рисунок 1.2). Время выдержки tH — это время после поступления синхросигнала, в течение которого информационный сигнал должен оставаться неизменным. Соблюдение времен предустановки и выдержки обеспечивает правильное восприятие триггером входной информации.

19. Узлы ЭВМ. Регистры. Счетчики. Сумматоры. Шифраторы и дешифраторы. Мультиплексоры. АЛУ. Элемент ЭВМ – наименьшая конструктивная и функциональная часть ЭВМ, которая используется при ее логическом проектировании и технологической реализации. По назначению они различаются на логические, запоминающие и вспомогательные. Логические элементы реализуют логические операции и применяются как для построения сложных логических схем (узлов), так и для управления работой отдельных блоков и устройств ЭВМ. Запоминающие элементы предназначены для хранения и выдачи двоичной информации. Вспомогательные элементы используются чаще всего для энергетического обеспечения и согласования работы различных блоков ЭВМ. Регистры Регистр хранения – внутреннее запоминающее устройство процессора или внешнего устройства, предназначенное для временного хранения обрабатываемой или управляющей информации. Регистры представляют собой совокупность триггеров, количество которых равняется разрядности регистра, и вспомогательных схем, обеспечивающих выполнение некоторых элементарных операций. Набор этих операций, в зависимости от функционального назначения регистра, может включать в себя · одновременную установку всех разрядов регистра в " 0 ", · параллельную или последовательную загрузку регистра, · сдвиг содержимого регистра влево или вправо на требуемое число разрядов, · управляемую выдачу информации из регистра (обычно используется при работе нескольких схем на общую шину данных) и т.д. Регистры хранения используются для приема, хранения и выдачи многоразрядного кода. Они представляют собой совокупность одноступенчатых триггеров (как правило, D -типа) с общим входом синхронизации. Иногда в регистре имеется также и общий вход асинхронной установки всех триггеров в " 0 ".

Регистр сдвига Регистр сдвига – регистр, обеспечивающий помимо хранения информации, сдвиг влево или вправо всех разрядов одновременно на одинаковое число позиций. При этом выдвигаемые за пределы регистра разряды теряются, а в освобождающиеся разряды заносится информация, поступающая по отдельному внешнему входу регистра сдвига. Обычно эти регистры обеспечивают сдвиг кода на одну позицию влево или вправо. Но существуют и универсальные регистры сдвига, которые выполняют сдвиг как влево, так и вправо в зависимости от значения сигнала на специальном управляющем входе или при подаче синхросигналов на разные входы регистра. Регистр сдвига может быть спроектирован и таким образом, чтобы выполнять сдвиг одновременно не на одну, а на несколько позиций. Регистры сдвига строятся на двухступенчатых триггерах. Счетчики Счетчиком называется электронная схема, предназначенная для подсчета числа сигналов, поступающих на его счетный вход. Счетчики используются в устройстве управления компьютера при построении · распределителей импульсов и · организации циклов, · в счетчиках команд для формирования адреса выполняемой команды при естественном порядке выполнения и · в некоторых других устройствах ЭВМ. · Также счетчики широко применяются в качестве самостоятельных узлов в различных системах цифровой автоматики. Суть работы счетчика заключается в изменении на единицу зафиксированного в нем значения с приходом каждого счетного сигнала. Счетчики принято подразделять на суммирующие, вычитающие и реверсивные. Суммирующие счетчики увеличивают свое значение, вычитающие – уменьшают, а реверсивные могут работать как на прибавление, так и на вычитание в зависимости от сигналов управления. Параметром, определяющим информационную емкость счетчика, является модуль пересчета, равный числу внутренних состояний. Это значение проставляется на УГО после аббревиатуры CT. Пример асинхронного трехразрядного двоичного суммирующего счетчика приведен на рис. 2.1, а его условно-графическое обозначение – на рис. 2.2. Для построения этого счетчика использованы JK-триггеры с динамической синхронизацией по спаду синхросигнала. Каждый JK-триггер в счетчике включен в режим инвертирования своего состояния при переключении синхросигнала с высокого уровня на низкий (см. табл. 1.5). Идеализированная временная диаграмма работы этого счетчика показана на рис. 2.3.

Обычно счетчик имеет вход установки в нулевое состояние (асинхронный сброс составляющих его триггеров в " 0 "). Некоторые счетчики имеют цепи установки в произвольное начальное состояние, с которого уже будет начинаться операция счета. Сумматор Сумматор - это узел, в котором выполняется арифметическая операция суммирования цифровых кодов двух двоичных чисел.

Используя одноразрядные сумматоры можно построить многоразрядные сумматоры. Шифраторы и дешифраторы Дешифратором называется комбинационная схема, имеющая n входов и 2n выходов и преобразующая двоичный код на своих входах в унитарный код на выходах. Унитарным называется двоичный код, содержащий одну и только одну единицу, например 00100000. Условно-графическое обозначение дешифратора на три входа приведено на рис. 1.1.

Номер разряда, в котором устанавливается " 1 " на выходе дешифратора, определяется кодом на его входах. Ниже приведена таблица истинности трехвходового дешифратора (таблица 1.1). Шифратор Шифратор – схема, имеющая 2n входов и n выходов, функции которой во многом противоположны функции дешифратора (рис. 1.4). Эта комбинационная схема в соответствии с унитарным кодом на своих входах формирует позиционный код на выходе (таблица 1.2).

Мультиплексоры Мультиплексоры - это узлы, преобразующие параллельные цифровые коды в последовательные. В этом устройстве выход соединяется с одним из входов в зависимости от значения адресных входов. Мультиплексоры широко используются для синтеза комбинационных устройств, так как это способствует значительному уменьшению числа используемых микросхем.

Демультиплексоры - это узлы, преобразующие информацию из последовательной формы в параллельную. Информационный вход D подключается к одному из выходов Qi определяемый адресными сигналами A0 и A1.

РОН Есть 8 32-разрядных РОН.

· Первые 4 РОН: А, B, C, D – для хранения операндов команд (арифметических, логических и всяких прочих) · Последние 4 – ESI, EDI, EBP, ESP – для задания смещения внутри сегмента данных. Используются совместно с регистрами сегментов (см дальше) для задания виртуального адреса. (Регистры для работы со стеком и для задания адресов)

К первым 4 регистрам можно обращаться: · Целиком (EAX, EBX, ECX, EDX) · К младшему их байту (AL, BL, CL, DL); · Ко второму по старшинству байту (AH, BH, CH, DH); · К двум младшим байтам (AX, BX, CX, DX);

Рассмотрим регистры по одному: 1) АХ – регистр-сумматор. Применяется для накапливания результатов вычислений, часто выступает в роли приемника различных команд. Результаты исполнения некоторых команд (умножения, например), направляются сюда автоматом. 2) ВХ – базовый регистр. Очень похож на первый, но, в отличие от него, может содержать указатель на область памяти, где лежит операнд. MOV AX, (BX) 3) СХ – регистр счетчик. Применяется для хранения показателей счетчиков при выполнении циклов. 4) DX – регистр данных. Совместно с АХ задействуется в исполнении команд с 32-разрядными словами. Здесь сохраняются старшие 16 бит, а в АХ – младшие. 5) SP – указатель стека – указывает на вершину стека. 6) BP – указатель базы – может указывать на любое место в стеке (обычно указывает на начало стекового кадра текущей процедуры – упрощается задача поиска ее локальных переменных) SI – индекс источника 8) DI – индекс приемника. Они совместно с BP употребляются для адресации данных в стеке, а с BХ – для вычисления адресов. Применяются для работы со строками (содержат текущий адрес элемента в строке-источнике или приемнике) Ввод-вывод по прерываниям Ввод-вывод по прерываниям подразумевает, что действия по обмену информацией инициируют сами периферийные устройства, генерируя сигнал прерывания. При восприятии сигнала прерывания микропроцессор приостанавливает выполнение текущей программы, временно запоминае т ее состояние (как минимум, запоминается содержание PSW, РС) идентифицирует прерывающее устройство и осуществляет обмен информацией. После завершения обмена восстанавливается состояние прерванной программы и возобновляется ее выполнение (рис. 17). В данном режиме на ввод-вывод расходуется гораздо меньше времени микропроцессора, чем в программно-управляемом ВВ, поэтому система может выполнить больше полезной работы или обслужить больше периферийных устройств.

Для повышения производительности системы необходимо освободить процессор от опроса готовности ВУ к обмену. Эту функцию берет на себя контроллер прерываний ВУ. Получив команду ввода-вывода, контроллер передает ее ВУ и следит за временем ее выполнения. По окончании действий в ВУ (печати, перфорации и т. п.) контроллер посылает в процессор сигнал требования прерывания, получает очередную команду ввода-вывода, и действия повторяются. Процессор в этом случае, передав в контроллер очередную команду ввода-вывода, может выполнять другие операции основной программы до получения сигнала требования прерывания. Получив его, он обслуживает это прерывание, то есть формирует и выдает в контроллер очередную команду ввода-вывода, а затем возвращается к выполнению прерванной основной программы.

Ввод-вывод по прерываниям, однако, требует усложнения аппаратных средств – создания системы прерываний. Структура таблицы векторов прерываний для ип от Intel имеет вид

Обращение к элементам таблицы осуществляется по 8-разрядному коду - типу прерывания

На уровне электроники внешние прерывания организованы следующим образом. Имеется контроллер прерываний (микросхема i8259А), выполняющий несколько важных функций: · получение сигналов на прерывания от внешних устройств, · маскировка (т. е. запрещение обработки) некоторых прерываний, · арбитраж приоритетов прерываний и · формирование очереди запросов на прерывание. Контроллер имеет три 8-разрядных регистра и 8 входов от внешних устройств, называемых IRQ0, IRQ1,...IRQ7 (Interrupt ReQuest), выход INT на процессор (соединяемый со входом процессора INTR) и вход обратной связи от процессора INTA, по которому процессор подтверждает начало обработки прерывания. Запрос на прерывание, поступающий на некоторый вход IRQ, устанавливает в 1 соответствующий бит 8-разрядного регистра фиксации запросов прерываний (IRR). Если соответствующее прерывание не замаскировано 8-разрядным регистром маски (IMR может программироваться) и если процессор не занят обработкой прерывания высшего или равного приоритета (что определяется 8-разрядным регистром ISR), запрос на прерывание поступает с выхода INT на вход прерываний процессора INTR, и процессор подтверждает по линии INTA. Один контроллер прерываний имеет 8 входов (IRQ), чего явно недостаточно для обслуживания внешних устройств современного компьютера (таймер, часы реального времени, клавиатура, гибкий и жесткий диски, мышь, последовательные и параллельные порты и проч.). Однако несколько контроллеров прерываний могут быть включены последовательно. На современных компьютерах (начиная с 286) один (ведущий) контроллер прерываний подключен непосредственно к процессору, а второй (ведомый) своим выходом INT подключен ко входу IRQ2 ведущего контроллера. Итого получается 15 входов прерываний от IRQ0 до IRQ 15 (IRQ2 не может быть использован). При подаче сигнала на прерывание от контроллера к процессору по линии INTR-INT, одновременно по линиям данных из контроллера прерываний в процессор поступает номер вектора прерывания, который образуется путем сложения IRQ с некоторым базовым номером, который присваивается ВIOSом контроллеру в процессе загрузки (значения по умолчанию 08h для ведущего контроллера и 70h для ведомого). Таким образом, например, номер вектора прерывания для клавиатуры будет 08+1=9 h, для жесткого диска 70 h +6=76 h. Контроллер прерываний допускает перепрограммирование для установки различных режимов формирования очереди запросов, изменения приоритетов прерываний, изменения базовых номеров контроллеров. Такое перепрограммирование осуществляется через два байтовых порта 20 h и 21 h. По умолчанию IRQ отдельного контроллера имеют приоритеты в соответствии с их номерами (IRQ0 – наивысший, IRQ7 – наинизший).

Структура контроллера приоритетных прерываний имеет вид

Пример каскадного включения двух контроллеров прямого доступа к памяти

Кэширование данных Чем быстрее память, тем она дороже. Но нам хотелось бы быструю и недорогую память. Для этого есть компромиссное решение – кэширование. Кэширование – это способ совместного функционирования двух типов запоминающих устройств, отличающихся временем доступа и стоимостью хранения данных. При кэшировании за счет копирования наиболее часто использующихся фрагментов информации из медленного ЗУ в быстрое достигается уменьшение времени доступа к данным, но при этом экономится быстродействующая память. При этом КЭШем называют не только способ организации памяти, но и само быстрое ЗУ, куда производится копирование информации. Более медленное ЗУ называют основной памятью. Кэширование – универсальный метод, пригодный для ускорения доступа к: - оперативной памяти – роль КЭШа выполняет быстрая память - к данным, хранящимся на диске – роль КЭШа выполняют буферы в оперативной памяти - к другим видам ЗУ. Виртуальная память по сути – тоже разновидность кэширования, где оперативная память выступает в роли КЭШа по отношению к диску. Правда здесь цель – не ускорение доступа, а увеличение объема и подмена оперативной памяти.

Вытеснение данных из КЭШа · Если данные не были изменены, то нужно просто сбросить бит действительности · Если данные были изменены, то нужно скопировать их в основную память 2) Если во время нахождения данных в КЭШе были изменены данные в основной памяти – копия в КЭШе становится недостоверной. Есть 2 варианта решения проблемы: · Сквозная запись – при каждой записи в основную память просматривается кэш. Если элемент найден в КЭШе, переписываются обе копии, если нет – только то, что в основной памяти · Обратная запись – при каждой записи в основную память просматривается кэш. Если элемент найден в КЭШе, переписывается только копия в КЭШе, если нет – то, что в основной памяти. В некоторых алгоритмах замещения предусмотрена первоочередная выгрузка модифицированных, грязных данных. Также модифицированные данные могут выгружаться не только, когда нужно освободить кэш, но и в фоновом режиме, когда ОС больше нечем заняться. Случайное отображение Элемент ОП может быть размещен в ЛЮБОМ месте КЭШа. Данные помещаются вместе в адресом в ОП, и поиск осуществляется по этому адресу. Схемы поиска: · Простой перебор (неэффективно) · Ассоциативный поиск (сравнение выполняется не последовательно с каждой записью КЭШа, а параллельно, сразу со всеми записями). Признак, по которому идет сравнение, называется ТЭГ. В данном случае – это адрес элемента в оперативной памяти.

|

|||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 276; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.189.2.122 (0.16 с.) |