Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Глава 3. Построение схем на логических элементахСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Основные логические функции и их реализация в Электронных устройствах Элемент ИЛИ.

Устройства ЧПУ, как любые цифровые устройства, включая ЭВМ, состоят из основных логических элементов и элементов памяти. К основным логическим элементам относятся физические элементы, реализующие логические функции «ИЛИ», «И», «НЕ», т. е. осуществляющие логические суммирование, умножение и отрицание. Элементы памяти также могут состоять из этих же логических элементов, соединенных в триггеры. Узлы цифровых устройств реализуются в виде серийно выпускаемых стандартных логических элементов, образующих их элементную базу, которая состоит из серии функционально различных логических элементов. Эти элементы конструктивно оформлены в одинаковых корпусах, содержащих несколько логических элементов, которые устанавливают на блоках, панелях или платах (в зависимости от конструкции этих элементов) и соединяют между собой внешним монтажом. Основным свойством логических элементов определенной серии является возможность их последовательного включения, в связи с чем предусмотрен одинаковый уровень их входных и выходных сигналов. Из основных логических элементов можно построить любую сколь угодно сложную схему, реализующую любую логическую функцию. Например, можно построить логические схемы со многими входами и выходами, служащие для преобразования кодов из одной формы в другую. Логические элементы (узлы) предназначены для, выполнения различных логических (функциональных) операций над дискретными сигналами при двоичном способе их представления. Преимущественное распространение получили логические элементы потенциального типа. В них используются дискретные сигналы, нулевому значению которых соответствует уровень низкого потенциала, а единичному значению — уровень высокого потенциала (отрицательного или положительного). Связь потенциального логического элемента с предыдущим и последующими узлами в системе осуществляется непосредственно, без применения реактивных компонентов. Благодаря этому преимуществу именно потенциальные логические элементы нашли почти исключительное применение в интегральном исполнении в виде микросхем. С позиций использования логических микросхем потенциального типа и проводится далее рассмотрение логических элементов. Логические биполярные микросхемы чаще выполняют на транзисторах типа n-p-n с напряжением питания Eti> 0. Этим объясняется, что используемые здесь сигналы имеют положительную полярность. Уровню высокого положительного потенциала («1») на выходе соответствует закрытое состояние транзистора, а уровню низкого потенциала («0») — его открытое состояние. С этой точки зрения, в частности, и следует понимать действие сигнала на входе логического элемента, имеющего непосредственную связь с другими элементами в конкретной схеме. Для упрощения уровень низкого потенциала сигнала полагаем равным нулю, а процесс перехода транзистора из одного состояния в другое — достаточно быстрым. Логические интегральные микросхемы являются элементами, на основе которых выполняются схемы цифровой техники, в частности, применяемые в устройствах систем ЧПУ. Логический элемент ИЛИ. Логический элемент ИЛИ имеет несколько входов и один общий выход. Его условное обозначение показано на рис.3.1, а. Логический элемент ИЛИ выполняет операцию логического сложения (дизъюнкции):

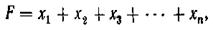

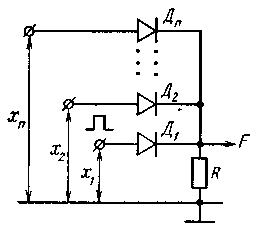

где F - функция; х1, х2, х3,..., хn — аргументы (переменные, двоичные сигналы на входах).

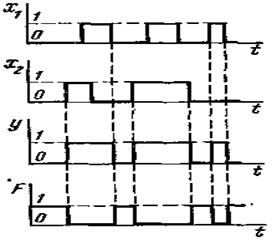

Рис.3.1. Условное обозначение логического элемента ИЛИ (а), его таблица истинности и временное диаграммы (б, в)

Наиболее просто элемент ИЛИ реализуется на диодах (рис.3.2). Значение F=1 на выходе создается передачей входного сигнала вследствие отпирания соответствующего диода. К диодам, для которых входной сигнал равен нулю, прикладывается обратное напряжение, и они находятся в закрытом состоянии.

Рис.3.2. Схема логического элемента ИЛИ на диодах

На практике возможны случаи, когда число входов используемого логического элемента ИЛИ превышает количество входных сигналов. Неиспользуемые входы заземляют. Тем самым исключается возможность прохождения помех через элемент ИЛИ от наводок по неиспользованным входам.

Элементы И, НЕ.

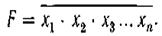

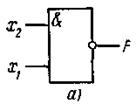

Логический элемент И. Логический элемент И также имеет несколько входов и один выход. Его условное обозначение показано на рис.3.3, а. Логический элемент И выполняет операцию логического умножения (конъюнкции):

Рис.3.3. Условное обозначение логического элемента И (а), его таблица истинности и временные диаграммы (б, в)

Здесь функция F=0, если один из ее аргументов равен нулю, и F=1 при всех аргументах, равных единице. Работу схемы двухвходового логического элемента И иллюстрируют таблица истинности и временные диаграммы, приведенные на рис.3.3,б,в. Элемент И является схемой совпадения: сигнал «1» на выходе появляется при совпадении сигналов «1» на всех входах. Моделью двухвходового элемента И может служить схема с двумя последовательно включенными ключами и источником питания. Простейшая схема элемента И на диодах приведена на рис.3.4. Отличие от схемы элемента ИЛИ (см. рис.3.2) заключается в изменении полярности включения диодов и наличии резистора R подключенного к шине «+» источника питания. Схема работает следующим образом. При всех входных сигналах, равных единице, на катодах диодов имеется положительный потенциал относительно общей точки и все диоды закрыты. На выходе схемы создается напряжение ER2/(R1+R2), определяющее F=1. При нулевом значении сигнала хотя бы на одном из входов соответствующий диод будет проводить ток и шунтировать резистор R2, выполняющий, как и резистор R в схеме рис.3.2, роль нагрузки. Напряжение на выходе при этом определяется падением напряжения на открытом диоде и близко к нулю (F=0). Увеличение числа входов с нулевым значением сигнала приводит только к увеличению числа проводящих диодов, а функция F остается равной нулю.

Рис.3.4. Схема логического элемента И на диодах

В случае применения логического элемента И, имеющего число входов, большее количества входных сигналов, неиспользуемые входы элемента соединяют с шиной «+» источника питания (подают сигнал логической «1»). Диоды неиспользуемых входов будут находиться в закрытом состоянии. Это уменьшает вероятность прохождения помех на выход элемента И от наводок по неиспользованным входам. Поведение логического элемента будет зависеть от комбинации входных сигналов. Логический элемент НЕ. Логический элемент НЕ имеет один вход и один выход. Его условное обозначение показано на рис.3.5,а. Элемент НЕ выполняет операцию инверсии (отрицания), в связи с чем его часто называют логическим инвертором. Сигналу х=0 на входе соответствует F=1 и, наоборот, при x=1 F=0. Работу схемы логического элемента НЕ иллюстрируют таблица истинности и временные диаграммы, приведенные на рис.3.5,б,в. Логический элемент НЕ представляет собой ключевую схему на транзисторе (рис.3.6). При х=0 (Uвх=0) транзистор закрыт, напряжение uкэ=Ек, т.е. F=1. При х=1 (Uвх=Uвхотп) транзистор открыт, напряжение F=0. Открытое состояние транзистора обеспечивается заданием тока базы, вводящего транзистор в режим насыщения.

Рис.3.5. Условное обозначение логического элемента НЕ (а), его таблица истинности и временные диаграммы (б, в)

Рис.3.6. Схема логического элемента НЕ

Элементы ИЛИ-НЕ, И-НЕ.

Логический элемент ИЛИ-НЕ. Условное обозначение логического элемента ИЛИ-НЕ показано на рис.3.7,а. Он объединяет элементы ИЛИ и НЕ с очередностью проведения операций, показанной в таблице истинности рис.3.7,б. В связи с этим входным сигналам, равным единице, соответствует логический «0» на выходе, а при нулевых сигналах на всех входах F=1. Функциональная операция, выполняемая элементом ИЛИ-НЕ при n входах, определяется выражением

На рис.3.8,а приведена схема логического элемента ИЛИ-НЕ, представляющая собой последовательное соединение элемента ИЛИ на диодах и элемента НЕ. Логические схемы подобного сочетания определяют, в частности, класс элементов так называемой диодно-транзисторной логики (ДТЛ). Принцип действия элемента ясен из диаграмм рис.3.8,б, где показаны сигналы x1 и х2 на входах, сигнал у на выходе элемента ИЛИ и выходная функция F.

а) б) Рис. 3.7. Условное обозначение логического элемента ИЛИ-НЕ (а), его таблица истинности (б)

а) б) Рис.3.8. Схема логического элемента ИЛИ-НЕ ДТЛ (а) и его временные диаграммы (б)

Логический элемент И-НЕ. Условное обозначение логического элемента И-НЕ показано на рис.3.9,а. Ему эквивалентна структурная схема, показанная на рис.3.9,б. Логической «1» на всех информационных входах соответствует логический «0» на выходе элемента. При логическом «0» на одном из входов создается логическая «1» на выходе. Для двухвходового элемента И-НЕ сказанное отражено в таблице истинности на рис.3.9,в. Логическая функция элемента И-НЕ при n входах отвечает выражению

Рис.3.9. Условное обозначение логического элемента И-НЕ (а),

Рис.3.10. Схема логического элемента И-НЕ ДТЛ (а) и его временные диаграммы (б)

При логическом «0» на одном из входов (например, x1) открывается диод этого входа (Д1). Образуется цепь, в которой ток резистора Rб (рис.3.10,а) протекает через открытый диод (Д1) и источник сигнала логического «0» (x1). При этом цепь Д' — Д" — эмиттерный переход транзистора — оказывается шунтированной цепью с проводящим диодом. Ток базы транзистора равен нулю, транзистор закрыт, F=1. Поскольку напряжение на открытом диоде входной цепи, а также напряжение входа логического «0» реально больше нуля, точка у на рис.3.10,а имеет некоторый положительный потенциал относительно эмиттера транзистора. В отсутствие диодов Д', Д" это могло бы привести к отпиранию транзистора. При их введении напряжение между точкой у и эмиттером транзистора будет приложено к диодам, а напряжение Uбэ транзистора близко к нулю. Наличие усилительного элемента, транзистора, в логических микросхемах ИЛИ-НЕ и И-НЕ классов ДТЛ и ТТЛ определяет такое их важное преимущество, как сохранение неизменного уровня напряжения, соответствующего логической «1», в процессе передачи сигнала при их последовательном соединении. В связи с этим указанные элементы, а также элемент НЕ являются базовыми в микросхемотехнике. В общем корпусе выпускаемых микросхем обычно содержится несколько элементов одного типа. Функцию И-НЕ называют функцией Шеффера (штрихом Шеффера) и обозначают в виде у=x1|x2, а функцию ИЛИ-НЕ — функцией Пирса (стрелкой Пирса) и обозначают в виде Логическое устройство, реализованное в базисе И-НЕ (ИЛИ-НЕ), имеет преимущества по сравнению с устройством, реализованным в базисе И, ИЛИ, НЕ: уменьшение номенклатуры элементов до одного типа, что упрощает компоновку устройства и его ремонт; наличие в каждом элементе инвертора (усилителя), который компенсирует затухание потенциалов при передаче их через коныонктор или дизъюнктор элемента. Благодаря этому не накапливается затухание сигнала при прохождении его через ряд последовательно включенных элементов, что могло бы вызвать снижение уровня U1 (лог. 1). Кроме того, инвертор увеличивает нагрузочную способность элемента: подключение допустимого числа других элементов к его выходу не вызывает заметного уменьшения на нем уровней потенциалов (что важно для U1), а наличие емкости на выходе не вызывает длительного переходного процесса при смене потенциалов.

Цифровые компараторы

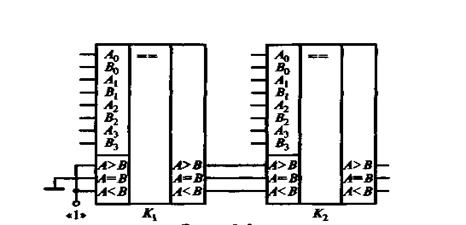

Цифровой компаратор предназначен для сравнения двух двоичных чисел (компарировать — сравнивать). Он имеет две группы входов. На одну из них поступают разряды первого числа А, на другую группу — разряды второго числа В. Появление лог.1 на одном из трех выходов компаратора фиксирует результат сравнения. На одном выходе она устанавливается при равенстве чисел (А=В), на другом — при А>В, на третьем — при А<В. Сравнение одноразрядных чисел на равенство может осуществлять элемент «Равнозначность», а на неравенство — элемент «Неравнозначность» (см. п.2.3.2). Для сравнения многоразрядных чисел они дополняются элементами других типов. Цифровой компаратор можно использовать, например, в системах автоматического контроля и регулирования. При этом число А является параметром некоторого процесса, а число В — порогом (уставкой), которого (в соответствии с условиями задачи) этот параметр не должен превосходить или опускаться ниже его. На рис.4.12 приведена классификация цифровых компараторов. Наряду с цифровыми существуют и аналоговые компараторы.

Рис.3.11. Классификация компараторов

Структура компаратора.

В табл.3.1 показана связь между сигналами на выходах и входах компаратора при сравнении одноразрядных чисел а и в, которые могут быть равны единице или нулю. На соответствующем выходе появляется лог.1, когда в должном соотношении находятся коды на входах. Так, если а=1, b=1 (числа одинаковы), то функция, характеризующая равенство чисел, Fa=b=1, а функции, характеризующие их неравенство, Fa>b=0 и Fa<b=0. Таблица 3.1 Связь между входными и выходными сигналами компаратора

Аналогично заполняются другие строки таблицы. По правилам алгебры логики из табл.3.1 можно записать следующие логические функции, характеризующие соотношения одноразрядных чисел:

Если значения а и b таковы, что правые части функций равны 1, то соотношения, указанные в индексах левых частей, выполняются. Если правые части функций равны 0, то соотношения между а и в противоположны указанным. Схема одноразрядного компаратора, реализующая приведенные функции, изображена на рис.3.12. На рис.3.13 приведены условное обозначение компараторов и способ наращивания их разрядности. Каждый из изображенных компараторов предназначен для сравнения двух 4-разрядных слов и имеет выходы А>В, А=В и А<В. Аналогичные входы служат для наращивания разрядности компараторов. Результат сравнения младших разрядов отражается на выходах компаратора К1: на одном из них появляется единица, на других присутствуют нули.

Рис.3.12. Схема одноразрядного компаратора

Компаратор К2 воспринимает этот результат как единую пару младших разрядов, с учетом которой формируется окончательный результат сравнения. Подобным образом можно осуществлять дальнейшее наращивание разрядности. Указанные потенциалы на входах компаратора К1 младших разрядов обеспечивают правильное функционирование многокаскадного компаратора на данных микросхемах.

Рис.3.13. Условное обозначение компараторов и способ наращивания их разрядности

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 3792; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 52.14.110.171 (0.009 с.) |

(3.1)

(3.1) Здесь функция F=0, когда все ее аргументы равны нулю, и F=1 при одном, нескольких или всех аргументах, равных единице. Работу схемы двухвходового логического элемента ИЛИ иллюстрируют таблица истинности и временные диаграммы, приведенные на рис.3.1,б, в. Моделью двухвходового элемента ИЛИ может служить схема с двумя параллельно включенными ключами. Если оба ключа выключены (аргументы равны нулю), то напряжение на выходе равно нулю и F=0. При одном или двух включенных ключах напряжение на выходе равно Е и F=1.

Здесь функция F=0, когда все ее аргументы равны нулю, и F=1 при одном, нескольких или всех аргументах, равных единице. Работу схемы двухвходового логического элемента ИЛИ иллюстрируют таблица истинности и временные диаграммы, приведенные на рис.3.1,б, в. Моделью двухвходового элемента ИЛИ может служить схема с двумя параллельно включенными ключами. Если оба ключа выключены (аргументы равны нулю), то напряжение на выходе равно нулю и F=0. При одном или двух включенных ключах напряжение на выходе равно Е и F=1.

(3.2)

(3.2)

(3.3)

(3.3)

(3.4)

(3.4) На рис.3.10,а приведена схема логического элемента И-НЕ ДТЛ. Принцип действия элемента иллюстрируют временные диаграммы рис.3.10,б. При логических «1» на обоих входах диоды Д1, Д2 закрыты. В схеме образуется цепь + ЕИ — RG — Д¢— Д², которая обеспечивает протекание тока базы EH/R6 транзистора. Транзистор открыт и насыщен, F=0.

На рис.3.10,а приведена схема логического элемента И-НЕ ДТЛ. Принцип действия элемента иллюстрируют временные диаграммы рис.3.10,б. При логических «1» на обоих входах диоды Д1, Д2 закрыты. В схеме образуется цепь + ЕИ — RG — Д¢— Д², которая обеспечивает протекание тока базы EH/R6 транзистора. Транзистор открыт и насыщен, F=0.

его функциональный эквивалент (б) и таблица истинности (в)

его функциональный эквивалент (б) и таблица истинности (в)

. Базис И-НЕ называют базисом Шеффера, а базис ИЛИ-НЕ — базисом Пирса.

. Базис И-НЕ называют базисом Шеффера, а базис ИЛИ-НЕ — базисом Пирса.

;

;  ;

;  .

.