Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Правила выполнения арифметических действий над двоичными числами.Содержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Сложение двоичных чисел в кодах.

При сложении двоичных чисел в кодах знаковые разряды участвуют в операции сложения на ровне с цифровыми, при этом если выполняется операция сложения в обратных кодах то единица переноса из знакового разряда сумматора прибавляется к её младшему разряду(т.е. выполняется циклический перенос) если же операция сложения выполняется над числами представленными в дополнительным коде то единица переноса из знакового разряда суммы отбрасывается. Переход от обратного и дополнительного кодов прямому выполняется аналогично переходу от прямого кода к обратно ому и дополнительно соответственно. При сложении двух чисел с одинаковыми знаковыми знаками возможно переполнение разрядной сетки, это приводит к существенному искажению результата. Способы обнаружения переполнения: 1) Переполнение отсутствует если имеет место перенос из знакового разряда и в знаковый, либо если они оба отсутствуют. 2) Использование модифицированных кодов: не совпадение знаковых разрядов модифицированного кода является признакам переполнения разрядной сетки: 01 или 10.

Тема 2.4 «методы минимизации логических ф-ий» 1)минимизация логических ф-ий. Метод последовательного исключения переменных. Минимальной формой представления ПФ называют такую форму которая не допускает больше никаких упрощений. Процесс упрощения ПФ с целью получения минимальной нормальной формы называют минимизациями. При минимизации исходят из требования минимальной затраты оборудования т.к каждой элементарной логической ф-ии соответствует определённый физический элемент. Метод последовательного исключения переменных с помощью законов и тождеств алгебры логики является наиболее простым методом минимизации для этой цели используют чаще всего правила склеивания и правила поглощения. В результате остаются конъюнкции которые между собой не склеиваются, конъюнкция которая не склеивается ни с какой другой конъюнкцией ДНФ называется простой импликантой. Минимизация ПФ с большим числом переменных, этим методом является задачей довольно сложной не всегда можно получить минимальную форму возможно получение тупиковой формы то есть такой которая не упрощается но не является минимальной.

Метод карт (Карно-Вейча) Этот метод удобен для минимизации ПФ содержащих обычно не более 4 переменных (пример в тетр) Диаграмма Вейча имеет вид прямоугольника разбитого на 2 в степени n клеток, где n число переменных ПФ, каждой клетке диаграммы ставится в соответствии определённая конъюнкция при чём конъюнкции в соседних клетках(в строке или в столбце) должны отличатся не более чем значением одной переменной. В результате любые 2 соседние строке или столбце конъюнкции склеиваются по соответствующей переменной. Кроме того соседними на диаграмме являются так же крайние левая и правая конъюнкция в одной строке и верхняя и нижняя конъюнкции в одном столбце. Для минимизации ПФ приводится к СДНФ после чего заполняется диаграмма Вейча для n переменных. При этом в соответствующую клетку диаграммы вписывается 1 если ПФ на данном наборе документов равна 1. Остальные клетки остаются пустыми. В заполненной диаграмме обводят прямоугольными контурами клетки с единицами по следующим правилам: 1)в нутрии контура должны быть клетки только с 1. 2)количество клеток с 1 в контуре =2 в степени n где n 0,1,2 и т.д, то есть =1.2.4.8… 3) 1 в крайних клетках одного столбца или одной строки могут включатся в один контур 4)каждый контур должен включать как можно большее число клеток с 1 а общее число контуров должно быть как можно меньше. После чего записывают минимальную ДНФПФ в виде дизъюнкции простых импликант описывающих эти контуры. В такие импликанты включаются те переменные которые во всех клетках контура имеют или только прямое или только инверсное значение. Раздел 3. Синтез комбинационных схем Тема 3.1 Этапы построения логической схемы 1.Синтез комбинационных схем Синтез - это проектирование схемы реализующей заданный закон её функционирования. Последовательность этапов синтеза КС: 1)составить таблицу истинности по словесному описанию закона функционирования КС. 2)записать СДНФПФКС. 3) минимизировать ПФ. 4)построить на логических элементах КС реализующую ПФ.

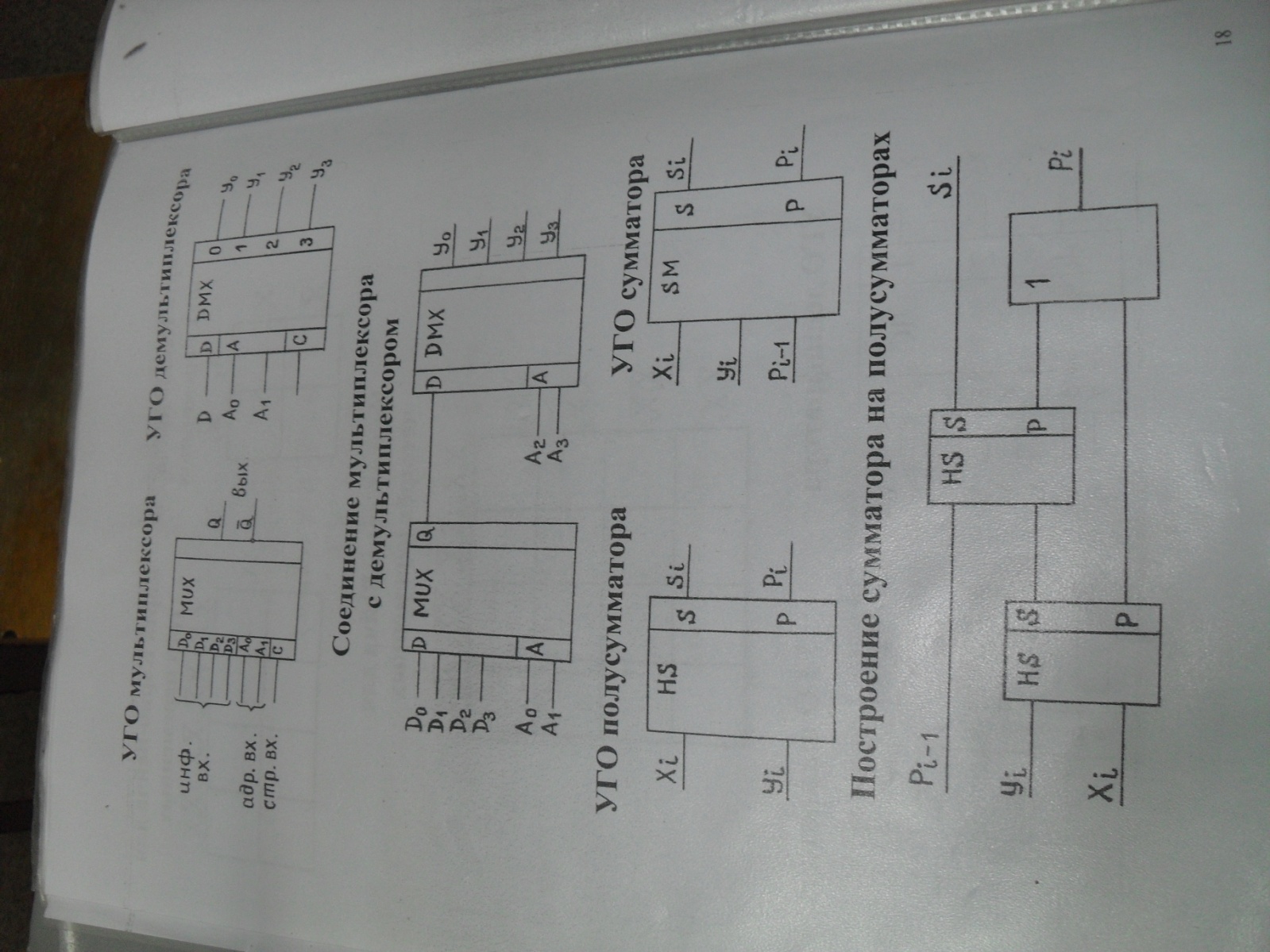

Дешифраторы и шифраторы 1) Дешифратор (ДС) – это логическая схема предназначенная для преобразования n разрядного двоичного кода в один управляющий сигнал, количество входов n и выходов N ДС связано формулой N=

В ЭВМ ДС используется для расшифровки кода адреса и кода команды. Выходы дешифратора имеют нумерацию совпадающую с десятичным представлением двоичного числа (например если на входе код 101 то единичный сигнал появляется только на 5-ом выходе)э Зарисуем УГО дешифратора:

Для схемной реализации ПС необходимо иметь N с большим количеством и числу входов маленькому ДС

Шифратор - это узел цифровой техники преобразующий десятичный код в двоичный код. Рассмотрим принцип построения десяти входового двоичного шифратора (см. рис. выше) Закон функционирования шифратора задан таблицей истинности

Компараторы, сумматоры. 1.Полусумматор (одноразрядный сумматор на 2 входа) Сумматор- это электронный узел выполняющий операцию суммирования цифровых кодов 2 чисел

При сложении 2 чисел в каждом разряде производится сложение 3 цифр. Цифры данного разряда первого слогаемого xi, цифры данного разряда второго слагаемого yi, цифры (1 или 0) переноса из соседнего младшего разряда (pi-1) Результат сложения для каждого разряда состоит из 2 цифр: цифры суммы для этого разряда (Si); цифры(1 или 0) переноса в следующий старший разряд (Pi). Полусумматор служит для сложения 2 двоичных цифр (xi, yi) и не учитывает переноса из соседнего младшего разряда в данный (pi-1) xi+yi=PiSi

Полный одноразрядный комбинационный сумматор на 3 входа. на вход подаются xi, yi, pi-1; имеют 2 выхода si, pi. Такой сумматор можно построить из 2 полусумматоров. Второй полусумматор будет прибавлять к полученной сумме единицу переноса из предыдущего разряд, которая поступает на дополнительный вход pi-1. Последовательный сумматор

Последовательный сумматор преобразует последовательные коды слагаемых в последовательный код их суммы. Сложение 2 многоразрядных двоичных чисел начинается с младшего разряда и выполняется поразрядно последовательно за столько тактов сколько разрядов содержится в двоичном числе. Перед началом счета схема задержки устанавливается в 0. Цифра переноса в каждом такте сложения запоминается в схеме задержки, с выхода которой снимается бит переноса в следующем такте сложения и поступает на вход 3 сумматора SM. Достоинства- малое количество оборудования, недостаток- низкое быстродействие. Параллельные сумматоры В параллельных сумматорах имеется отдельная схема суммирования в для каждого разряда. В этом сумматоре n разрядные числа x1 x2 … xn и y1 y2 …yn подаются одновременно на его входы. Перенос pi-1 каждого отдельного предыдущего одноразрядного сумматора подается на вход переноса последующего одноразрядного сумматора. Компараторы. Цифровые комбинационные устройства сравнения. Устройство сравнения или компаратор- это операционный узел ЭВМ предназначенный для сравнения 2 чисел A и B Результатом сравнения является обнаружение состояний.

Многоразрядные числа сравнивают начиная со старший разрядов. На выход многоразрядного компоратора подают результат сравнения самых старших несовпадающий разрядов. Тема 4.1 Тема 4.2 Синхронезирууемые триггеры

Синхронезируеммые RS триггеры.

R и S информационные входы, С вход синхронизации. При С=0 схемма может работать от не синхронезируемых входов не R и не S. При работе с синхронезируемыми входами на не R и не S должны присутствовать сигналы которые не влияют на состояние схеммы. В данном случае 1. Двухступенчатые.

Состоит их 2 одноступенчатых RS триннеров в цепи синхронизации. При поступлении на вход RS триггера импульса С=1 входная информация заносится только в первый однотактный RS триггер а вотрой триггет при этом будет хронить инфу относящуюся к предедущему переуду представления. По окончании действия импульса синхронизации (С=0 а неС=1) первый RS триггер передет в режим храниния, а второй перепишет из него новое значение выходного сигнала таким образом двухтактный триггер изменяет свое состояние только по окончании действия импульса синхронизации. Для установки триггера в состоянии 0 или 1 без использования синхроимпульсов в схемму введены дополнительные входы не R и не S не синхронизируемой установки. Тема 4.3 Правила выполнения арифметических действий над двоичными числами. Правила выполнения арифметических действий на двочными числами задаются таблицами двоичных сложения вычитания и умножения.

При сложении двоичных чисел в каждом разряде производится сложение двух цифр слогаемых или двух этих цифр и еденицы если имеется перенос из соседнего в младшего разряда. +1101011.01 101110.10 10011001.11

При вычитании двоичных чисел в данном разряде при необходимости занимается еденица из следующего старшего разряда это занимаемая еденица 2-м еденицам данного разряда. -10001.101 110.011 01011.010

-10111.10 1101.01 Д/з Умножение двоичных многоразрядных чисел производится путём оброзования частичных произведений и последующего их сумирования. Операция умножения многразрядных двоичных чисел сводится операциям сдвига и сложения. Положение точки определяется также как и при умножении десятичных чисел.

*1011.1 101.01

Операциии деления двоичных чисел выполняется онологично деления 10-ных чисел с учётам таблиц двоичного умножения и вычитания.

1100.011/10.01

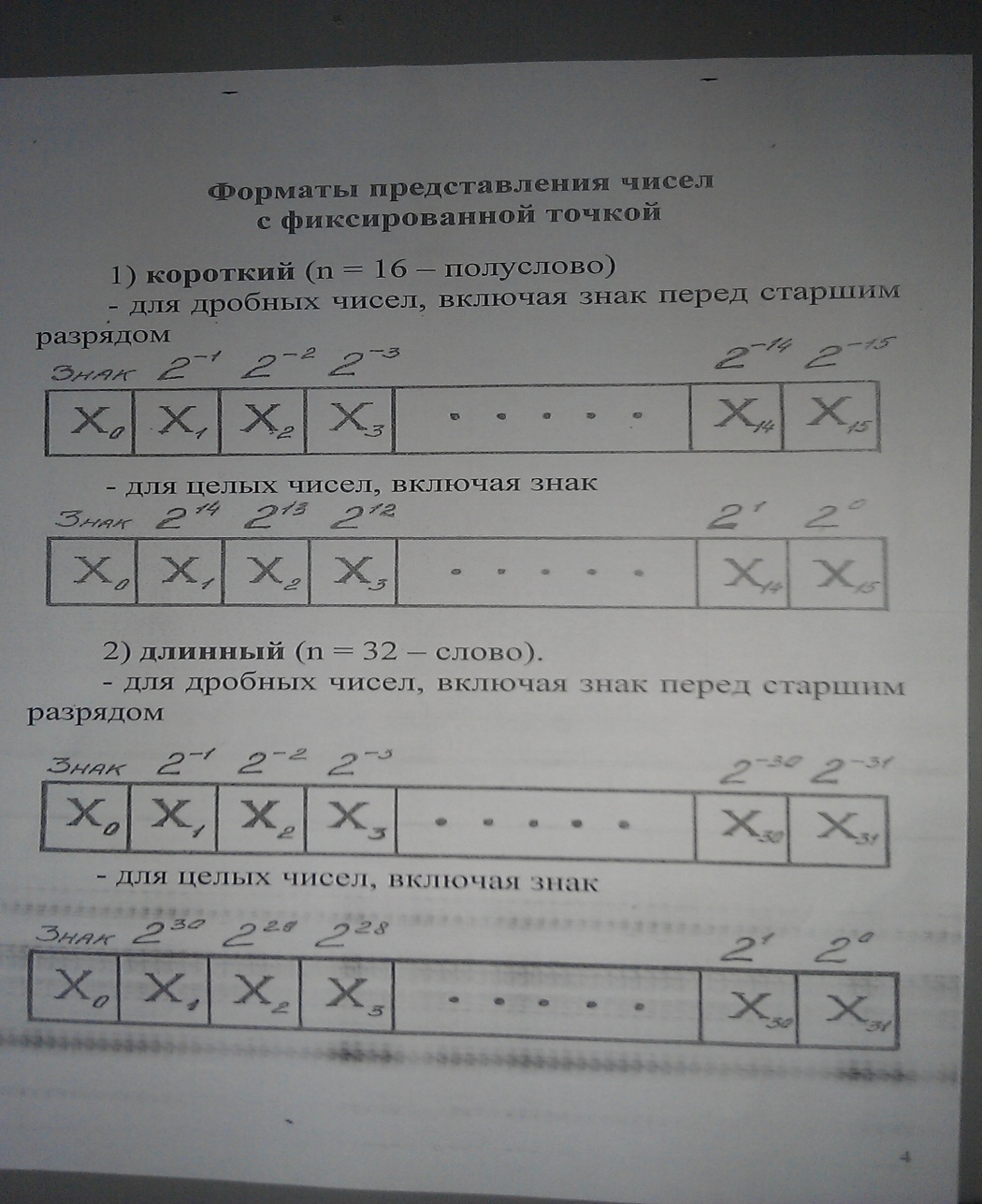

Бдагодаря простоте правил двоичной армфметике применение в компьюерах двоичной ПСС позволяет упростить схемы устройств выполняющих арифметических операции. Естественная форма представления данных. Структура данных- это перечень и взаимосвязь сведенья необходимых для предсавления данных в разрядной сетке машины.Структура данных для чисел задаётся естественно и нормальными формами. В естественной форме число записывается с выделением следующих компонентов числа: знака запетой и цифр числа. Обычно в компьютере положение точки фиксируется схемо-технически – предсавление чисел с фиксированной точкой. Для дробных чисел обычно точка находится перед старшим разрядом а для целых после младшего.Таким образом сохраняется лишь два структурных компанента поле знака и поле цифр. Достоинство форы представления чисел с фиксированной точкой в том что её применение приводит к значительному упрощению лагически и управляющих схем компьютера. Но при подготовке задач к решению необходимо следить за тем чтобы перед сложением или вычитанием исходные числа имели одинаковые масштабы данных. Кроме того необходимо исключить переполнение разрядной сетки. Формат данных определяет разрядность размещаемых в разрядной сетке машины структурноых компанентов данных. Для представления чисел с фиксированной точкой используются следующие форматы. Для представления чисел с фиксированной точкой используется следующие примеры:

Для расширения диапозона представляемых чисел последние могут занимать два-четыре соседних слова.

Нормальные форма предстваления данных. Для расширения диапозона представления чисел и уменьшения погрешности их задания используется нормальная форма записи. A=+- MP+-q Где м мантиса числа, р основание ПСС, q- порядок числа. Порядок с учётом знака показывает на сколько разрядов и в какую сторону сдвинута запятая при замене формы записи числа с естественной на нормальную поэтому такую форму записи называют предсталением чисел с плавающей точкой. В компьютерах используют нармолизованную форму записи для представления чисел с плавающей точкой, число называется нормализованным если его мантиса удовольтворяет условию 1/p<=|m|<1. При представления в компьютере чисел в форме с плавающей точкой они могут иметь 2 формата: короткий(слово), длинный(двойное слово)-отличается от короткого тока длинной мантисы.

Значение порядка –целое число и определяет положеие точки в числе.Знак продка указывает на пренадлежность числа области целых или дробных чисел. При представлении чисел в форме с плавающей точкой в компьютере достигается широкий диапозон изображении чиселно структура таких машин значительно усложняется так как необходимо иметь отдельные усторйства для выполнения опираций как над мантиами так и над порядками чиселпри этом скорость выполнения операции ниже что объестняется необходимостью нормализации чисел выравниванию порядка.

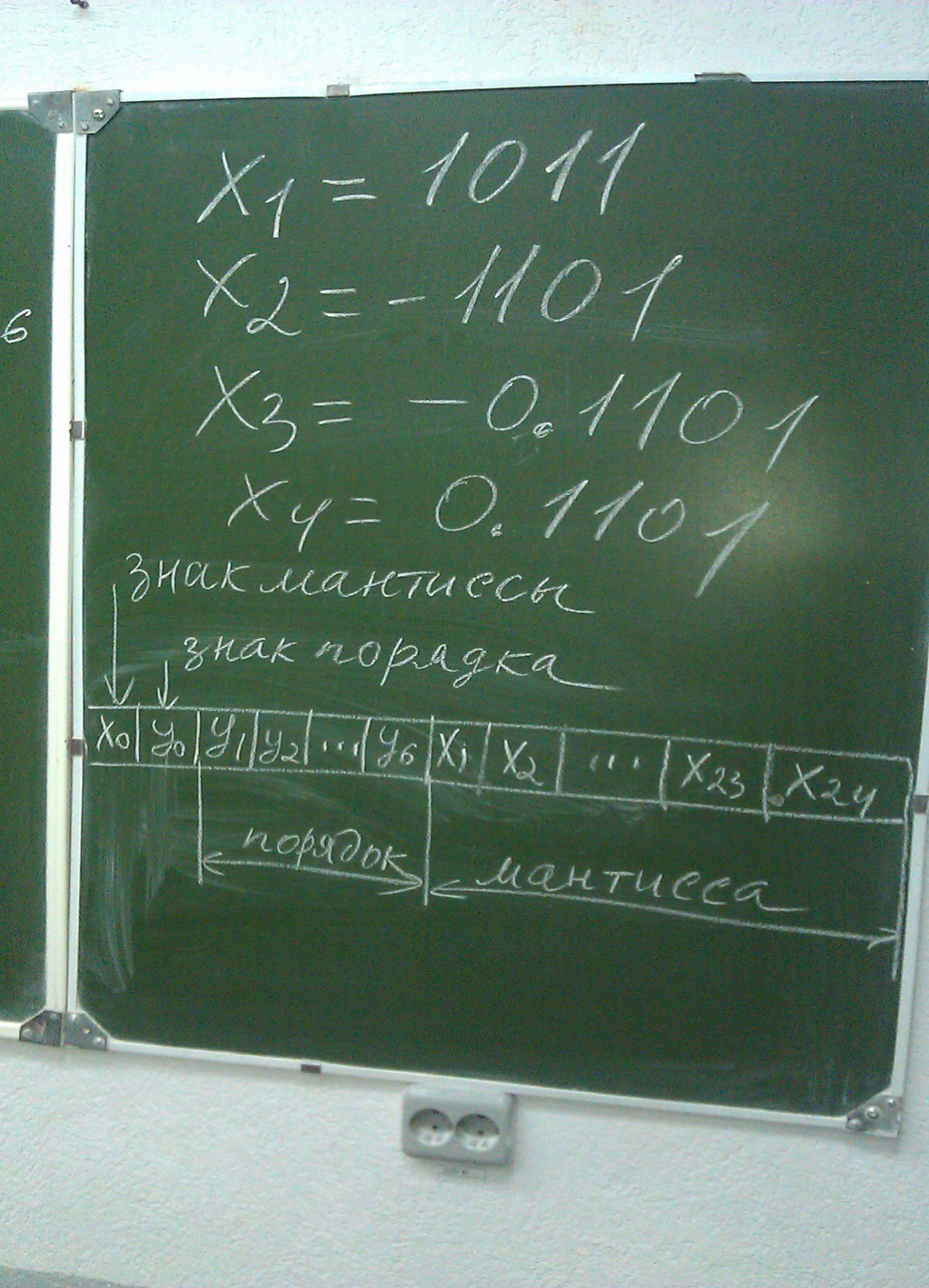

Прямой обратный и дополнительные коды. Для кодировании чисел в компьтере применяют специальные коды: 1) Прямой код Изображение двоичного числа х в прямом коде основано на представлении его абсолютоного значения закодированного знаком. Таким образом прямой код получается при кодировании в числе только знаковой информации причём +кодируется 0 а – кодируетс 1 Х1=1011 Х2=-11011 Х3=-0.1101 Х4=0.1101 [х1]пр.=01011 [x2]пр.=111011 [x3]пр.=1.1101 [x4]пр.=0.1101 В прямом коде 0 может иметь 2 представления: 0=+0=-0 [+0]пр.=0.0000....0 [-0]пр.=1.0000....0 Код знака числа практически во все компьютерах заносится в каждый разряд разрядной сетке например при использовании 8-ми разрядной сеткой числа: [x1]пр.=00001011 [х3]пр.=1.1101000 [x4]пр.=0.1101000 Прямой код используется в компьтере для хранения положительных и отрицательных чисел в запоминающих чисел и при выполнении операции умножении. 2) Обратный код числа х обозначается [x]обратное обратный код положительного числа совподает с его прямым кодом, отрицательного числа образуется следующим образом: первое в знаковом разряде записывается 1, второе в цифровых В обратном коде возможны 2 представлении 0: [+0]обр=0.00000....0 [-0]обр=1.111......1 3) Дополнительный код Дополнительный код числа х обозначается [х]доп. Доп.код с положите.совподает с его прямым кодом.доп.код отрицательного числа образуется следующим образом:1 в знаковом разряде записывается еденица, 2 во все цифровых разрядах заменить еденицы 0 а, 0 еденицами, и третье к младшему разряду числа прибавить еденицу. [x1]доп= 01011 [x2]доп=100101 [x3]доп=1.0011 [x4]доп=0.1101 В дополнительном коде 0 в машине имеет имеет единственное представление: [+0]доп=[-0]доп=0.000....0 [-0]доп= 0.0000...0 Обратные и доп. коды позволяют операцию вычитания в компьютере заменить операции сложения что даёт возможность сведения всех арифетических операций к выполнению операции сложения. Мадифицированные коды. Иногда в кодах под знак отводятся по 2 разряда такие коды называются модифицирванные (прямым, обратным и дополнительным). [x1]пр.м.=[x1]обр.м.=[x1]доп.м.=001011 [x2]пр.м.=1111011 [x2]обр.м.=1100100 [x2]доп.м.=1100101

[x3]пр.м.= 11.1101 [x3]обр.м.=11.0010 [x3]доп.м.=11.0011

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 1104; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.226.169.169 (0.014 с.) |