Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Базовый элемент транзисторно-транзисторной логики (ТТЛ)Содержание книги

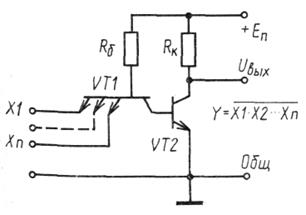

Поиск на нашем сайте В соответствии с рисунком 76показана схема ТТЛ с простым однотранзисторным ключом для логического элемента И-НЕ.

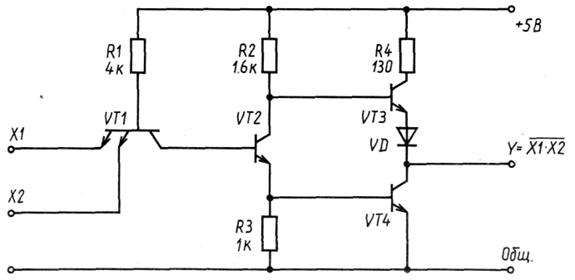

Рисунок 76 На входе элемента включен многоэмиттерный транзистор VT 1. Принцип действия такого транзистора тот же, что и у обычного биполярного транзистора. Единственное отличие заключается в том, что инжекция носителей заряда в базу осуществляется через несколько самостоятельных эмиттерных р— n -переходов. Многоэмиттерный транзистор и сложный инвертирующий ключ и составили схему базового логического элемента И — НЕ ТТЛ. Эта схема в соответствии с рисунком 77 состоит из следующих каскадов: входного многоэмиттерного транзистора VT1, выполняющего логическую операцию И; управляющего транзистора VT 2 и двухтактного инвертирующего выходного каскада на VT 3 и VT4.

Рисунок 77 При этом транзистор VT 4 рассчитан на большой рабочий ток, так как через него стекают на землю входные токи многоэмиттерных транзисторов следующих логических элементов.

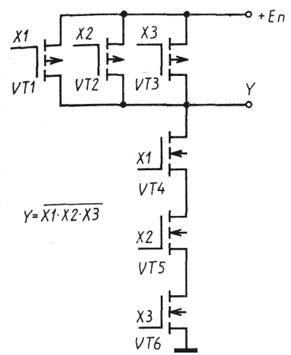

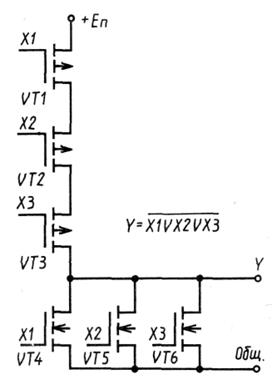

Базовый элемент на КМДП структурах Структура из двух комплементарных МДП-транзисторов, являющаяся идеальным переключателем напряжения, положена в основу базовых элементов И — НЕ и ИЛИ — НЕ в соответствии с рисунками 78 и 79. Как видно из этих схем, для реализации функции И — НЕ используется: - параллельное включение транзисторов p -типа; - последовательное (каскадное) включение транзисторов п -типа. При этом каждый входной сигнал подается на пару транзисторов с каналами различной проводимости.

Рисунок 78 Для реализации базового элемента ИЛИ — НЕ в соответствии с рисунком 79 необходимо поменять местами параллельные и последовательные участки схемы и заменить в каждой группе (параллельной и последовательной) транзисторы с каналами одного типа на транзисторы с каналами противоположного типа проводимости.

Рисунок 79

Элементы последовательностной логики

В цифровых автоматах значение функции зависит не только от значения переменных в данный момент времени (данный такт), но и от их последовательности в предыдущие моменты (такты). Поэтому раздел алгебры логики, описывающий работу цифровых автоматов, обладающих памятью, называется последовательностной логикой. Основным элементом является триггерный элемент памяти, или просто триггер.

Триггеры

Триггер— это устройство с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое и напряжение на его выходе скачкообразно меняется. Триггер имеет два выхода: прямой Q и инверсный

4.6.2. Асинхронный RS -тригтер

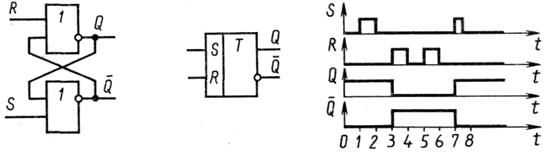

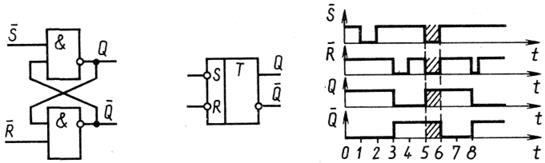

В основе всех схем лежит основной (базовый) асинхронный RS -триггер. Асинхронный RS -тригтерможет быть построен на двух логических элементах ИЛИ — НЕ в соответствии с рисунком 80 либо И — НЕ в соответствии с рисунком 81.

Рисунок 80

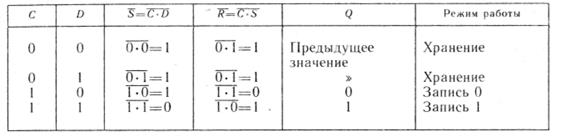

Рисунок 81 Элементы охвачены цепями обратных связей, для чего выход каждого элемента подключен к одному из входов другого элемента. Триггер имеет два входа: S — вход установки в единичное состояние (от англ. set — установка) и R — вход сброса в нулевое состояние (от англ. reset— сброс). Принцип работы триггера: - при S =1 и R =0 происходит установка триггера в устойчивое состояние с Q = 1 и - при S =0 и R =1 происходит установка триггера в устойчивое состояние с Q = 0 и - при S = R =0 триггер сохраняет то устойчивое состояние, которое имел до прихода этих сигналов (режим хранения); - при S = R =1 выходы Q = Описание работы при помощи таблицы переключений представлена в таблице 3 Таблица 3

Асинхронному RS -триггеру присущие серьезные недостатки: - наличие запрещенной комбинации входных сигналов; - подача информации по двум отдельным цепям (R, S); - низкая помехоустойчивость.

Синхронный D-триггер

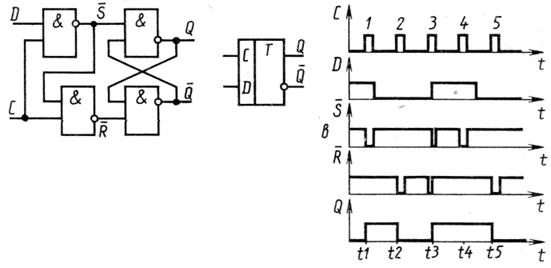

Синхронный D -триггер свободен от недостатков RS -триггера. В соответствии с рисунком 82 D -триггер образован из RS -триггера и входной комбинационной схемы на двух логических элементах.

Рисунок 82 Сигналы, предназначенные для занесения в триггер, поступают на информационный вход D. На вход синхронизации С подают синхроимпульсы, определяющие момент записи информации. Описание работы триггера при различных комбинациях входных сигналов представлено в таблице 4. Таблица 4

Из таблицы 4 видно, что D -триггер находится в режиме хранения при С = 0 и в режиме записи при С = 1. Такой триггер задерживает выходной сигнал до окончания того такта, в который он был записан. Отсюда произошло и название D -триггера (от англ. delay — задержка). Если сигнал на входе изменится во время действия синхроимпульса, то в триггере окажется записанной та информация, которая предшествовала окончанию синхроимпульса. Благодаря этому свойству (изменение информации в течение всего времени, пока С = 1) рассмотренный триггер называется статическим синхронным D -триггером. Для нормальной работы статического D -триггера необходимо, чтобы изменение информации на D -входе происходило только при С = 0.

|

||

|

Последнее изменение этой страницы: 2021-04-04; просмотров: 338; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.214 (0.008 с.) |

. Число входов зависит от выполняемых функций. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может изменяться в любой момент времени при изменении входных сигналов. В синхронизируемых триггерах информация на выходе может меняться только в определенные моменты времени, задаваемые дополнительным синхронизирующим сигналом. Существует большое число разнообразных триггеров с различными функциональными возможностями.

. Число входов зависит от выполняемых функций. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может изменяться в любой момент времени при изменении входных сигналов. В синхронизируемых триггерах информация на выходе может меняться только в определенные моменты времени, задаваемые дополнительным синхронизирующим сигналом. Существует большое число разнообразных триггеров с различными функциональными возможностями.