Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Обобщенная структурная схема микропроцессора

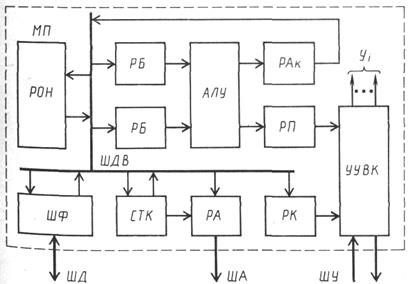

Рассмотренные функциональные и структурные особенности операционного и управляющего блоков микропроцессора позволяют составить обобщенную структурную схему, представленную в соответствии с рисунком 117. Основой ее является общая внутренняя шина данных (ШДВ), соединяющая все элементы операционного блока (на схеме расположены выше ШДВ) и элементы управляющего блока (расположены ниже ШДВ). Шинный формирователь (ШФ), связывающий внутреннюю шину данных с внешней (ШД), является общим элементом как для операционного, так и для управляющего блоков.

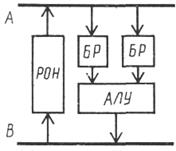

Рисунок 117 Структура микропроцессора с одной внутренней шиной данных не является единственно возможной. В соответствии с рисунками 118 и 119 представлены схемы двухшинной и трехшинной организации операционного блока соответственно.

Рисунок 118 Увеличение числа внутренних шин данных позволяет совмещать во времени операции пересылки данных из одного операционного элемента в другой и ведет к росту быстродействия МП.

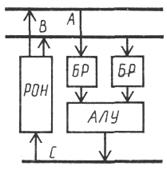

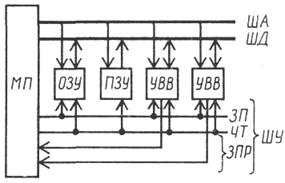

Рисунок 119 В то же время увеличение числа шин уменьшает площадь кристалла, которую можно занять под различные функциональные элементы, и тем самым (при фиксированной площади) приводит к уменьшению функциональных возможностей МП. Поэтому промышленность выпускает микропроцессоры, в которых в зависимости от назначения по-разному организованы внутренние шины данных. На характеристики МП большое влияние оказывают число и организация не только внутренних, но и внешних шин. В связи с ограниченностью числа выводов БИС в некоторых МП применяют общие шины адреса и данных. В таких системах обмен информацией с внешними устройствами ввода — вывода (УВВ) или запоминающими устройствами (ОЗУ, ПЗУ) требует большого времени (до 8 тактов). Кроме того, необходим специальный внешний регистр для запоминания адреса, так как после 1-го такта шину надо освободить для передачи данных. Поэтому большее распространение получили МП с раздельными внешними шинами данных и адреса. В этих МП шина адреса однонаправленная, по ней адресные сигналы только передаются к внешним устройствам. Шина данных двунаправленная, информация по ней и передается от МП к внешним устройствам (ОЗУ, УВВ), и принимается от них (ОЗУ, ПЗУ, УВВ).

Внешняя шина управления ШУ во всех микропроцессорах самостоятельна. Эта шина многоразрядная, и каждая линия в ней однонаправлена, т. е. служит только для передачи или только для приема управляющих сигналов. В состав этой шины обязательно входят линии передачи сигналов записи (ЗП) в память и УВВ, а также сигналов чтения (ЧТ) из памяти и УВВ. Эти сигналы организуют соответствующий режим работы того устройства, адрес которого выставлен в этот момент на шине ША. Сигналы ЗП и ЧТ организуют обмен данными между МП и внешними устройствами по инициативе МП. Но бывают ситуации, когда внешние устройства вынуждены обращаться к МП по своей инициативе. Примером может служить обращение пользователя к МП через клавишный пульт ввода информации. В этом случае внешнее УВВ (пульт) выставляет запрос на прерывание (ЗПР) текущей программы и обслуживание микропроцессором внешнего устройства. Если внешних устройств, которые могут выставить сигнал ЗПР, больше, чем входов запросов на прерывание у МП, то необходима дополнительная БИС — контроллер прерываний, которая устанавливала бы очередность этих сигналов и пропускала их на вход МП по заданному приоритету. Обработка запросов на прерывание в МП ведется схемой прерывания (СП), входящей в состав УУВК. Этот узел (СП) должен выполнить следующие действия: - выбрать момент, когда можно прервать основную программу и выставить на линии управления сигнал, подтверждающий разрешение прерывания (РПР); - дать команду на запись в РОН состояния счетчика команд и регистра признаков в момент прерывания; - запустить выполнение команды обслуживания УВВ; - после окончания обслуживания УВВ вернуть исходную информацию в СТК и РП и запустить продолжение выполнения основной программы с прерванного места. Помимо описанных управляющих сигналов в различных микропроцессорах применяются и другие сигналы, облегчающие организацию наиболее трудоемких для программирования операций взаимодействия с внешними устройствами.

Синхронизация работы

В начале работы логические схемы должны находиться в устойчивом исходном состоянии. Однако когда в качестве входных сигналов используются электрические импульсы, то необходимо некоторое время для того, чтобы выходные величины достигли уровня установившегося состояния из-за внутренних задержек в схеме. В электронных машинах двоичные сигналы проходят через множество схем и задержка может стать значительной. В этом случае необходимо выделить отрезок времени (такт) на каждую операцию. Если операциязавершается раньше, чем закончится тактовое время, машина ожидает его окончания. В результате скорость выполнения операций несколько снижается, но достигается высокая надежность, так как обеспечивается синхронизация между многими параллельно выполняющимися операциями.

Синхронизация внутри ЦВМ обеспечивается с помощью специального генератора, который работающий в автоколебательном режиме и формирующий импульсы стабильной частоты. Два уровня импульсов соответствуют двум логическим состояниям двоичных переменных 0 и 1. Почти все операции в машине синхронизируются посредством этих импульсов. Однако обмен информацией по каналам ввода — вывода между ЭВМ и внешними устройствами обычно осуществляется асинхронно.

|

||||||

|

Последнее изменение этой страницы: 2021-04-04; просмотров: 134; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.138.125.2 (0.007 с.) |