Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Схема тактирования и цикл выполнения командыСодержание книги

Поиск на нашем сайте

Входная тактовая частота, поступающая с вывода OSC1/CLKIN, делится внутри на четыре, и из нее формируются четыре циклические не перекрывающиеся тактовые последовательности Q1, Q2, Q3 и Q4. Счетчик команд увеличивается в такте Q1, команда считывается из памяти программы и защелкивается в регистре команд в такте Q4. Команда декодируется и выполняется в течение последующего цикла в тактах Q1...Q4. Цикл выполнения команды состоит из четырех тактов: Q1...Q4. Выборка команды и ее выполнение совмещены по времени таким образом, что выборка команды занимает один цикл, а выполнение – следующий цикл. Эффективное время выполнения команды составляет один цикл. Если команда изменяет счетчик команд (например, команда GOTO), то для ее выполнения потребуется два цикла. Цикл выборки начинается с увеличения счетчика команд в такте Q1. В цикле выполнения команды выбранная команда защелкивается в регистр команд в такте Q1. В течение тактов Q2, Q3 и Q4 происходит декодирование и выполнение команды. В такте Q2 считывается память данных (чтение операнда), а запись происходит в такте Q4.

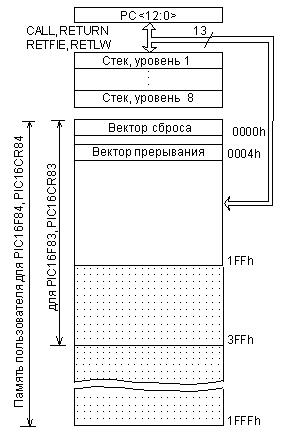

Организация памяти программ и стека Счетчик команд в МК PIC16F8Х имеет ширину 13 бит и способен адресовать 8Кх14бит объема программной памяти. Однако физически на кристаллах PIC16F83 и PIC16CR83 имеется только 512х14 памяти (адреса 0000h-01FFh), а в МК PIC16F84 и PIC16CR84 – 1Кх14 памяти (адреса 0000h-03FFh). Обращение к адресам выше 1FFh (3FFh) фактически есть адресация в те же первые 512 адресов (первые 1К адресов). Организация памяти программ и стека приведена на рисунке 40.2. В памяти программ есть выделенные адреса. Вектор сброса находится по адресу 0000h, вектор прерывания – по адресу 0004h. Обычно по адресу 0004h располагается подпрограмма идентификации и обработки прерываний, а по адресу 0000h – команда перехода на метку, расположенную за подпрограммой обработки прерываний.

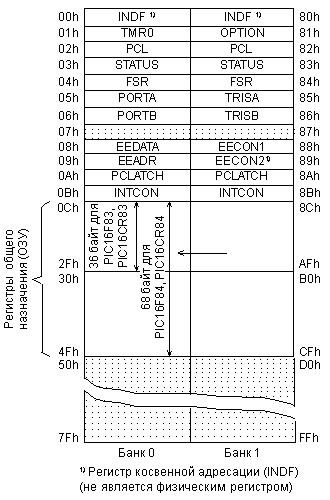

Рисунок 40.2 - Организация памяти программ и стека Организация памяти данных Память данных МК разбита на две области. Первые 12 адресов – это область регистров специальных функций (SFR), а вторая – область регистров общего назначения (GPR). Область SFR управляет работой прибора. Обе области разбиты в свою очередь на банки 0 и 1. Банк 0 выбирается обнулением бита RP0 регистра статуса (STATUS). Установка бита RP0 в единицу выбирает банк 1. Каждый банк имеет протяженность 128 байт. Однако для PIC16F83 и PIC16CR83 память данных существует только до адреса 02Fh, а для PIC16F84 и PIC16CR84 – до адреса 04Fh. На рисунке 40.3 изображена организация памяти данных.

Рисунок 40.3 - Организация памяти данных

Некоторые регистры специального назначения продублированы в обоих банках, а некоторые расположены в банке 1 отдельно. Регистры с адресами 0Ch - 4Fh могут использоваться как регистры общего назначения, которые представляют собой статическое ОЗУ. Адреса регистров общего назначения банка 1 отображаются на банк 0. Следовательно, когда установлен банк 1, то обращение к адресам 8Ch - CFh фактически адресует банк 0. В регистре статуса помимо бита RP0 есть еще бит RP1, что позволяет обращаться к четырем страницам (банкам) будущих модификаций этого кристалла. К ячейкам ОЗУ можно адресоваться прямо, используя абсолютный адрес каждого регистра, или косвенно, через регистр указатель FSR. Косвенная адресация использует текущее значение разрядов RP1:RP0 для доступа к банкам. Это относится и к EEPROMпамяти данных. В обоих случаях можно адресовать до 512 регистров.

|

||||

|

Последнее изменение этой страницы: 2021-02-07; просмотров: 210; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.218.123.194 (0.006 с.) |