Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Концептуальная блок-схема CPU.Содержание книги

Поиск на нашем сайте

На схеме представлены:: · 32-разрядная шина считываемых команд. На нее считываются команды из памяти программ. · 22-разряднаяадресная шина команд. · 32-разрядная адресная шина считываемых данных. · 32-разрядная шина считываемых данных. На нее считываются данные из памяти данных. · Буфер считываемых данных. Это регистр для хранения считанных данных. Его выход передается на шину операндов, либо на генератор адреса памяти программ, если данные - это адрес стека. Это первый операнд при выполнении команды. · Шина операндов. На ней находится первый операнд при выполнении команды. · Шина результата операции в исполнительном устройстве. · Буфер записываемых данных. Это регистр данных, записываемых в память данных. Он загружается с шины результатов операции Result Bus. · Логика управления командами. Декодирует считанную команду и передает данные исполнительным устройствам. · Логика генерации адресов команд. · Арифметический модуль адресного регистра ARAU. Вычисляет адреса для регистрового файла и адресной шины считываемых данных. · Регистровый файл, который содержит набор регистров (системные и общего назначения). · Исполняющее устройство, включает - умножитель, параллельный сдвигатель, АЛУ. Умножитель реализован аппаратно, выполняет умножение 32х32 или два умножения 16х16. Исполнительное устройство.

Основные регистры. Определен комплект регистров. Основные регистры:

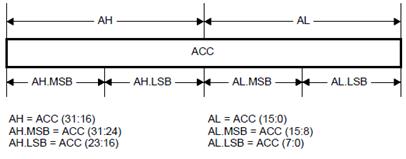

Аккумулятор (ACC). Главный регистр – аккумулятор (ACC). Он хранит результаты операций в АЛУ. Он поддерживает одноцикловые операции перемещения, сложения, вычитания и сравнения с данными из 32-разрядной памяти данных. Он также принимает 32-разрядный результат от умножителя. Для ACC возможен доступ и к части его содержимого: AH – старшая часть, AL – младшая часть. Для каждого из них можно получать младший LSB или старший MSB байты.

Статусный регистр ST0. В нем запоминаются флаги состояния ACC

Флаги (по умолчанию все сброшены): · Расширение знака (Sign-extension mode - SXM), бит 0. Если SXM=1, то при загрузке 16-разрядного числа со знаком в 32-разрядный ACC оно перед загрузкой расширяется по знаку (пустые биты заполняются битом знака) до 32-разрядного представления. · Переполнение (Overflow mode -OVM), бит 1. Если OVM = 0 (режим переполнения выключен), то переполнения считаются в поле OVC в ACC. Если OVM = 1 (режим переполнения включен), то переполнения не подсчитываются, в ACC заносятся значения насыщения. · Флаг теста/контроля (Test/control - TC), бит 2. · Перенос (Carry - C), бит 3. · Флаг нуля (Zero flag - Z), бит 4. Если результат операции равен 0, то Z=1. · Флаг отрицательного значения (Negative - N), бит 5. Если результат операции отрицательное число, то N=1. · Флаг запрета переполнения (Latched overflow flag - V), бит 6. Если результат операции вызывает переполнения в регистре хранения результата, то V=1 и защелкивается. Если нового переполнения нет, то V не меняется, остается защелкнутым от предыдущего переполнения. · Поле режима сдвига произведения (Product shift mode bits - PM). Поле в битах 7…9. 3-разрядное значение определяет режим сдвига для значения, получаемого из регистра произведения P. Возможные режимы:.

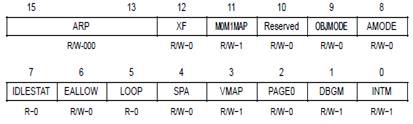

· Счетчик переполнения операций с числами со знаком (Overflow counter - OVC). Для чисел без знака OVCU. Поле в битах 10…15. Счетчик 6-разрядный со значениями от -32 до 31. При OVC=0 содержимое ACC не меняется. При OVC>0 содержимое ACC = насыщение по максимуму ($7FFFFFFF), OVC = 0. При OVC<0 содержимое ACC = насыщение по минимуму ($8000000), OVC = 0. · Статусный регистр ST1 В нем запоминаются флаги состояния разных узлов.

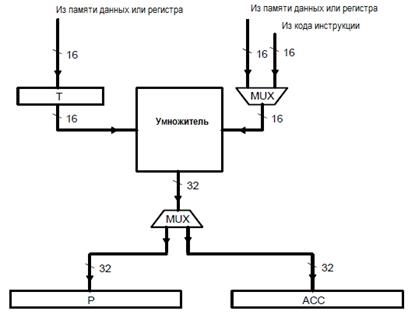

Флаги (по умолчанию все сброшены): · Флаг глобальной маски прерывания (Inerrupt global mask - INTM), бит 0. Если INTM=1, то маскированное прерывание запрещено. · Флаг массирования отладки (Debag enable maskt -DBGM), бит 1. Если DBGM = 1, то отладка запрещена. · Флаг режима адресации (PAGE0). Размещен в бите 2. При PAGE0=0 – адресация через стек, при PAGE0=1 – прямая. · Флаг размещения вектора прерываний (VMAP), бит 3. При VMAP=0 вектор внизу памяти программ (адреса $000000…$000003F), при VMAP=1 вектор вверху памяти программ (адреса $3FFFC0…$3FFFFF). · Флаг размещения указателя стека (Stack pointer alignment - SPA), бит 4. При SPA=0 указатель стека SP не может занимать четные адреса. · Статус инструкции цикла (LOOP), бит 5. При LOOP=1 то под операцию LOOP отводится два этапа конвейера. · Флаг разрешения эмуляции (EALLOW), бит 6. При EALLOW=1 разрешены эмуляция и доступ к защищенным регистрам. · Флаг режима только чтение (IDLESTAT), бит 7. Устанавливается IDLESTAT=1 при выполнении инструкции IDLE. Флаг сбрасывается командами, отменяющими этот режим. · Флаг режима адресации (AMODE), бит 8. · Флаг совместимости режима (OBJMODE), бит 9. При OBJMODE=0 режим C27x, при OBJMODE=1 режим C28x. · Флаг размещения M0, M1 (M0M1MAP), бит 11. Для C28x.обязательно M0M1MAP=1. · Статус выходного сигнала XFS (XF), бит 12. При XF=1 совместимость с C2xLP. · Указатель на дополнительные регистры (Auxiliary register pointer.- ARP). Поле размещено в битах 13-15. В него заносится 3-разрядный номер регистра (0-7). · Умножитель C28x содержит встроенный аппаратный умножитель, выполняющий умножение за 1 такт. Возможны: · умножение16х16 · умножение16х16 с накоплением MAC · умножение 32х32 · умножение 32х32 с накоплением DMAC Концептуальная блок-схема умножителя в режиме 16x16. Умножитель получает 16-разрядные сомножители. Первый заносится в регистр T (старшая часть XT)из памяти данных или регистра. Второй извлекается из мультиплексора MUX, который получает значение из памяти данных или регистра, либо из кода инструкции. 32-разрядное произведение через MUX заносится в регистр произведения P (и может использоваться как операнд) и в аккумулятор ACC (для выполнения операций MAC).

Концептуальная блок-схема умножителя в режиме 32x32. Умножитель получает 32-разрядные сомножители. Первый заносится прямо из памяти данных или регистра Второй извлекается из MUX, который получает значение из памяти программ или регистра XT, который загружается из памяти данных или регистра. 64-разрядное произведение содержит 32-разрядные части (старшую и младшую). Одна из них через MUX и заносится в регистр произведения P.

Сдвигатель. Сдвигатель имеет 64 разряда и поддерживает операции сдвига влево и вправо. Входные операнды могут иметь длину 16, 32 или 64 разряда. Возможные сдвиги: · Логический влево. Старшие биты теряются, младшие заполняются нулями.

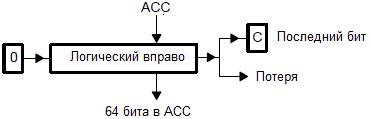

· Логический вправо. Младшие биты теряются, старшие заполняются нулями. Последний выдвигаемый бит заносится в бит переноса С.

· Арифметический вправо. Младшие биты теряются, последний выдвигаемый бит заносится в бит переноса С. В старших расширение бита знака Sign.

· Циклический влево. Старшие биты по цепочке переносятся в младшие (в цепочку входит бит переноса С)аполняются нулями.ряда.га влево и вправо..

· Циклический вправо. Младшие биты по цепочке переносятся в старшие (в цепочку входит бит переноса С)аполняются нулями.ряда.га влево и вправо..

Прерывания и приоритеты. Прерывание это сигнал, генерируемый аппаратно или программно, по которому ЦП останавливает текущую программу и переходит к выполнению подпрограммы обработки прерывания. Обычно прерывания генерируются периферийными или аппаратными блоками, для того чтобы получить данные от ЦП. Различаются прерывания: · Маскируемые. Они могут быть блокированы или отменены другими устройствами. Каждому маскируемому прерыванию присваивается приоритетный номер (номер ниже – приоритет выше). Маскируемое прерывание выполняется, если нет запросов прерывания с более высокими приоритетами. · Немасккируемые. Они не могут быть блокированы или отменены другими устройствами. Обработка прерывания включает 4 фазы: · Прием запроса прерывания. · Обработка запроса. Если прерывание маскируемое, то нужно проверить условия разрешения прерывания. Немаскируемое прерывание должно выполняться немедленно. · Подготовка к обработке прерывания. Завершить текущую инструкцию, выполнить операции в конвейере, сохранить контекст программы (значения регистров, текущее состояние счетчика команд). Извлечь из вектора прерывания адрес процедуры обработки и загрузить его в программный счетчик. · Запустить процедуру обработки прерывания. После завершения происходит возврат в текущую программу. C28x поддерживает 32 вектора прерывания: 19 приоритетных прерываний с приоритетами 1…19 (19 – нижний), 12 неприоритетных прерывания пользователя, 1 прерывание при неправильной инструкции. Каждый вектор включает стартовый адрес процедуры обработки прерывания (Interrupt Service Routine - ISR). Он накапливается в двух соседних словах памяти. Конвейер. Для повышения производительности C28x использует защищенный 8-уровневый конвейер. На каждом уровне конвейера может быть команда для аппаратного блока ЦП (F1, F2, D1, D2, R1, R2, X, W). Конвейер работает независимо от действий программиста. Он управляется командами, заложенными в ЦП. Конвейер предотвращает возможность записи и чтения по одному и тому же адресу в порядке, не предусмотренном программистом. Если такое происходит, то ЦП вставляет в конвейер пустые операции.

На рисунке выделен интервал времени, когда одновременно работают 8 блоков ЦП. За счет распараллеливания конвейер позволяет C28x работать на высокой скорости, не прибегая к использованию дорогой высокоскоростной памяти. Специальное устройство предсказания переходов минимизирует задержку на условных переходах. Специальным образом организованные переходы еще больше увеличивают производительность. Архитектура F28x В нем поддерживаются операции с плавающей точкой. F28x = C28x + Flash. Имеются дополнительные регистры: Регистры R0H – R7H используются для хранения результатов операции с плавающей точкой, 32 бита. Регистр FPU Status Register (STF) - регистр статуса блока с плавающей точкой, 32 бита. Его структура:

Регистр блока повторов (Repeat Block - RB), 32 бита. Его структура:

Блок-схема.

Ядро процессора с производительностью 300MFLOPs при частоте 150МГц включает: · 32x32 аппаратный умножитель. · 32-разрядные таймеры (3). · Встроенный модуль отладки (JTAG реального времени). · Атомарное АЛУ, выполняющее короткие RISC инструкции. · 32-разрядный модуль умножитель с ПТ. Подсистема памяти: · Flash до 512 Кбайт. · ОЗУ (RAM) 68 Кбайт. · Загрузочное ПЗУ (ROM). · Интерфейс EMIF. · 6 каналов прямого доступа к памяти (DMA). Периферийный модули: · 18 модулей ШИМ. · Высокоскоростной встроенный АЦП. · 6 модулей захвата (CAP). · 88 выводов общего назначения. · 2 канала McBSP с возможностью конфигурирования в режим SPI. · Порт CAN 2.0b с 32 почтовыми ящиками (mailboxes). · Интерфейс PC со скоростью 480 кбит/с. · 2 импульсных квадратурных декодера (QEP). Питание: · Ядро 1,9 В. · 3,3 В периферия.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 216; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.116.85.204 (0.007 с.) |