Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Микроконтроллер AVR от Atmel

Архитектура AVR от Atmel AVR - самая обширная производственная линии среди других флэш-микроконтроллеров корпорации Atmel. Atmel представила первый 8-разрядный флэш-микроконтроллер в 1993 году и с тех пор непрерывно совершенствует технологию. Прогресс данной технологии наблюдался в · снижении удельного энергопотребления (мА/МГц), · расширении диапазона питающих напряжений (до 1.8 В) для продления ресурса батарейных систем, · увеличении быстродействия до 16 млн. операций в секунду, · встраивании эмуляции в реальном масштабе времени, · реализации функции самопрограммирования, · совершенствовании и расширении количества периферийных модулей, · встраивании специализированных устройств (радиочастотный передатчик, USB-контроллер, драйвер ЖКИ, программируемая логика, контроллер DVD, устройства защиты данных) и др. Успех AVR-микроконтроллеров объясняется возможностью простого выполнения проекта с достижением необходимого результата в кратчайшие сроки, чему способствует доступность большого числа инструментальных средств проектирования, поставляемых, как непосредственно корпорацией Atmel, так и сторонними производителями. Ведущие сторонние производители выпускают полный спектр компиляторов, программаторов, ассемблеров, отладчиков, разъемов и адаптеров. Отличительной чертой инструментальных средств от Atmel является их невысокая стоимость. Другая особенность AVR-микроконтроллеров, которая способствовала их популярности, это использование RISC-архитектуры с мощным набором инструкций, большинство которых выполняются за один машинный цикл. Это означает, что при равной частоте тактового генератора они обеспечивают производительность в 12 (6) раз больше производительности предшествующих микроконтроллеров на основе CISC-архитектуры (например, MCS51). С другой стороны, в рамках одного приложения с заданным быстродействием, AVR-микроконтроллер может тактироваться в 12 (6) раз меньшей тактовой частотой, обеспечивая равное быстродействие, но при этом потребляя гораздо меньшую мощность. Таким образом, AVR-микроконтроллеры представляют более широкие возможности по оптимизации производительности/энергопотребления, что особенно важно при разработке приложений с батарейным питанием. Микроконтроллеры обеспечивает производительность до 16 млн. оп. в секунду и поддерживают флэш-память программ различной емкости: 1… 256 кбайт. AVR-архитектура оптимизирована под язык высокого уровня Си, а большинство представителей семейства megaAVR содержат 8-канальный 10-разрядный АЦП, а также совместимый с IEEE 1149.1 интерфейс JTAG или debugWIRE для встроенной отладки. Кроме того, все микроконтроллеры megaAVR с флэш-памятью емкостью 16 кбайт и более могут программироваться через интерфейс JTAG.

Пример использования

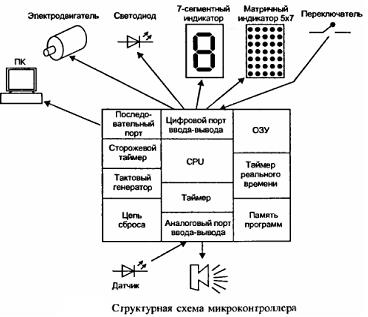

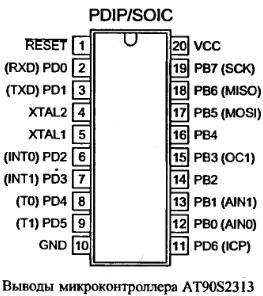

Основные параметры · Гарвардская архитектура. · RISC. · Количество команд 90…130. · Число выводов 8…64. · Частота тактового генератора 10…16 МГц. · Большинство инструкций выполняются за 1 цикл тактового генератора ТГ. · Производительность 10…16 МIPS (Millions Instructions per Second). · Память программ типа FLASH ROM. Перепрограммируется до 1000 раз. · Память данных ОЗУ (тип EEPROM). Перепрограммируется до 100000 раз. · 32 регистра общего назначения. · Есть режимы с пониженным энергопотреблением. · Отладчик AVR Studio, бесплатный. Семейства · Tiny AVR – миниатюрные МК. Flash ROM 1…2 Кбайт, ОЗУ типа EEPROM 64 байт · Classic AVR. Flash ROM 2…8 Кбайт, ОЗУ типа EEPROM 64…512 байт, ОЗУ типа SRAM 128…512 байт · Mega AVR Flash ROM 2…128 Кбайт, ОЗУ типа EEPROM 64…512 байт, ОЗУ типа SRAM 2…4 Кбайт, 10 разрядный 8-и канальный АЦП, аппаратный умножитель 8*8 Микроконтроллер AT90S2313 выбран как пример для изучения основ. Это современный 8-битный КМОП МК. Он имеет производительность 1 MIPS при частоте ТГ в 1 МГц, так как почти все его команды выполняются за 1 период ТГ. Используется расширенная RISC архитектура от ARM, 32 регистра общего назначения. Все регистры подключены к арифметико-логическому устройству АЛУ, что дает доступ к 2-м регистрам в течение 1 цикла. Его основные характеристики: · 2 Кб загружаемой FLASH памяти. Может быть перепрограммирования через интерфейс SPI. · 128 байт EEPROM для данных. · 15 линий ввода/вывода общего назначения. · 2 таймера/счетчика (один 8-разрядный, другой 16-разрядный.). · Внешние и внутренние прерывания · Встроенный последовательный порт. · Программируемый сторожевой таймер со встроенным генератором. · Последовательный порт SPI для загрузки программ.

· 2 выбираемых программно режима низкого энергопотребления. Описание выводов

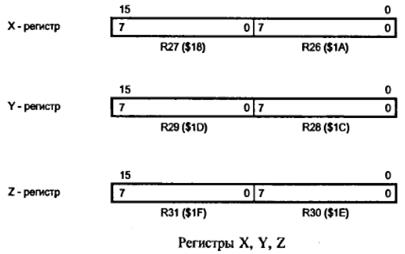

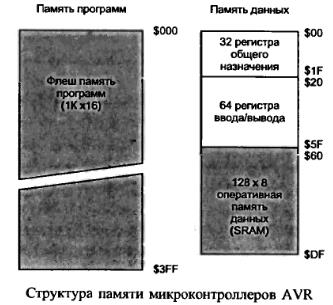

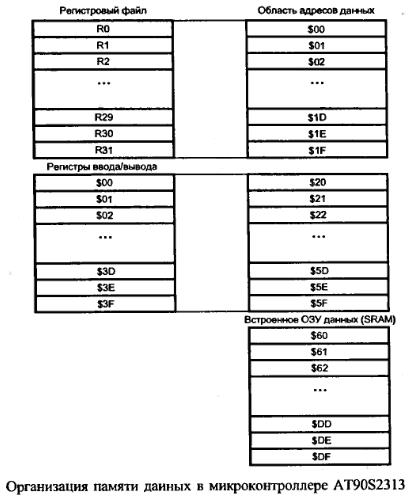

· VCC – питание. · GND – земля. · PORT B (PB7…PB0) – 8-разрядный параллельный порт ввода/вывода. Выводы PBO, PB1 являются также положительным (A1N0) и отрицательным (A1N1) входами встроенного аналогового компаратора. · PORT D (PD6…PD0) – 7-разрядный двунаправленный параллельный порт ввода/вывода с встроенными подтягивающими резисторами. Входы воспринимают ток до 20 мА. · RESET – вход сброса для перезапуска МК. · XTAL1 и XTAL2 – вход и выход инвертирующего усилителя, используемые для построения ТГ. К ним можно подключить кварцевый резонатор, задающий частоту ТГ. Обзор архитектуры Файл регистров общего назначения РОН. 32 8-разрядных. Регистровый файл занимает адреса $00…$1F, поэтому к регистрам можно обращаться и как ячейкам памяти данных. Большинство команд, использующих регистры, могут обращаться к любым РОН. Исключение составляют команды, работающих с константами: SBCI, SUBI, CPI, ANDI, ORI, LDI. Они работают только со второй половиной файла РОН – R16…R31. Каждому регистру присвоен и адрес в первых 32 ячейках ОЗУ. Это удобно. Пространство ввода/вывода состоит из 64 адресов $20…$5F. АЛУ поддерживает арифметические и логические операции. 6 РОН (R26…R31) можно использовать как 3 16-разрядных указателя X,Y,Z в адресном пространстве данных. Указатель Z можно использовать для адресации таблиц в памяти программ.

Структура памяти Использована Гарвардская архитектура – данные и программа в разных устройствах памяти.

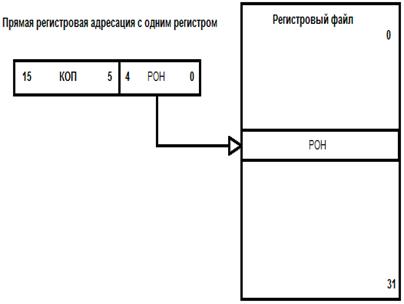

Во время выполнения одной команды следующая команда считывается одновременно из памяти программ. Режимы адресации Прямая регистровая адресация с одним регистром. В качестве источника используется любой РОН. Результат заносится туда же.

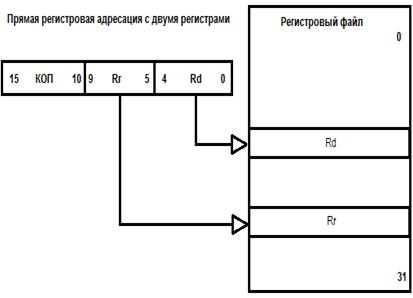

Код команды содержит 1 слово. КОП – код операции, РОН определяет используемый регистр. Прямая регистровая адресация с двумя регистрами. Код команды содержит 1 слово: КОП – код операции, Rr – источник данных, Rd – получатель результата.

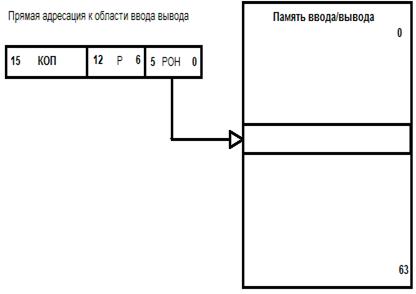

Прямая адресация к области ввода вывода. Операция осуществляется с данными в поле P. Используется регистр РОН, он может быть источником или получателем данных.

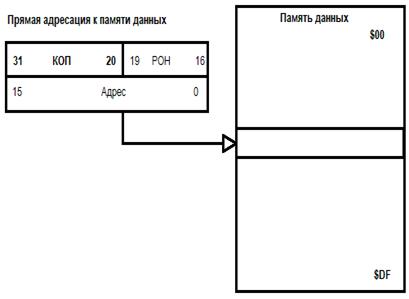

Прямая адресация к памяти данных. Код команды состоит из 2-х слов. В старшем слове команды размещены - код операции КОП и используемый РОН. В младшем слове находится 16-разрядный адрес ячейки памяти данных.

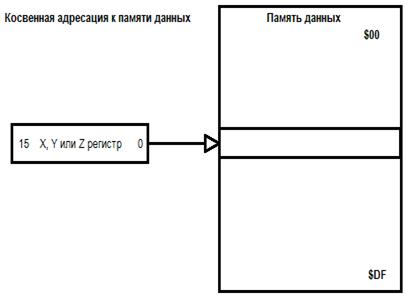

Косвенная адресация к памяти данных. Адрес операнда находится в одном из регистров X, Y, Z.

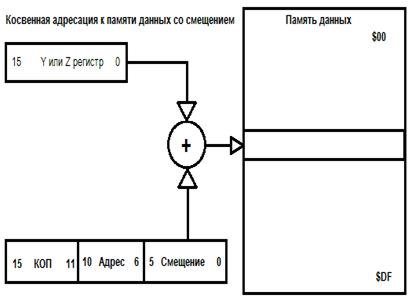

Косвенная адресация к памяти данных со смещением. Адрес операнда определяется как сумма содержимого Z или Y регистра и смещения.

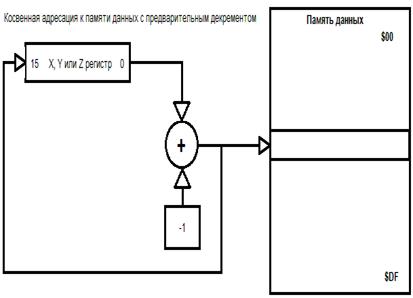

Косвенная адресация к памяти данных с предварительным декрементом. Адрес операнда находится в одном из регистров X, Y или Z. Перед выполнением операции он уменьшается на 1.

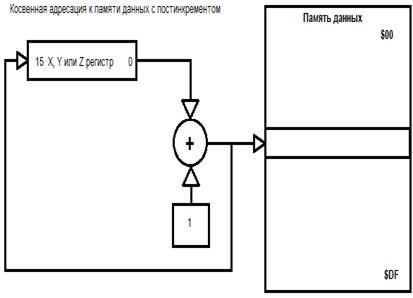

Косвенная адресация к памяти данных с постинкрементом. Адрес операнда находится в одном из регистров X, Y или Z. После выполнение операции он увеличивается на 1.

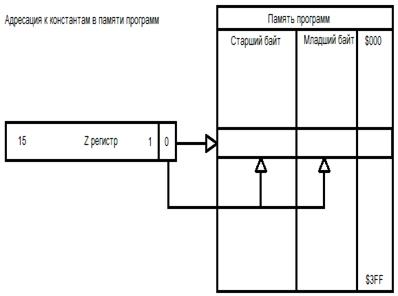

Адресация к константам в памяти программ. Константа в регистре Z. 15 старших битов определяют адрес слова, а младший (0) бит задают младший (если 0) или старший (если 1) байт константы в памяти программ.

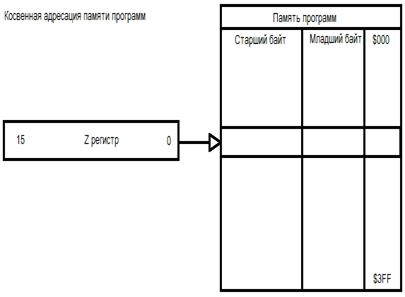

Косвенная адресация памяти программ. После операций IJMP или ICALL выполнение программы продолжается с адреса записанного в регистре Z. Его содержимое переносится в счетчик команд.

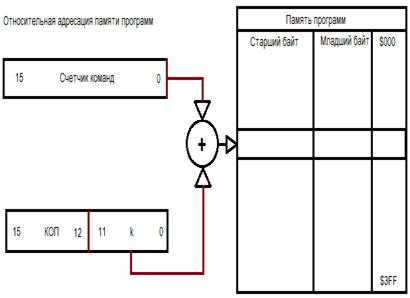

Относительная адресация памяти программ. После операций RJMP или RCALL выполнение программы продолжается с адреса (Счетчик команд)+k+1. Относительный адрес k = -2048…2047

Память программ. Содержит 2 Кб флэш-памяти. Она организована как 1Кх16. Может перепрограммироваться до 1000 раз.. Программный счетчик имеет 10 разрядов и может адресовать 1024 слов памяти программ. EEPROM память данных. Содержит 128 байтов электрически стираемой энергонезависимой памяти (EEPROM). Организована как отдельная область данных, каждый байт которой может быть прочитан и при необходимости переписан. Выдерживает не менее 100000 циклов записи/стирания. К этой памяти может обращаться программа. Данные а нее можно занести с помощью внешнего программатора. Оперативная память данных включает 224 ячейки: регистровый файл (32 адреса), память ввода/вывода (64 адреса), оперативная память данных (128 адресов).

Ассемблер Ассемблер преобразовывает (транслирует) исходные файлы ассемблера в объектные файлы в машинном коде. Эти файлы находятся в общем формате объектного файла (COFF). Исходные файлы могут содержать следующие инструкции ассемблера: · Директивы Ассемблера. · Макро директивы. · Команды ассемблера. · Формат инструкций исходника Компилятор работает с исходными файлами, содержащими инструкции, метки и директивы. Инструкции и директивы, как правило, имеют один или несколько операндов. Строка кода не должна быть длиннее 120 символов. Строка ассемблерного кода завершается символом Enter. Строка содержит поля, разделенные пробелами. Строка может иметь одну из 4 форм: · [метка:] директива [операнды] [Комментарий] · [метка:] инструкция [операнды] [Комментарий] · Комментарий · Пустая строка Позиции, указанные в квадратных скобках, необязательны. Ассемблер не различает регистр символов. Любая строка может начинаться с метки, которая является набором символов, заканчивающимся двоеточием. Метки используются для указания места, в которое передаётся управление при переходах, а также для задания имён переменных. Операнды разделяются запятыми (без пробелов). Текст после точки с запятой (;) и до конца строки – это комментерий. Он игнорируется компилятором. Комментарий имеет следующую форму: ; [Текст] Компилятор не требует, чтобы метки, директивы, комментарии или инструкции находились в определённой колонке строки.

Примеры: label:.EQU var1=100; Устанавливает var1=100 (это помеченная директива). .EQU var2=200; Устанавливает var2=200 (это директива). ; Строка с одним только комментарием Команды ассемблера Операнды в командах могут быть таких видов: · Rd: Результирующий (и исходный) регистр в регистровом файле · Rr: Исходный регистр в регистровом файле · b: Константа (3 бита), может быть константное выражение · s: Константа (3 бита), может быть константное выражение · P: Константа (5-6 бит), может быть константное выражение · K6; Константа (6 бит), может быть константное выражение · K8: Константа (8 бит), может быть константное выражение · k: Константа (размер зависит от инструкции), может быть константное выражение · q: Константа (6 бит), может быть константное выражение · Rdl:═ R24, R26, R28, R30. Для инструкций ADIW и SBIW · X,Y,Z: Регистры косвенной адресации (X=R27:R26, Y=R29:R28, Z=R31:R30) Используемые обозначения:

|

||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 138; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.221.154.151 (0.044 с.) |