Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Универсальные сапр, поддерживающие проектирование плисСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

В первую очередь здесь необходимо отметить САПР ведущих фирм, ориентированных на весь класс электронных устройств. Это САПР таких фирм, как Synopsys, Cadence и Mentor Graphics. Эти САПР, имея соглашения с фирмами, производящими чипы БИС, подключают модули нижнего уровня в свои САПР, что позволяет пользователям этих САПР проектировать различные устройства в единой системе. Достоинством таких САПР является то, что они поддерживают своими средствами множество типов кристаллов разных производителей (например, САПР Cadence поддерживает проектирование кристаллов Xilinx, Altera, AMD, Actel и др.). Недостатком данных САПР является их высокая стоимость и работа только на платформе рабочих станций (UNIX платформа). К работающим на РС платформе в данном классе САПР можно отнести (с определенной натяжкой) только лишь САПР фирмы MicroSim (Design Lab). САПР Design Lab, кроме проектирования кристаллов основных фирм разработчиков ПЛИС (Xilinx, Altera, Actel), позволяет проектировать аналоговые и смешанные схемы, разрабатывать печатные платы и др. С некоторой условностью к этому же классу САПР можно отнести и программы фирмы OrCAD, так как в последние годы фирма пытается расширить возможности своей САПР, добавляя к традиционно сильным своим модулям ввода схем и логического моделирования модули проектирования печатных плат и др. К САПР, покрывающим большинство этапов проектирования ПЛИС разных фирм-производителей, можно отнести и программы фирмы ISDATA, решающие большинство задач, характерных при проектировании ПЛИС, от ввода схем до подготовки файла загрузки. Работают эти программы как на РС, так и на платформе рабочих станций.

САПР Synopsys Компания Synopsys Inc. является одним из мировых лидеров по разработке программных средств автоматизации проектирования (EDA) полупроводниковых устройств. Компания занимается разработкой, поддержкой и маркетингом систем автоматического моделирования высокого уровня, программного обеспечения для проектирования интегральных схем и электронных систем. Компания является основоположником коммерческой реализации технологии синтеза, предлагает исчерпывающий набор синтезаторов, эмуляторов, тестов и опробованных решений, которые поддерживают Verilog HDL и VHDL стандарты. Важно также отметить, что Synopsys выпускает передовые платформы для проектирования и верификации, позволяющие выполнять разработку сложных SoC (система на кристалле) проектов.

Основанная под названием Optimal Solutions в 1986 доктором Артом де Джисом (Aart de Geus) и командой инженеров из Центра Микроэлектроники компании General Electric в Северной Каролине, компания Synopsys была призвана развивать и продавать технологию синтеза, разработанную коллективом компании General Electric. В течение последних почти 20 лет из небольшой компании, занимавшейся разработкой одного продукта, компания Synopsys превратилась в разноплановую компанию, являющуюся лидером технологии средств проектирования ИС и предлагающую полный набор решений от концепции до изготовления в кремнии. За это время компанией Synopsys были предложены и продвинуты решения в области логического синтеза, которые сейчас приняты практически всеми крупными электронными компаниями в мире. В течение всего периода развития Synopsys наращивал свою стратегию разработки технологии путем добавления к своим внутренним продуктам технологий, полученных в результате приобретения новых компаний и объединения с другими компаниями. В частности, в 2004 компания Synopsys приобрела компанию Integrated Systems Engineering AG (ISE) (разработчик программной платформы Technology CAD); компанию Cascade Semiconductor Solutions, Inc (поставка цифровых IP блоков); компанию Accelerant Networks (IP-cores); значительные активы компании Analog Design Automation, Inc, (разработка решений в области автоматической оптимизации аналоговых, смешанных и заказных интегральных схем). Продукты компании Synopsys охватывают весь цикл проектирования, давая проектировщикам возможность использования лучшей на сегодняшний день интегрированной технологии, начиная от спецификации проекта и заканчивая его изготовлением в кремнии. Основными направлениями разработки и поддержки программного обеспечения компании Synopsys являются две платформы: Galaxy (платформа проектирования) и Discovery (платформа верификации). Эти платформы обеспечивают интегрированный набор инструментов, использующих современные подходы для проектирования и верификации ИС. Список решений Synopsys в рамках этих платформ включает: · создание системы;

Структура платформ Galaxy и Discovery показана на рис.2.2.

Платформа Galaxy. Цель проектирования – реализация физического проекта БИС. Технология проектирования на этой платформе базируется на следующих модулях: системного проектирования Design Compiler, планирования кристалла БИС JupiterXT, физического компилятора Astro, модуле верификации, средствах статистического анализа PrimeTime SI, базе данных MilkyWay. Module Compiler – это средство синтеза модулей трактов обработки данных, дающее возможность использовать различные структуры трактов обработки данных для достижения оптимальной реализации своих проектов. JupiterXT – это инструмент для иерархического планирования кристалла (floorplan), решает проблемы проектирования систем на кристалле (количество эквивалентных вентилей превышает миллиард). Работа JupiterXT основана на использовании базы данных MilkyWay.

Рисунок 2.2 - Структура платформ Galaxy и Discovery

Astro – это современная система проектирования на физическом уровне для размещения, трассировки и оптимизации топологии. В рамках решения задач физической компиляции проекта возможно подключение таких программных модулей, как Astro-Rail, обеспечивающего решение задач анализа энергопотребления (шин питания), падения напряжения питания и эффектов электромиграции для проектов, реализуемых под UDSM (Ultra Density System Manufacturing) технологии, и Astro-Xtalk – опцию, предназначенную для анализа и коррекции взаимовлияния проводников (xtalk) для UDSM проектов. Параллельный анализ взаимовлияния проводников с помощью Astro-Xtalk's не только обеспечивает раннее выявление проблем целостности данных, но и управляет процессом физического проектирования таким образом, чтобы любое действие предотвращения/коррекции взаимовлияния не создало других проблем взаимовлияния проводников где-либо еще. Astro-Xtalk является частью решения Synopsys SinglePass-SoC, основанной на базе данных MilkyWay. Конечным результатом работы физического компилятора является физический проект без проблем взаимовлияния проводников и с достигнутыми параметрами быстродействия. Модуль верификации включает в свой состав программные решения для проверки физического проекта. К этим решениям относятся: экстрактор Star-RCXT – пакет промышленного стандарта для извлечения значений паразитных емкостей и сопротивлений для UDSM технологий (90-нанометров и ниже); тестер TetraMAX ATPG – средство автоматизированного создания тестовых наборов для производственных тестов контроля годности СБИС; семейство тестеров Hercules – комплекс программных инструментов для проверки правил физического проектирования: DRC, ERC, LVS. Это программное решение дает возможность работать с использованием таких технологий, как распределенная обработка заданий на нескольких рабочих станциях или серверах, а также в условиях мультипроцессорной обработки заданий. В состав семейства Hercules входят пакеты Hercules DRC, Hercules ERC, Hercules LVS и Hercules Explorer, полностью закрывающие задачи анализа результатов физической верификации. Семейство Hercules работает с проектами на уровне транзисторов и примитивов, обеспечивая физическую верификацию как для цифровых, так и для аналоговых и смешанных проектов. Пакет Hercules является промышленным стандартом для подавляющего числа производителей СБИС.

PrimeTime SI – это инструмент временнóго статического анализа вентильных схем. Способен работать с проектами размером до 100 млн. вентилей. PrimeTime является комплексным инструментом, сочетающим в себе временной статический анализ, точный расчет RC параметров и генерацию временных моделей. Данный инструмент стал промышленным стандартом временного статического анализа практически для всех производителей кристаллов. MilkyWay – база данных проектов, представляющая собой общее для всех инструментов, входящих в платформу проектирования Galaxy, хранилище данных проекта. Такой подход позволяет, во-первых, осуществить бесшовное взаимодействие между различными инструментами проектирования и верификации СБИС и, во-вторых, исключить временные задержки и несоответствия, связанные с обновлением различных представлений проекта в единой базе данных различными инструментами платформы Galaxy. Естественным является наличие интерфейсов для ввода/вывода данных проекта в стандартных форматах представления (Verilog, VHDL и др.), а также наличие интерфейса обмена данными с инструментами проектирования других компаний через API. Кроме перечисленных выше модулей, к платформе Galaxy, в зависимости от класса проектируемых изделий, могут быть подключены библиотеки IP блоков DesignWare, предоставляющие разработчикам широкий набор IP блоков различной номенклатуры. Платформа Discovery. Эта платформа представляет собой комплексное решение для верификации СБИС на системном, регистровом и смешанном уровнях с возможностью проверки эквивалентности описаний. Комплекс обеспечивает высокую производительность и эффективное взаимодействие лучших в своем классе технологий, включающих многоязыковое HDL моделирование, смешанное (mixed-signal) моделирование, верификацию на системном уровне, формальные утверждения (assertions), IP блоки для верификации, анализ покрытия кода, анализ функционального покрытия, создание тестирующих моделей и статический формальный анализ. Компоненты платформы поддерживают проекты, представленные на языках Verilog, VHDL, SystemVerilog, SystemC, а также многоязычные, аналоговые и смешанные проекты. Особенностью платформы является встроенная поддержка промышленных стандартов. Работа на платформе Discovery ведется с использованием следующих модулей: проектирования на системном уровне (модули System Studio и Saber), интеллектуальной верификации на регистровом уровне (программные решения VCS и VCS MX, Vera, Leda и Magellan), проверки функциональной эквивалентности (Formality и Formality ESP, а также программный модуль ESP-CV) и смешанной верификации (NanoSim, HSpice, Cosmos и Discovery AMS). Работа платформы поддерживается базами стандартных моделей процессоров и шин SystemVerilog/SystemC и верификационных моделей IP-ядер DesignWare Verification Library.

Модуль System Studio является мощным инструментом для проектирования на системном уровне, используемым преимущественно в двух критически важных областях проектирования для передовых систем на кристалле (SoC): разработка алгоритмов и разработка архитектур. Разработка алгоритмов охватывает обработку сигналов в таких приложениях, как беспроводная телефония, мультимедийные кодеки, DSL и кабельные модемы. Разработка архитектуры включает объединение требуемых процессоров, логических схем, шин, блоков памяти и периферийных устройств с целью получения наибольшей эффективности использования системы. Программный модуль Saber представляет собой средство для моделирования и анализа, поддерживающее несколько технологий и используемое для системного проектирования в таких отраслях, как автомобилестроение, авиакосмическая промышленность и энергетика. Интеллектуальная верификация на регистровом уровне реализуется на базе использования программных решений VCS и VCS MX (средства моделирования со встроенной, всесторонней поддержкой формальных утверждений и анализа их покрытия, тестирующих моделей и анализа покрытия кода, реализующее эффективную методологию «проектирования для верификации» (DFV)), Vera (инструмент для создания автоматизированных тестирующих моделей, использующий такие концепции, как генерация случайных воздействий с ограничениями, генерация данных в реальном времени и временные проверки, расширенный анализ функционального покрытия), Leda (программируемый инструмент для проверки описаний проектов регистрового и вентильного уровней на соответствие заданному стандарту кодирования) и Magellan (гибридное средство для верификации описаний RTL проектов). Formality и Formality ESP представляют собой инструмент для проверки функциональной эквивалентности, использующий технику статического формального сравнения для доказательства или опровержения функциональной эквивалентности двух представлений одного и того же проекта и дающий возможность проверки функциональной эквивалентности между Verilog моделями, предназначенными для моделирования и библиотечными элементами в формате SPICE, макросами трактов данных и встроенными блоками памяти. Программное решение ESP-CV является инструментом для функциональной верификации полностью заказных (full custom) проектов. Для поддержки смешанных проектов (заказных цифровых схем, схем памяти, смешанных и аналоговых схем) платформа Dyscovery предлагает ряд программных решений, таких как NanoSim (инструмент моделирования и анализа схем на транзисторном уровне, предназначенный для верификации аналоговых, цифровых и смешанных проектов), HSpice (моделирование схем высокой точности на уровне транзисторов, объединяющее достоверные модели c алгоритмами моделирования и анализа по таким характеристикам проекта, как временные показатели, потребляемая мощность и функциональные возможности), Cosmos (высокопроизводительное средство автоматизации схемных проектов) и Discovery AMS (интегрированный комплекс средств верификации проектов смешанного типа на основе общего интерфейса и совмещенных моделей).

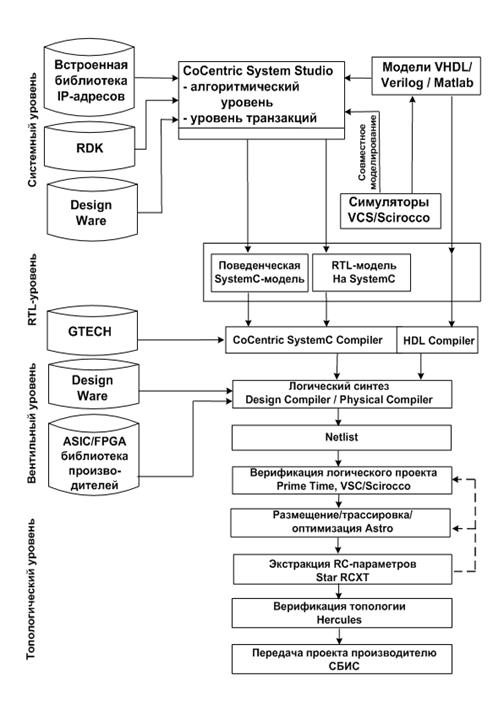

На системном уровне разработка происходит в среде CoCentric System Studio. Этот уровень включает два подуровня – функциональный подуровень и подуровень транзакций. На функциональном подуровне (уровне алгоритмов) создается и верифицируется математическая модель системы в целом. На подуровне транзакций можно моделировать архитектуру системы. Причем для разработки моделей используется ставший фактически промышленным стандартом язык SystemC. Очень важно, что уже на системном уровне CoCentric System Studio позволяет совместно моделировать аппаратную и программную части системы, определять их оптимальное соотношение. Верификация встраиваемого ПО в среде CoCentric System Studio может происходить совместно с верификацией системной модели аппаратной части. Кроме SystemC на системном уровне можно использовать модели на языках С/С++, Verilog, VHDL, Matlab, а также задействовать уже готовые IP блоки.

Рисунок 2.3 - Маршрут проектирования СБИС Для моделирования Verilog и VHDL кодов предназначены симуляторы VCS и Scirocco соответственно. Это позволяет, в частности, разработав системную модель сложного устройства, довести отдельный его блок до вентильного и даже до топологического уровня и верифицировать системную модель, используя уже готовый блок. В этом случае может выясниться, например, что какие-либо параметры, заложенные в блок на системном уровне, не реализуются, и тогда можно изменить саму систему. Для перехода с системного уровня к непосредственному проектированию СБИС необходимо описание проекта на уровне регистровых передач (RTL). Переход от системной модели к RTL возможен двумя путями. Традиционный подход – это вручную писать соответствующий код на языках Verilog/VHDL. Описывать RTL модели позволяет и SystemC, причем для этого не надо заново переписывать код – достаточно лишь дополнить существующее описание определенными конструкциями. Другой подход, предоставляемый CoCentric System Studio, – это генерация так называемой поведенческой модели на SystemC (синтезабельный код SystemC). При этом формируется некая модель в виде "черного ящика", у которой определены интерфейсы, временные характеристики, выполняемые функции, однако внутренняя структура не детализирована. Особенностью Synopsys является то, что из такой модели можно синтезировать логическое описание проекта. Иными словами, система сама синтезирует внутреннюю микроархитектуру СБИС. Для этого предназначен CoCentric SystemC Compiler, который формирует список цепей (netlist) в базисе внутренней библиотеки элементов Synopsys (библиотека GTECH). Технология логического синтеза на основе поведенческой RTL модели позволяет быстро получить ответ на вопрос: реализуема ли в принципе та или иная система и какие аппаратные ресурсы СБИС (число вентилей, площадь кристалла, энергопотребление, частотные характеристики и т.д.) для этого нужны. Причем синтезируемые CoCentric SystemC Compiler структуры если и превышают по числу вентилей разработанные вручную, то в среднем не более чем на 10%. Отметим, что процесс разработки и верификации системных моделей существенно упрощают и ускоряют различные библиотеки системного и RTL уровней. Основные из них – это Design Ware и Reference Design Kit (RDK). Библиотека Design Ware не имеет аналогов на рынке средств САПР благодаря уникальному набору функциональных параметризируемых блоков (от арифметических устройств до микропроцессорных ядер). RDK представляет собой набор системных моделей множества стандартов и протоколов – в области проводной и беспроводной связи, шинных интерфейсов и т.д. Он удобен, например, при разработке коммуникационного процессора для системы GSM, а модели всего стека GSM протоколов для верификации модели этой СБИС можно взять из RDK. За RTL следует вентильный уровень. Для работы на нем предназначено семейство продуктов Design Compiler. Эти продукты занимают на рынке долю около 80%, и фактически Design Compiler стал промышленным стандартом. Он представлен в двух версиях: стандартной – Design Compiler Expert и расширенной – Design Compiler Ultra. С Design Compiler стыкуются различные дополнительные инструменты. Например, DFT Compiler формирует аппаратные средства контролепригодности синтезируемой структуры, Power Compiler позволяет оптимизировать схему с точки зрения энергопотребления и т.д. Отметим, что готовые блоки и библиотечные элементы не транслируются повторно, а в Design Compiler передаются указатели на них. Design Compiler оптимален для технологии до 0,25–0,18 мкм. На технологиях следующего уровня, с разрешением менее 0,18 мкм, начинают проявляться более тонкие физические эффекты. Для работы на этих глубокосубмикронных уровнях предназначен Physical Compiler. В отличие от Design Compiler, этот инструмент использует библиотеки топологического уровня и синтезирует не только список цепей, но и реальное размещение элементов на кристалле. Получив размещение, можно с точностью до 5–10% оценить длину связей между элементами и по значениям их емкостей и сопротивлений определить времена задержек распространения сигналов в цепях. Очень важно, что выходной формат Design Compiler и Physical Compiler стандартны: netlist – на языках Verilog или VHDL, описание размещения элементов – в универсальных форматах pdef, def, LEF, которые понятны продуктам других компаний. Таким образом, Physical Compiler можно использовать в маршрутах проектирования, например, компании Cadence. Для работы с ПЛИС предназначен стыкуемый с Design Compiler инструмент FPGA Compiler II Add On, который включает библиотеки около 80 производителей (Altera, Xilinx, Actel, Atmel, Motorola, Intel, Lattice и т.д.). Компания Synopsys позиционирует ПЛИС как средство аппаратной верификации. Именно поэтому разработку и ПЛИС, и заказной СБИС можно проводить в единой среде Design Compiler. По завершении логического синтеза необходимо провести верификацию проекта. Для анализа временных статических характеристик предназначен пакет Prime Time. Это также весьма распространенный на рынке продукт. Он позволяет получить адекватное представление о поведении схемы, проанализировать его в наилучших и наихудших случаях, обнаружить скрытые ошибки. У этого продукта есть расширение – Prime Time SI, предназначенное для анализа топологии. Оно позволяет отслеживать взаимовлияние проводников. Для синтеза топологии служит инструмент Astro. Он предназначен для решения задач размещения, трассировки и оптимизации топологии. При размещении и трассировке учитывается влияние взаимных помех между отдельными проводниками и фрагментами схемы (например, можно запретить вести длинные связи в одном слое, размещать рядом мощные буферные элементы и т.д.). Astro позволяет учитывать влияние физических эффектов, проявляющихся при технологическом разрешении меньше 0,18 мкм. Предусмотрена и защита от так называемого антенного эффекта, возникающего на стадии производства, когда остаточный заряд формирующегося проводника способен повредить уже подсоединенный к нему вентиль. Для борьбы с подобными явлениями предусмотрены определенные меры, например, разбиение длинного проводника на несколько коротких в разных слоях, введение защитного диода и т.д. Astro позволяет определить те места, где антенный эффект может проявиться. На выходе Astro получается готовая топология кристалла в формате gds2. Однако ее надо проверить, прежде всего – на паразитные RC параметры. Для экстракции RC параметров из уже готовой топологии предназначен инструмент Star RCXT. Полученные с его помощью RC характеристики реальной топологии можно проанализировать с помощью того же Astro или Prime Time SI. Кроме анализа временных параметров, проверяется соблюдение правил проектирования (DRC) и правильности электрической схемы (ERC), т.е. правильность соединений, наличие несоединенных входов/выходов и т.п. Третья составляющая проверки топологии – восстановление из нее списка цепей и сравнение с исходным netlist (LVS). Все эти проверки реализует инструмент Hercules.

Информационные источники, использованные при подготовке раздела:

САПР Cadence В целом проектирование БИС в среде Cadence, реализуемое сегодня на платформе Virtuoso, включает этапы, изображенные на рисунке 2.4. • системное проектирование – построение модели системы на высоком уровне абстракции с использованием языков программирования C/C++ и SystemC, разбиение на программные и аппаратные модули, исследование параметров системы, получение спецификаций (набора требуемых параметров) на программные и аппаратные блоки; • аппаратное проектирование и верификация – разработка на основе спецификации поведенческих моделей отдельных блоков системы с использованием языков Verilog/VHDL, реализация проекта в базисе библиотек производителя ИС, проверка программно-аппаратной реализации на соответствие спецификациям, полученным на системном уровне;

Рисунок 2.4- Этапы проектирования БИС в среде Cadence

• физическое прототипирование – предварительное размещение элементов, оценка потребляемой мощности, планирование шин питания и иерархии тактовых сигналов, качественная оценка возможных искажений сигнала; • проектирование и верификация топологии кристалла – разработка топологии заказных блоков, трассировка на уровне ячеек, проверка правил проектирования топологии, экстракция паразитных параметров.

Информационные источники, использованные при подготовке раздела:

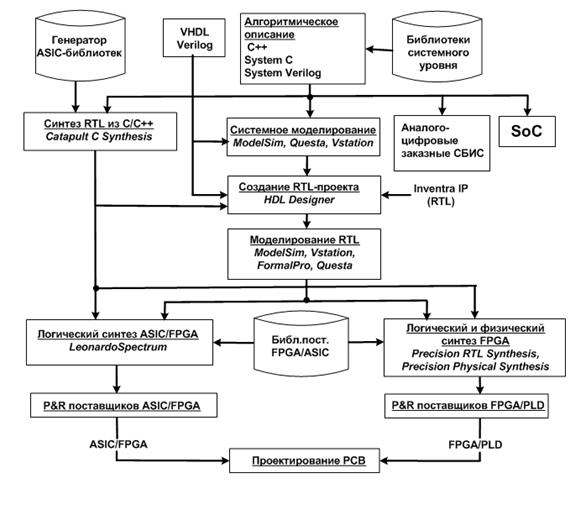

САПР Mentor Graphics Комплексное проектирование систем на базе PLD/FPGA/ASIC схем реализуется в среде САПР Mentor Graphics в соответствии со схемой (рис.2.5): Из приведенной схемы можно выделить базовые программные решения, используемые Mentor Graphics при проектировании БИС: · HDL Designer – комплексное средство графического и текстового ввода проектов многомиллионных кристаллов FPGA/ASIC/SoC/FPSoC на основе языков VHDL, Verilog и их “смеси”, управления процессом проектирования и выпуска документации. Поддерживает концепции коллективного проектирования, в том числе с возможностью дистанционного доступа через Intranet или Internet, повторного использования стандартных решений (IP-blocks) и многовариантного проектирования;

Рисунок 2.5 - Комплексное проектирование систем на базе PLD/FPGA/ASIC схем в среде САПР Mentor Graphics · ModelSim – система цифрового моделирования проектов на основе VHDL, Verilog и “смешанных” описаний с встроенными функциями анализа производительности, индикации “активности” кода (code coverage), компаратора временных диаграмм и визуализатора Enhanced Dataflow Window. Основные функциональные возможности: высокая скорость моделирования для RTL и Gate проектов; единое моделирующее ядро и оптимизированная архитектура Native Compiled; интерактивная отладка и анализ с помощью модуля Debug Detective; интегрированный анализ Code Coverage; оптимизация скорости моделирования с помощью анализатора производительности Performance Analyzer; исчерпывающая трассировка сигналов Signal Spy; встроенный отладчик C; поддержка интерфейсов C и Tcl/Tk; поддержка ОС Unix/Windows/Linux; · Leonardo Spectrum – пакет логического синтеза и оптимизации CPLD/FPGA/ASIC на основе VHDL, Verilog и “смешанных” описаний проектов на базе библиотек всех ведущих изготовителей (более 100). Основные функциональные возможности: единая среда для проектирования CPLD, FPGA и ASIC; поддержка проектов, использующих любую комбинацию VHDL, Verilog и EDIF и стандартных решений в виде IP-блоков; высокое качество результатов (QoR) в сочетании с высокой скоростью синтеза; возможность генерации оптимизированного HDL-кода с помощью модуля HDLInventor; использование оптимизирующего алгоритма F.A.S.T.; полная интеграция со средствами размещения и траcсировки изготовителей кристаллов (P&R Integrator); усовершенствованные отладочные возможности схемотехнического браузера LeonardoInsight; · Precision Synthesis RTL – пакетлогического синтеза, оптимизированный для FPGA. Высокая скорость синтеза и простота использования. Практически не требует ручной настройки (работа по принципу “нажал кнопку – получил результат”). Высокое качество результатов с первого прохода. Оптимизация временных параметров (до 30%). Полностью интегрирован с HDL Designer, ModelSim, LeonardoSpectrum, FPGA Advantage; · Precision Physical Synthesis -пакет физического синтеза, ориентированный на оптимизированные, с точки зрения производительности, FPGA-проекты. В отличие от традиционного подхода RTL Synthesis + P&R, как правило, требующего большого числа итераций, Precision Physical реализует временную оптимизацию на этапе синтеза на основе конкретных физических параметров библиотек изготовителей, что позволяет сократить или полностью исключить необходимость повторных итераций размещения и трассировки; · Catapult C Synthesis -пакет поведенческого синтеза, позволяющий получить синтезируемое RTL-описание проекта (VHDL или Verilog) на основе входного функционального описания на С или С++. Основное отличие от других маршрутов проектирования верхнего уровня (например, на основе MATLAB, System C, Handle C и других) состоит в том, что Catapult C не требует никаких промежуточных представлений (System C, Handle C), а непосредственно синтезирует исходный С-код в том виде, в котором он был написан инженером-системщиком, что существенно сокращает цикл проектирования. При этом результат зависит не от исходного кода, а от тех ограничений и настроек, которые выполняются непосредственно в Catapult C; · FPGA Advantage (HDL Designer + ModelSim + Leonardo Spectrum/Precision Synthesis) – комплекс, включающий все модули маршрута проектирования CPLD/FPGA/ASIC. Оптимальное решение по стоимости. Информационные источники, использованные при подготовке раздела:

|

|||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 1104; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.137.211.49 (0.012 с.) |

Маршрут проектирования СБИС (рис.2.3), базирующийся на описанных платформах, включает системный уровень (разработка и отладка системы на функциональном уровне и уровне транзакций, отработка ТЗ системы как для аппаратной, так и для программной ее частей, совместная верификация ПО и аппаратуры), уровень регистровых передач RTL (разработка синтезируемого описания аппаратной части СБИС), вентильный уровень (разработка логического проекта СБИС) и топологический уровень (разработка топологического проекта).

Маршрут проектирования СБИС (рис.2.3), базирующийся на описанных платформах, включает системный уровень (разработка и отладка системы на функциональном уровне и уровне транзакций, отработка ТЗ системы как для аппаратной, так и для программной ее частей, совместная верификация ПО и аппаратуры), уровень регистровых передач RTL (разработка синтезируемого описания аппаратной части СБИС), вентильный уровень (разработка логического проекта СБИС) и топологический уровень (разработка топологического проекта).

Отметим, что средства, предназначенные для работы на топологическом уровне, – Astro, Hercules, Star RCXT и т.д. – вошли в состав системы Synopsys после слияния этой компании с фирмой Avant! От нее же к Synopsys перешла и база данных MilkyWay, позволяющая работать с описанием проекта одновременно нескольким инженерам. Причем все изменения вносятся только в одну рабочую версию (разумеется, предусмотрено сохранение предыдущих версий), что исключает ситуацию, когда по ошибке в работе оказываются несколько копий проекта. В MilkyWay проекты хранятся во внутреннем закрытом представлении, что исключает возможность какого-либо непредусмотренного вмешательства в проект. Недостаток этой базы данных: она совместима только с инструментами компании Avant!. Однако сейчас эта проблема находится в стадии разрешения.

Отметим, что средства, предназначенные для работы на топологическом уровне, – Astro, Hercules, Star RCXT и т.д. – вошли в состав системы Synopsys после слияния этой компании с фирмой Avant! От нее же к Synopsys перешла и база данных MilkyWay, позволяющая работать с описанием проекта одновременно нескольким инженерам. Причем все изменения вносятся только в одну рабочую версию (разумеется, предусмотрено сохранение предыдущих версий), что исключает ситуацию, когда по ошибке в работе оказываются несколько копий проекта. В MilkyWay проекты хранятся во внутреннем закрытом представлении, что исключает возможность какого-либо непредусмотренного вмешательства в проект. Недостаток этой базы данных: она совместима только с инструментами компании Avant!. Однако сейчас эта проблема находится в стадии разрешения.