Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Элементы эмиттерно – связанной логики (ЭСЛ).Содержание книги Поиск на нашем сайте

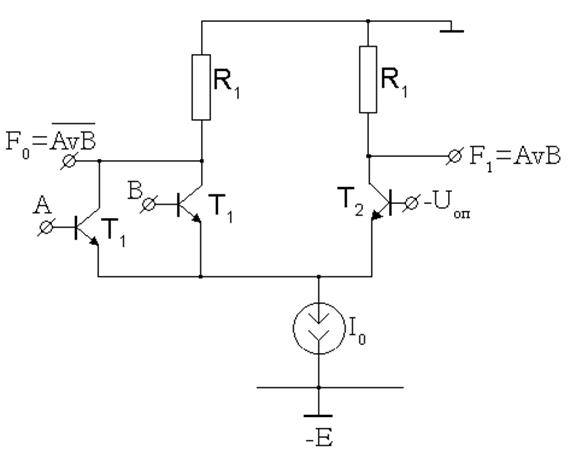

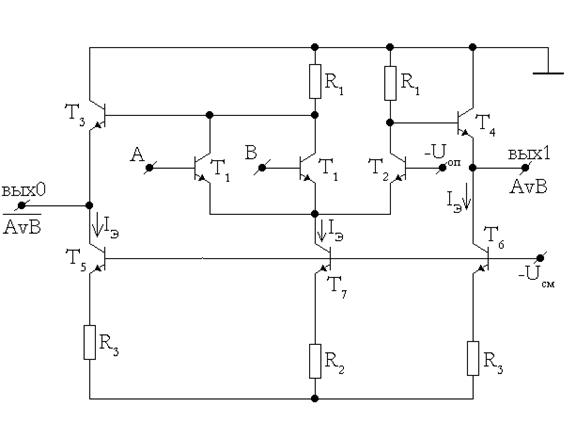

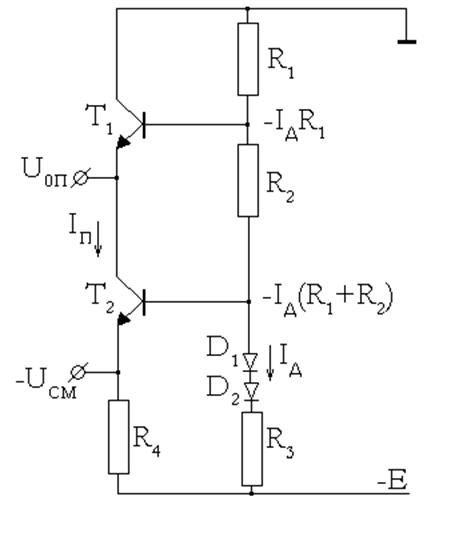

Элементы эмиттерно – связанной логики (ЭСЛ). ЭСЛ – элементы отличаются высоким быстродействием (t3≤1 нс) и поэтому они являются в настоящее время основной элементной базой высокопроизводительных ЭВМ. Основой ЭСЛ – элементов является переключателем тока (токовые ключи).

Принцип действия переключателя тока.

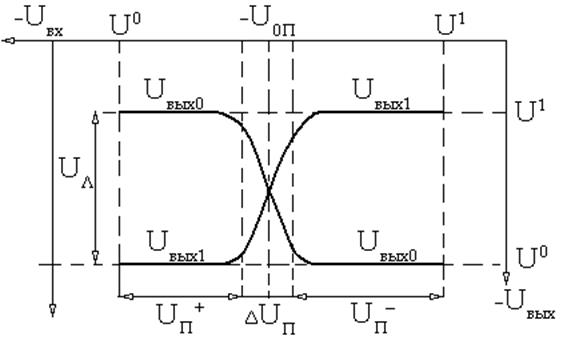

U0,U1<0, U0<U1, т.о. |U0|>|U1|. Пусть хотя бы на один вход подан высокий потенциал Uвх>-Uоп, тогда соотв. Т1 открыт, вычислим напряжение БЭ транзистора Т2: Uбэ2=-Uоп-Uэ=-Uоп-(Uвх-U*)=U*-(Uоп+Uвх)<U* Uэ=Uвх-U* – потенциал эмиттеров. Следовательно Т2 закрыт, ток источника тока I0 протекает через входное плечо переключателя тока, на входе F0 устанавливается низкий потенциал U0=-I0R1 , в правом “опорном” плече ток не течет и на выходе. F1 потенциал равен 0 U1=0. Если на все переключатели тока подан низкий потенциал Uвх<-Uоп, то транзисторы Т1 закрыты, Т2 открыт и на выходе F0-U1, на F1-U0.

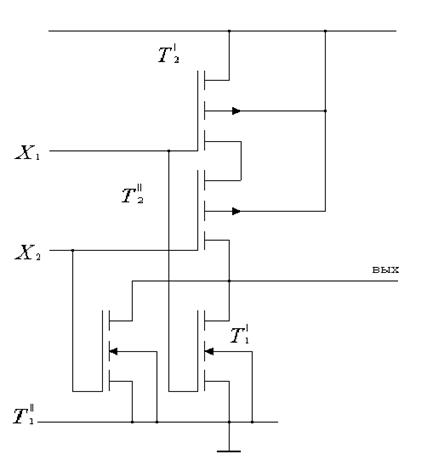

Базовый элемент ЭСЛ.

В этом случае Т2 открыт и через R1 в его коллекторе цепи течет ток На выходе 1 – низкий потенциал

Ограничение на максимум логического перепада

Входные токи: при Макс ток нагрузки

Мощность

ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ И НАПРЯЖЕНИЯ СМЕЩЕНИЯ.

Чтобы:

Пусть

Т.К. Снижение от

Пусть

Средняя задержка переключения:

Энергия переключения:

КМОП

В схемах данного типа используются как n-канальные, так и p-канальные МДП транзисторы. Это позволяет создать логические схемы, практически не потребляющие мощность в статическом режиме. У таких схем потребляемая мощность на низких и средних частотах на 2-3 порядка меньше, чем у ТТЛ схем, а задержка примерно такая же. Эти схемы применяются при наличии ограничений на потребляемую мощность из-за ограниченных энергоресурсов или жестких требований к тепловому режиму. Однако они технологически сложнее и занимают большую площадь на кристалле.

Инвертор

Пусть Пусть Пусть Когда

Рис. 37. Принципиальная схема КМОП инвертора

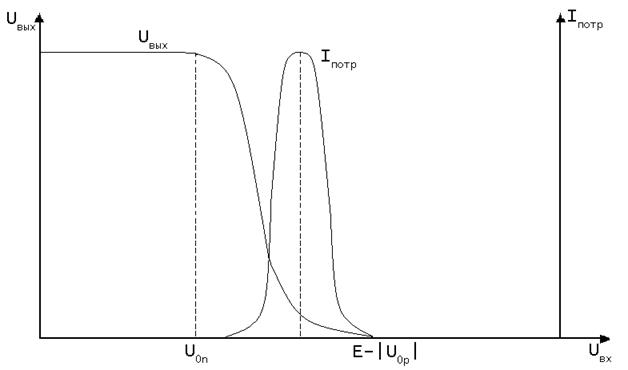

Рис. 38. Передаточная характеристика

Рис. 39. Структура КМОП инвертора

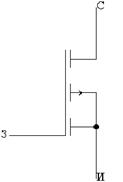

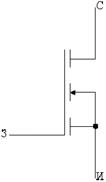

Рис. 40. Обозначения транзисторов

Как правило, к выходу логической схемы подключается вход такой же логической схемы, поэтому в статике ток в КМОП схеме может течь только через транзисторы (вход следующей схемы – затворы её транзисторов, через них ток не течёт): когда на выходе логический 0, заперт когда на выходе логическая 1, заперт Требования к транзисторам КМОП схем: 1. В КМОП схемах должно соблюдаться равенство по модулю пороговых напряжений n- и p-канальных транзисторов 2. Необходимо равенство удельной крутизны n- и p-канальных транзисторов, из-за чего отношение ширины n- и p-канальных транзисторов пропорционально отношению подвижности электронов и дырок (при равной длине канала). Схема ИЛИ-НЕ

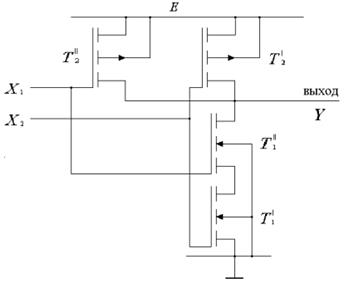

Рис. 41. Схема ИЛИ-НЕ Схема И-НЕ

Рис. 42. Схема И-НЕ

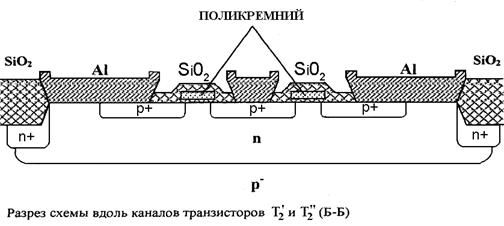

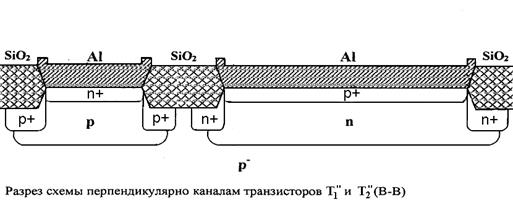

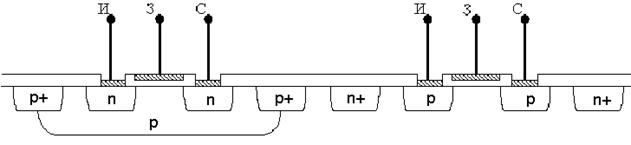

Рис. 43. Сечение структуры

Рис. 44. Сечение структуры

Рис. 45. Сечение структуры

Рис. 46. Топология схемы И-НЕ

Проектирование КМОП схем. Рекомендуется длину канала транзисторов обоих типов выбрать равной двум минимальным размерам, ширину канала n-канального транзистора выбрать в 3 раза больше длины (6 минимальных размеров), тогда ширина канала p-канального транзистора будет в 3 раза больше ширины канала n-канального(18 минимальных размеров). Размеры областей стока и истока определяются шириной канала и условиями размещения контактов: контакт занимает всю площадь стока и истока, отступая от их краев на минимальный размер, ширина контакта не может быть меньше минимального размера. Когда геометрические размеры выбраны, делается расчет параметров транзисторов по формулам, приведенным выше, а после этого – расчет схемы с помощью программы PSPICE. Исходя из анализа результатов расчета схемы делаются изменения в размерах транзисторов.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-12; просмотров: 349; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.119.159.212 (0.007 с.) |

и оба Т1 закрыты

и оба Т1 закрыты  ,

,  ,

,  ток нагрузки,

ток нагрузки,  ток источника тока T5-R3, на выходе 0 высокий потенциал

ток источника тока T5-R3, на выходе 0 высокий потенциал

коэффициент передачи тока транзистора.

коэффициент передачи тока транзистора.  , где

, где

. Токи, задаваемые транзисторными источниками тока

. Токи, задаваемые транзисторными источниками тока  ,

, . Когда

. Когда  (хотя бы один) открывается Т1 и закрывается Т2,

(хотя бы один) открывается Т1 и закрывается Т2,  течет через Т1 и

течет через Т1 и

определяется из условия ненасыщенного режима транзисторов Т1:

определяется из условия ненасыщенного режима транзисторов Т1:  . Чтобы Т1 не был насыщен

. Чтобы Т1 не был насыщен  (схемы нагружены друг на друга). В этом режиме

(схемы нагружены друг на друга). В этом режиме  Опорное напряжение:

Опорное напряжение: , где l – число открытых входов (

, где l – число открытых входов ( ). При

). При

определяется исходя из допустимого снижения уровня

определяется исходя из допустимого снижения уровня  при подключении нагрузки:

при подключении нагрузки:  , l=1

, l=1

из условия:

из условия:  - для стабильности

- для стабильности  ; один источник на 5-10 ЭСЛ - элементов.

; один источник на 5-10 ЭСЛ - элементов.

меняется от

меняется от  , транзистор Т1 открывается, потенциал коллектора Т1:

, транзистор Т1 открывается, потенциал коллектора Т1:

- емкости коллекторов Т1 и Т3,

- емкости коллекторов Т1 и Т3,  - паразитная емкость межсоединений.

- паразитная емкость межсоединений.  - емкость нагрузки,

- емкость нагрузки,  - паразитная емкость.

- паразитная емкость. достаточно мала, а емкость нагрузки

достаточно мала, а емкость нагрузки  велика, потенциал

велика, потенциал  не успевает следовать за уменьшением

не успевает следовать за уменьшением  и Т3 запирается, поэтому емкость

и Т3 запирается, поэтому емкость  (ток эмиттерного повторителя).

(ток эмиттерного повторителя).

происходит за время спада

происходит за время спада  ,когда

,когда  напряжение на эмиттерном переходе Т3

напряжение на эмиттерном переходе Т3 и Т3 открывается.

и Т3 открывается. , Т1 запираются и

, Т1 запираются и  . Через открытый Т3 изменения

. Через открытый Т3 изменения  за время нарастания

за время нарастания

.

.

следовательно n-канальный

следовательно n-канальный  тогда

тогда  следовательно p-канальный

следовательно p-канальный  открыт и работает в крутой области выходной характеристики, то

открыт и работает в крутой области выходной характеристики, то  .

. растет, когда

растет, когда  ,

,  , тогда

, тогда  - открыт (

- открыт ( ),

),  - закрыт

- закрыт  , если

, если  и

и  - что то же самое.

- что то же самое. транзистор

транзистор  , запирается и устанавливается

, запирается и устанавливается

пороговое напряжение

пороговое напряжение

,

, Þ

Þ

и

и  оба заперты

оба заперты

и

и  оба открыты

оба открыты