Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Тригер Т- типу ( Т – тригер )Содержание книги

Поиск на нашем сайте

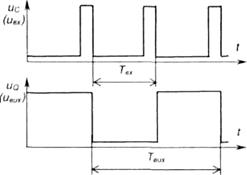

Т - тригер (від англійського to toggle - перекидатись) ще називають тригером поділювачем на два або лічильним тригером.Тригер має тільки один тактовий вхід, а його стан змінюється на протилежний з надходженням на вхід кожного імпульсу. Цей тригер використовують для лічення та ділення частоти імпульсів.

Рисунок 21.7 Умовні позначення та часові діаграми роботи Т- тригера. JK- тригер Синхронний JK- тригер має два інформаційних входи Jі Кта тактовий С. Умовне позначення та таблиця переходів JK-тригера з прямим імпульсним тактовим входом наведені на рис. 21.8. JK

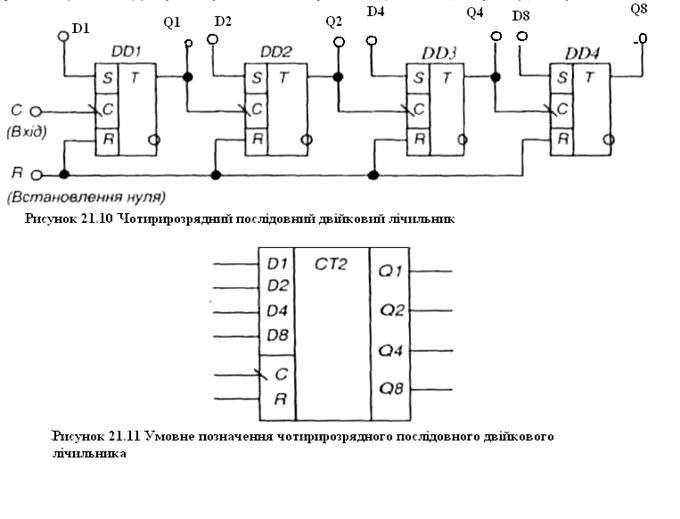

Лічильники імпульсів. Однією з найрозповсюдженіших операцій у пристроях інформаційно-обчислювальної і цифрової вимірювальної техніки є фіксування кількості імпульсів - підрахунок їх кількості. Реалізують таку операцію лічильники імпульсів. Лічильники також забезпечують представлення інформації про кількість імпульсів у вигляді двійкового коду (завдяки принципу побудови). Лічильники бувають прості (підсумовуючі, у яких код збільшується на одиницю після надходження на вхід кожного імпульсу; віднімаючі, у яких код відповідно зменшується після надходження на вхід кожного імпульсу) і реверсивні (суміщають властивості підсумовуючих і віднімаючих - можуть працювати в тому або іншому режимі за зовнішньою командою). Як правило, лічильники будують на основі тригерів. Схема чотирирозрядного підсумовуючого послідовного двійкового лічильника, виконаного на комбінованих RST- тригерах з імпульсними інверсними входами синхронізації наведена на рис. 21.10, його умовне позначення - на рис. 21.11 часові діаграми роботи - на рис. 21.12, таблиця переходів - у таблиці 1

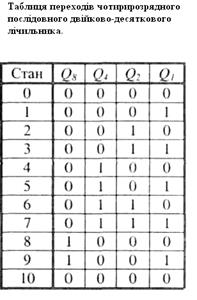

Таблиця1

Лічильник називається послідовним, тому що вихід тригера кожного попереднього розряду з'єднано з лічильним входом (входом синхронізації) тригера наступного розряду, в результаті чого передача інформації - перемикання тригерів розрядів лічильника - відбувається послідовно одного за одним. Це визначає низьку швидкодію лічильника.

У паралельних лічильників інформація з розряду в розряд передається за допомогою спеціальної комбінаційної схеми, а входи синхронізації тригерів з'єднано разом і перемикання всіх тригерів відбувається одночасно. Як видно з таблиці переходів і часових діаграм, при безперервній роботі лічильника на його виходах Q1,Q2, Q4, Q8 формується послідовний двійковий код. Вхід R призначений для встановлення лічильника в нульовий стан (у даному разі - подачею сигналу логічної 1). Входи D1, D2,D3, D4, призначені для паралельного занесення чисел у лічильник - для задания початкового стану, що відрізняється від нульового. Послідовну роботу лічильника можна порушити, обмеживши кількість його станів. Це можна зробити, вводячи зворотний зв'язок, як, наприклад, показано на рис. 21.13 Тепер при досягненні десятого стану лічильник одразу переходить в нульовий стан - отримано двійково-десятковий лічильник, який має не 16, а 10 станів і формує на виходах двійково-десятковий код. Його таблиця переходів наведена в таблиці 2, а часові діаграми роботи - на рис. 21.14

лічильника. Таблиця 2

Застосування таких лічильників разом з двійково-десятковими або двійково-семисегментними дешифраторами дозволяє на основі стандартних ІМС будувати схеми керування багаторозрядними десятковими індикаторами (розряди десяткові, а у межах десяткового розряду рахунок двійковий). На рис. 21.15 наведено схему лічильника, який також має десять станів, але працює не в послідовному двійковому коді, бо після надходження восьмого імпульсу переходить з 7 стану у 14, після дев'ятого - у 15, а після десятого - у 0.

У вигляді ІМС випускається досить широка номенклатура лічильників. На рис. 21.16 як приклад наведене умовне позначення чотирирозрядного реверсивного лічильника типу К561ИЕ14. Він має входи:

2) паралельного вводу інформації - D1, D2,D3, D4 3) синхронізації (тактовий) - С; 4) дозволу лічення - V; 5) напрямку лічення (підсумовування чи віднімання) - ±1; 6) задання роботи в двійковому чи двійково-десятковому коді - 2/10. Виходи: інформаційні - Q1,Q2, Q4, Q8 _ переносу (займу) в старший (із старшого) розряду - Р, Лекція 22 Регістри.Суматори. Регістри - це операційні елементи, які складаються з упорядкованих послідовностей елементів пам'яті (тригерів) і призначені для зберігання чисел у двійковому коді та виконання над ними найпростіших операцій. Так, у регістрах можуть виконуватись порозрядне додавання і віднімання, зсув на певну кількість розрядів (підготовка до множення або ділення) та інші елементарні операції.

Зсув числа полягає в тому, що цифра, яка розміщувалась до зсуву в і- му розряді, передається до сусіднього і + 1-го або і - 1-го розряду. Лічильний зсув інформації ліворуч на п розрядів еквівалентний множенню числа на 2n, а логічний зсув праворуч - множенню на 2n. Приклад зсуву на один розряд числа в чотирирозрядному регістрі показано нижче. Розрядність регістрів визначається кількістю тригерних комірок в них. Зсуви можна виконувати на будь-яку кількість розрядів. Застосовують також реверсивні регістри, в яких можливий зсув в обох напрямках. При цьому розряди, що звільнюються завдяки зсуву, заповнюються нулями або цифрами сусідніх розрядів. У лінійних регістрах при зсуві відбувається втрата молодших або старших розрядів машинного слова. Тому застосовують також кільцеві регістри, в яких зсув можна виконувати без втрати інформації.

Регістри зсуву будують на синхронних тригерах D або Ж-тилів, що з'єднані послідовно. Числа в них вводять послідовно цифра за цифрою, починаючи з молодшого розряду. Такі регістри називають послідовними. Приклад послідовного регістра зсуву на D-тригер показано на рис. 11.6, а. Зсув виконується за допомогою сигналу синхронізації. Вихід Q попереднього розряду приєднується до входу D наступного. Завдяки цьому кожний імпульс синхронізуючого сигналу встановлює наступний тригер у стан, в якому до цього знаходився попередній тригер, здійснюючи тим самим зсув інформації праворуч на один розряд. Вхід D першого тригера призначений для прийому в регістр інформації у вигляді послідовного коду. З кожним синхронізуючим імпульсом на вхід подають значення чергового розряду машинного слова. Наприклад, для запису в регістр числа 1011 на вхід подають сигнал "1", який першим синхроімпульсом пересилається на вихід Q1, далі подають знову на вхід сі' иі "1", який другим синхроімпульсом пересилається на вихід Q1, а сигнал з Q1 пересилається (зсовується) на один розряд, тобто на Q2; потім подають на вхід сигнал "0", який третім синхроімпульсом пересилається на Q1, а сигнали "1" з виходів Q1 і Q2 знову переносяться на один розряд праворуч і т. д. Таким чином, для запису в послідовний регістр л-розрядного числа машина повинна виконати п тактів, якщо, безумовно, це число не перевищує за розрядністю розрядність регістра. Число на виходах Q„...Q1 в регістрі зберігається в паралельному коді до приходу в нього наступного керуючого імпульсу. Якщо треба прочитати з послідовного регістра інформацію в послідовному коді, то її одержують з виходу Q4 після надходження чергових п синхронізуючих імпульсів.

В паралельному регістрі на синхронних D-тригерах (рис. 11.6, б) число на всі паралельні входи подається одночасно, а записується в регістр з надходженням синхронізуючого імпульсу. Швидкодія такого регістра максимальна, бо всі команди виконуються в ньому одночасно, а не по черзі. Розрядність не обмежена і змінюється шляхом простого з'єднання входів управління С декількох мікросхем. Використовують такі регістри переважно в оперативних запам'ятовуючих пристроях. Суматори - це комбінаційні операційні елементи цифрової техніки, призначені для арифметичного додавання двох чисел. Вони є основними елементами при створенні арифметично-логічних пристроїв.

Всі арифметичні операції в комп'ютері зводяться до додавання двійкових чисел. Для усіх випадків крім одного, а саме 1 + 1, їх може виконати елемент АБО. Лише виконання цієї операції потребує додаткових логічних елементів. Отже, треба створити таке з'єднання логічних елементів, яке працювало б як елемент АБО, а у випадку надходження на його обидва входи "логічних 1" забезпечувало б перенесення 1 у старший розряд числа і запис "О" у свій. Таку схему і таблицю істинності показано на рис. 22.2 (а). Одно-розрядні двійкові числа позначені літерами А і В, сума - S, перенос - Р. Імпульси чисел для додавання подають одночасно на схему АБО та схему І, що формує одиницю переносу і передає сигнал цієї одиниці на схему НЕ, яка у свою чергу разом із сигналом з виходу схеми АБО подає сигнал на другу схему І. Коли на вході суматора маємо одну з перших трьох комбінацій таблиці додавання, то на виході схеми НЕ одержуємо рівень "логічної 1" і на виході S маємо відповідну суму в границях одного розряду. Коли ж маємо комбінацію 1 + 1, то перша схема І передасть "логічну 1" на перенос, тобто на вихід Р, і на схему НЕ, на виході якої з'явиться "логічний 0", чим і буде забезпечено нуль на виході S. Розглянута схема називається схемою напівсуматора тому, що повний суматор повинен мати три входи: для чисел А, В та переносу Р0 з молодшого розряду. Схема такого повного двійкового суматора, складена з найпростіших логічних елементів, показана на рис. 22.2, (б). Повний суматор може бути складений з двох напівсуматорів (рис. 22.2, (в).Промисловість виготовляє суматори різної розрядності у вигляді окремих мікросхем. Умовне графічне позначення однієї з мікросхем чотирирозрядного суматора показано на рис. 22.2 (г).

Лекція 23 Структурна схема мікро - ЕОМ і МП. Інтерфейс. Сучасна технологія дозволяє виготовити вельми складні електронні пристрої у вигляді однієї або декількох ІМС. Але, щоб виробництво такого пристрою було економічно виправдано, необхідно виготовляти його масовими серіями. Разом з тим складні спеціалізовані пристрої потрібні у невеликій кількості екземплярів. Це протиріччя між можливостями технології та вузькою спеціалізованістю складних електронних пристроїв можна усунути за допомогою програмованих цифрових та логічних пристроїв, які отримали назву мікропроцесорних. Програмовані пристрої можуть виконувати різні функції в залежності від програми, що виконується, і це дозволяє розширити області їх застосування та збільшити тираж випуску. Мікропроцесор (МП) — це пристрій для обробки даних за певною програмою, реалізований з використанням інтегральної технології на одній або декількох великих інтегральних мікросхемах (ВІС). Дані, які обробляє МП, мають вигляд двійкових чисел, які можуть мати 4, 8, 16 або 32 розряди. Одиниця інформації, один біт, це однорозрядне двійкове число. Кванти інформації по 4, 8, 16, 32 біта називають словом даних. Широко розповсюджений процесор КР580ИК80 (серія К580), виконаний на одному кристалі ВІС, має 5000 транзисторів і слово даних довжиною 8 біт, що складаєодин байт. Спрощено МП можна представити структурною схемою. Головними частинами МП є арифметико-логічний пристрій (АЛЛ), пристрій керування (ПК) та регістри загального призначення (РЗП). Функції АЛП визначають архітектуру мікропроцесора в цілому. Типовими операціями, що їх виконують АЛП більшості мікропроцесорів є: ДОДАВАННЯ, ВІДНІМАННЯ, логічні І, АБО, ВИКЛЮЧАЮЧЕ АБО (операція нерівнозначності), ПОРІВНЯННЯ, ЗСУВ ВЛІВО, ЗСУВ ВПРАВО, ПРИРОЩЕННЯ ДОДАТНЕ, ПРИРОЩЕННЯ ВІД'ЄМНЕ. Деякі АЛП здатні виконувати більшу кількість операцій, в інших набір операцій обмежений. ПК задає режим роботи всіх елементів МП і послідовність виконання всіх операцій. РЗП виконують роль надоперативного запам'ятовуючого пристрою і призначені для зберігання М N-розрядних двійкових чисел (для процесорів серії К580 М = 6, N = 8). Одним з найважливіших регістрів МП є так званий акумулятор, який використовується у більшості арифметичних та логічних команд та у багатьох інших командах.

Рисунок 23.1 Спрощена структурна схема МП ПК декодує і дозволяє виконувати набір команд, сформований програмою, що розміщуються в зовнішньому постійному запам'ятовуючому пристрої (ПЗП).Команди по черзі викликаються з зовнішнього пристрою пам'яті і перетворюються на сигнали, які діють на всі блоки МП. Всі блоки МП зв'язані між собою і ПЗП шиною адреса(ША), шиною даних (ШД) і шиною керування(ШК). Шина являє собою паралельні провідники, до яких підключені блоки МП та зовнішні пристрої, наприклад ПЗП, ША використовується для передачі адрес комірок пам'яті до зовнішніх пристроїв. ШД використовується для передачі даних та кодів команд, які, як і числові дані, являють собою N-розрядні двійкові числа. ШК використовується для передачі сигналів керування. ПК визначає розподіл в часі зв'язків між блоками по одних і тих

самих шинах. Типовий МП звичайно виконують у вигляді великої ІМСз приблизно 40 електричними виводам и. У восьмирозрядного МП 16 виводів використовують для підключення доадресної шини (А0 — А15), 8 виводів — для підключення шини даних(D0— D7), 5-7 виводів припадає на підключення джерел живлення та сигнали синхронізації. Решту виводів (біля 10) використовують для передачі сигналів керування по шині керування. Сам по собі МП не може виконати якихось корисних функцій. Але на підставі МП можна виконати мікро ЕОМ — пристрій, який складається з МП, запам'ятовуючих пристроїв (ЗП), органів керування і зв'язку з зовнішніми пристроями (так звані інтерфейси). Сукупність мікро-ЕОМ із зовнішніми пристроями утворює мікропроцесорну систему (МПС) керування технічним об'єктом, Якщо ж мікро-ЕОМ призначена для керування якимось технічним об'єктом, то вона повинна мати засоби спряження мікропро ц есорної частини з цим об'єктом, тобто пристрої вводу та виводу. МПС складається з мікропроцесора МП, портів вводу-виводу інтерфейсних ІМС, пристроїв вводуПВв т а виводу ПВив, генератора тактових імпульсів ГТІ та запам'ятовуючих пристроїв ЗП. Пристроями вводу можуть бути контакти датчиків, що контролюють стан об'єкта, виводи датчиків,які перетворюють контрольовані фізичні параметри технічного об'єкта (температуру, тиск, деформацію, швидкість обертання) у пропорційні електричні сигнали, контакти клавіш клавіатури. АЦП і т. п. Пристроями виводу можуть бути: дисплей ( пристрій для візуального відображення інформації) друкуючий пристрій, ЦАП (для отримання аналогового сигналу керування об'єктом), транзисторні ключі і т. п. Пристрої вводу-виводу, сполучені електрично з силовою мережею, можуть бути підключені до низьковольтних ІМС мікропроцесорної системи лише через оптоелектричні пристрої, які забезпечують їх взаємну електричну ізоляцію. До складу пристроїв вводу-виводу входять також електронні підсилювачі, які використовують для підсилення сигналів від датчиків та сигналів керування МПС. Порти вводу-виводу інтерфейсних ІМСпризначені для короткочасногозберіганняінформації в процесі вводу та виводу і переключення каналів перетворення інформації. Звичайно порти інтерфейсних мікросхем під'єднують до пристроїв вводу-виводу через буферні підсилювачі, призначенідля узгодження рівня потужності сигналів. Запам'ятовуючі пристрої підрозділяють на постійні запам'ятовуючі пристрої пам'ять програм) і оперативні запам'ятовуючі пристрої (пам’ять даних). Останні виконуються н а паралельних регістрах. Оперативні запам'ятовуючі пристрої допускають зчитування та запис до них інформації, постійні запам'ятовуючі пристрої допускають тільки зчитування з них інформації, попередньо записаної до них за допомогою спеціальних програматорів. Оперативні запам'ятовуючи пристрої не зберігають занесену до них інформацію при відключенні напруги живлення МПС. В разі необхідності збереження такої інформації використовують резервне живлення мікросхем оперативної пам'яті від акумулятора

Шина керування (ПІК) Рисунок 23.2 Структурна схема мікро-ЕОМ . Особливістю МПС є те, що обмін інформацією між великою кількістю пристроїв здійснюється за допомогою спільних для всіх пристроїв шин — ША, ШД, ШК. За допомогою сигналів, що їх подає МП пошині керування, потрібні елементи МПС в певний момент працюють в режимі передачі д аних до шин, інші — в режимі прийому даних з шини, а решта елементів переводяться в стан від’єднання від шин, тобто не реагують на числові коди, що появляються на ШД та ША. Пристрій керування, що входить до складу МП, забезпечує певну послідовність сигналів керування за допомогою генератора тактових імпульсів (ГТІ). Частота сигналів ГТІ обмежена швидкодією логічних елементів і лежить звичайно 0,5-40 МГц. Для процесора серії К580 частота тактових імпульсів f = 2 МГц період тактових імпульсів Т= 0,5 мкс. Одна команда процесора К580, в залежності від її складності, виконується за 4—18 тактів. Отже, найкоротша команда виконується за 2 мкс, а найдовша — за 9 мкс. Якщо прийняти, що в середньому одна команда виконується за 8 тактів, тобто за 4 мкс, то за 0,1 сек. процесор виконає 25 000 команд: Припустимо, що МПС здійснює керування технічним об'єктом і програма, яку виконує;-МПС, складається з 1500 команд. Тоді за 0,1 сек. програма буде циклічно виконана: більше як 16 раз. Це дозволяє МП обслуговувати всі зовнішні пристрої так що у людини-оператора створюється враження неперервної взаємодії всіх елементів МПС, ніби вони працюють за принципом "кожний з кожним Для обробки інформації у МПС використовують двійкову систему числення. Мікроконтролери Мікроконтролери (МК) — різновид мікропроцесорних систем (мікро ЕОМ), орієнтована на реалізацію алгоритмів управління технічними пристроями і технологічними процесами. Порівняно з універсальними мікро ЕОМ мікроконтролери простіші, і вже близько 25 років тому виявилося можливим розмістити практично всю схемотехніку МК на одному кристалі, що і дало початок їх розвитку. МК ще називають однокристальною мікро ЕОМ Розробка МК означає появу ВІС такої функційної завершеності, яка дозволяє розв’язувати у повному обсязі задачи визначеного класу. Що відрізняє МК від мікро ЕОМ універсального призначення? Перш за все, це малий об'єм пам'яті і менш різноманітний склад зовнішніх пристроїв. До складу універсальної мікро ЕОМ входять модулі пам'яті великого об'єму і високої швидкодії, існує складна ієрархія ЗУ, оскільки багато задач (автоматизоване проектування, комп'ютерна графіка, мультимедійні додатки і ін.) без цього вирішити неможливо. Для МК ситуація інша, вони реалізують наперед відомі нескладні алгоритми, і для розміщення програм їм потрібна ємність пам'яті, на декілька порядків менша, ніж у мікро ЕОМ широкого призначення. Набір зовнішніх пристроїв також істотно звужується, а самі вони значно простіше. В результаті модулі мікро ЕОМ конструктивно самостійні, а МК виконується на одному кристалі, хоча в його складі є модулі того ж функціонального призначення. Зіставляючи мікропроцесор (тобто центральний процесорний елемент системи) і МК (тобто мікросхему простої системи в цілому) з погляду комерційних потреб, можна чітко бачити переважання МК. Число користувачів МК у декілька разів перевищує число користувачів окремих мікросхем МП. Застосування МК підтримується такими областями масового виробництва, як побутова апаратура, верстатобудування, автомобільна промисловість і т.д. Перші МК випущені фірмою Intel в 1976 р. (восьмирозрядний МК 8048). В даний час багатьма постачальниками випускаються 8-, 16- і 32-розрядні МК з місткістю пам'яті програм до десятків Кбайт, невеликими ОЗУ даних і набором таких інтерфейсних і периферійних схем, як паралельні і послідовні порти вводу/виводу, таймери, аналого-цифрові і цифроаналогові перетворювачі, широтно-імпульсні модулятори і ін. Серед тих МК, що випускаються широко відоме сімейство восьмирозрядних контролерів MCS-51/151/251 і 16-розрядних MCS-96/196/296 (фірми Intel). Дуже багато виробників випускають аналоги цих сімейств або сумісні з ними МК. У вітчизняній номенклатурі це К1816ВЕ51, К1830ВЕ51 (восьмирозрядні МК). Останнім часом фірма Intel зосередила зусилля на розробці складних мікропроцесорів для комп'ютерів і поступилася сектором ринку простих МК іншим фірмам, зокрема, фірмі Atmel, яка випускає популярне сімейство МК серії АТ89 з Флэш-пам'яттю програм, що є функціональним аналогом сімейства восьмирозрядних МК фірми Intel. Цікаво, що, не дивлячись на появу нових 16- і 32-розрядних МК, найбільший успіх на ринку залишається за 8-розрядними. Зараз близько половини ринку МК (приблизно 6 млрд доларів) залишається за цими МК, що означає їх лідирування з великим відривом щодо представників інших сімейств. У структурі МК сімейства АТ89С (рисунок 18.3) використовуються роздільні блоки програмної пам'яті типа Флеш і ОЗУ даних (Гарвардська архітектура). Діапазони місткостей пам'яті, як і частот генератора тактових імпульсів ГТІ, приведені на рисунку 18.3, характеризують параметри представників сімейства від молодшого до старшого. При необхідності можливе підключення зовнішніх БІС ПЗП, ОЗУ для розширення простору пам'яті. Засоби вводу/виводу представлені 4 паралельними портами (32 лінії) і лініями TxD (вихід передавача) і RxD (вхід приймача) для послідовного вводу/виводу. До складу МК входять 2—3 таймери-лічильники (16-розрядних), які дають системні мітки часу і відпрацьовують інтервали. Для скорочення ширини фізичного інтерфейсу функції ліній паралельних портів суміщені, і в різних режимах мають різне призначення. Система переривань з 5 джерелами запитів радіального типу обслуговує 2 зовнішні запити, 2 запити від таймерів і 1 від послідовного порту. При частоті ГТІ 12 Мгц більшість команд виконується за 1 мкс, деякі команди — за 2 мкс

|

|||||||||||||||

|

Последнее изменение этой страницы: 2016-08-01; просмотров: 1568; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.15.26.231 (0.017 с.) |

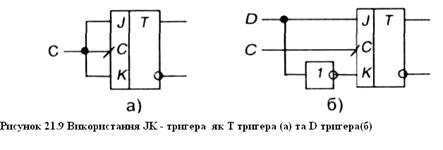

- тригер є універсальним, бо він може виконувати роль RS - тригера, якщо використовувати вхід J як S, а K як R (при цьому таблиця переходів RS -три-гера відповідає першим трьом рядкам таблиці переходів JK- тригера). Якщо задати одиниці на обох інформаційних входах, JK- тригер стає Т-тригером. Схеми використання JK- тригера як Т-тригера та D - тригера зображені на рис. 21.9

- тригер є універсальним, бо він може виконувати роль RS - тригера, якщо використовувати вхід J як S, а K як R (при цьому таблиця переходів RS -три-гера відповідає першим трьом рядкам таблиці переходів JK- тригера). Якщо задати одиниці на обох інформаційних входах, JK- тригер стає Т-тригером. Схеми використання JK- тригера як Т-тригера та D - тригера зображені на рис. 21.9

Таблиця переходів чотирирозрядного послідовного двійкового лічильника

Таблиця переходів чотирирозрядного послідовного двійкового лічильника

1) запису інформації з входів паралельно го вводу інформації D1, D2,D3, D4- WR;

1) запису інформації з входів паралельно го вводу інформації D1, D2,D3, D4- WR;

У цифровій техніці застосовують двійкові і десяткові суматори послідовної і паралельної дії. Кожен багаторозрядний суматор складається з набору однорозрядних суматорів, з'єднаних різними способами.

У цифровій техніці застосовують двійкові і десяткові суматори послідовної і паралельної дії. Кожен багаторозрядний суматор складається з набору однорозрядних суматорів, з'єднаних різними способами.