Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

CISC- и RISC-архитектура компьютеровСодержание книги

Поиск на нашем сайте

Разработка машинного языка требует предварительного принятия многих решений. Одно из них состоит в выборе между построением сложной машины, способной декодировать и выполнять широкий спектр разнообразных команд, и созданием более простой машины, которая будет иметь ограниченный набор команд. К первому варианту относятся компьютеры с CISC-архитектурой (Complex Instruction Set Computer — компьютер со сложным набором команд), а ко второму — компьютеры с RISC-архитектурой (Reduced Instruction Set Computer — компьютер с ограниченным набором команд). CISC-компьютер проще программировать, поскольку единственная его команда позволяет решить задачу, выполнение которой в RISC-компьютере потребует длинной последовательности более простых команд. Однако CISC-компьютер сложнее сконструировать, и он обходится дороже как при создании, так и при эксплуатации. Более того, многие сложные команды найдут лишь ограниченное применение, вследствие чего могут оказаться просто балластом, создающим дополнительную бесполезную нагрузку. Для уменьшения числа используемых электронных цепей CISC-процессоры обычно конструируются по двухуровневой схеме, при которой каждая машинная команда в действительности выполняется как последовательность простейших операций. В такие процессоры обычно встроен блок специальных ячеек памяти, называемых памятью микрокоманд, в которых записана программа, именуемая микропрограммой. Именно эта микропрограмма управляет выполнением сложных команд машинного языка. Кроме того, в микропрограмму можно вносить коррективы и тем самым изменять смысл команд машинного языка. Таким образом, помимо поддержки расширенного набора команд CISC-процессоров, реализуемой без использования сложных электронных схем, наличие микропрограммы позволяет настраивать один и тот же тип центрального процессора на поддержку различных специализированных команд машинного языка просто посредством внесения необходимых изменений в микропрограмму. Сторонники RISC-архитектуры заявляют, что все эти преимущества не оправдывают издержки, связанные с поддержкой микропрограммирования. Они утверждают, что лучше спроектировать более простую машину с небольшим, но тщательно продуманным набором команд. Такой подход позволяет избежать усложнения конструкции, связанного с поддержкой памяти микропрограмм, что приводит к упрощению проектирования центрального процессора. Однако это означает, что программы на машинном языке для RISC компьютеров будут значительно длиннее программ для CISC-компьютеров, так как для выполнения сложных операций потребуется несколько отдельных машинных команд, тогда как в CISC-архитектуре тот же результат достигается с помощью единственной команды. В настоящее время на рынке представлены оба вида процессоров — как с CISC-, так и с RISC-архитектурой. Процессоры серии Pentium, выпускаемые компанией Intel, являются примером центральных процессоров с CISC-архитектурой, тогда как процессоры серии PowerPC, выпускаемые компаниями Apple Computer, IBM и Motorola, имеют RISC-архитектуру.

Конвейерная обработка

Скорость прохождения электронных импульсов по проводам не превышает скорости света. Поскольку скорость света составляет около 30 см в наносекунду (одна миллиардная часть секунды), потребуется не менее двух наносекунд, что бы блок управления центрального процессора выбрал команду из ячейки памяти, которая находится от него на расстоянии около 30 см. Запрос на считывание должен поступить в схемы основной памяти, для чего потребуется не менее одной наносекунды. После этого выбранная команда должна быть доставлена в блок управления, что также потребует не менее одной наносекунды. Следовательно, чтобы выбрать и выполнить команду, машине потребуется несколько наносекунд, а это означает, что увеличение скорости выполнения команд прямо связано с проблемой его миниатюризации. Несмотря на фантастический прогресс в этой области, все же рано или поздно будет достигнут теоретический предел. Попытки решить эту проблему привели к тому, что конструкторы вычислительных машин заменили исходную концепцию скорости выполнения команд принципом пропускной способности. Этот термин означает общее количество работы, которое машина способна выполнить за определенный период времени, при этом продолжительность выполнения отдельного задания в расчет не принимается. Приведем пример того, как можно повысить пропускную способность компьютера без увеличения скорости выполнения команд. В данном случае используется подход, называемый конвейерной обработкой, согласно которому выполнение этапов машинного цикла может перекрываться во времени. Например, во время этапа выполнения одной из команд для следующей команды уже может выполняться этап выборки, а это означает, что выполнение более одной команды одновременно осуществляется по принципу "конвейера", т.е. каждая из них будет находиться на разной стадии выполнения. В результате общая пропускная способность компьютера увеличится, причем без повышения скорости выборки и выполнения каждой отдельной команды. Естественно, когда машина достигнет команды перехода, все преимущества от предварительной выборки и выполнения последующих команд будут утрачены, так как в действительности потребуется выполнение совершенно других команд, которых в данное время на "конвейере" нет. Конструкции современных процессоров оставляют далеко позади рассмотренный выше простейший пример конвейерной обработки. Современные процессоры способны выбирать сразу несколько команд за одно и то же время, а также реально выполнять больше одной команды одновременно, если только их действия не являются взаимозависимыми.

Многопроцессорные машины

Использование конвейерного режима можно рассматривать как первый шаг в направлении реализации параллельной обработки, предусматривающей одновременное выполнение сразу нескольких действий. Однако параллельная обработка требует использования нескольких устройств обработки данных, что приводит к необходимости создания многопроцессорных машин. Аргументом в пользу создания многопроцессорных машин может стать не что иное, как модель работы человеческого мозга. Современные технологии уже позволяют создавать электронные схемы, в которых есть столько же переключающих цепей, сколько нейронов в мозге человека (нейроны можно рассматривать как живые переключающие схемы). Несмотря на это, возможности современных компьютеров все еще значительно уступают возможностям человеческого мозга. Считается, что это происходит из-за неэффективного использования компонентов машин, вызванного недостатками архитектуры компьютеров. Действительно, если в компьютере установлено множество схем памяти и всего один центральный процессор, то большинство схем памяти в любой момент времени просто не используется. В противоположность этому, большая часть человеческого мозга в любой момент времени пребывает в активном состоянии. По этой причине сторонники параллельной обработки выступают в защиту машин, имеющих несколько устройств обработки данных. Они заявляют, что такое решение способствует созданию конфигурации с более высокой степенью использования элементов. По этому принципу было разработано большое количество машин. Один подход предусматривает подключение к одним и тем же ячейкам основной памяти нескольких устройств обработки данных, каждое из которых напоминает обычный центральный процессор однопроцессорной машины. В такой конфигурации процессоры могут работать независимо, координируя свои действия посредством обмена сообщениями через общие ячейки памяти. Например, когда один процессор получает большое и сложное задание, он может записать программу для выполнения части этого задания в общем поле памяти, а затем послать другому процессору запрос на ее выполнение. В результате мы получим машину, в которой разные последовательности команд выполняют обработку разных наборов данных. Подобная архитектура носит название MIMD (multiple instruction stream, multiple-data stream — множество потоков команд с множеством потоков данных). Очевидно, что она является противоположной по отношению к традиционной архитектуре компьютеров, называемой SISD (single instruction stream, single-data stream — один поток команд и один поток данных). Еще одним вариантом архитектуры многопроцессорных компьютеров является такое соединение процессоров между собой, которое позволит им одновременно выполнять одну и ту же последовательность команд, но с разными наборами данных. Этот вариант носит название архитектуры SIMD (single instruction stream, multiple-data stream — один поток команд и множество потоков данных). Машины этого типа больше всего подходят для выполнения таких приложений, в которых один и тот же алгоритм обработки применяется к отдельным наборам схожих элементов, составляющих один большой блок данных. Еще один подход к реализации параллельной обработки заключается в конструировании больших машин как некоего конгломерата из машин меньшего размера, каждая из которых имеет собственную памятью и центральный процессор. В подобной архитектуре каждая машина связана со своими соседями; в результате задача, поставленная перед всей системой, может быть разделена на элементарные задания, распределяемые между отдельными машинами. Таким образом, если задача, поставленная перед одной внутренней машиной, может быть разделена на несколько подзадач, то эта машина может "попросить" соседние машины выполнить все подзадачи параллельно. В результате вся задача в целом может быть выполнена в многопроцессорной машине намного быстрее, чем в однопроцессорной. При разработке и использовании многопроцессорных машин мы сталкиваемся с проблемой баланса нагрузки, т.е. динамического распределения задач между различными процессорами в целях повышения эффективности их работы. Эта проблема тесно связана с проблемой масштабирования, или разделения текущей задачи на несколько подзадач, количество которых совместимо с количеством доступных процессоров. Еще одна проблема заключается в сложности распределения выделенных задач. Действительно, если количество задач возрастает, то объем работы, связанной с их распределением и координацией взаимодействия между отдельными подзадачами, растет экспоненциально. Если имеется четыре задачи, то можно выделить шесть потенциальных пар задач, которым потребуется взаимодействовать друг с другом. Если имеется пять задач, то количество потенциальных каналов взаимодействия возрастает до десяти, а в случае с шестью задачами это количество увеличится до пятнадцати. Искусственные нейронные сети, конструкции которых основана на наших знаниях о структуре человеческого мозга, представляют собой еще один тип многопроцессорной архитектуры, так как они состоят из множества элементарных процессоров или устройств обработки информации, выходные данные которых — это просто реакция такого устройства на поступившие входные данные. Все эти простые процессоры соединены между собой и образуют сеть, в которой выходные данные одних процессоров являются входными данными для других процессоров. Такая машина программируется посредством настройки степени влияния выходных данных каждого процессора на реакцию соединенных с ним процессоров. В какой-то степени этот подход имитирует способ, в соответствии с которым, как считается, происходит обучение нашего мозга. Точнее говоря, биологические сети нейронов головного мозга человека учатся реагировать определенным образом на заданные стимулы посредством управления химическим составом соединений (синапсов) между отдельными нейронами, что, в свою очередь, контролирует способность одного нейрона влиять на действия других нейронов.

ПРИЛОЖЕНИЕ Пример типичного машинного языка

Архитектура машины

Рассматриваемая гипотетическая машина имеет 16 регистров общего назначения, пронумерованных от 0 до F (в шестнадцатеричной системе счисления). Длина каждого регистра равна одному байту (восьми битам). Для идентификации регистров в машинных командах каждому регистру присвоен уникальный четырехбитовый код, который представляет собой номер этого регистра. Таким образом, регистр 0 идентифицируется как 0000 (шестнадцатеричный 0), а регистр 4 — как 0100 (шестнадцатеричное 4). Поскольку память рассматриваемой машины состоит из 256 ячеек, каждая ячейка будет иметь уникальный адрес, представляющий собой целое число в диапазоне от 0 до 255. Следовательно, адрес любой ячейки памяти может быть представлен восьмибитовыми числами от 00000000 до 11111111 (в шестнадцатеричном представлении от 00 до FF).

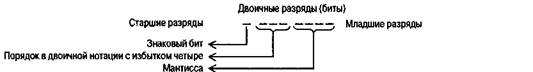

Предполагается, что числа с плавающей запятой хранятся в следующем формате:

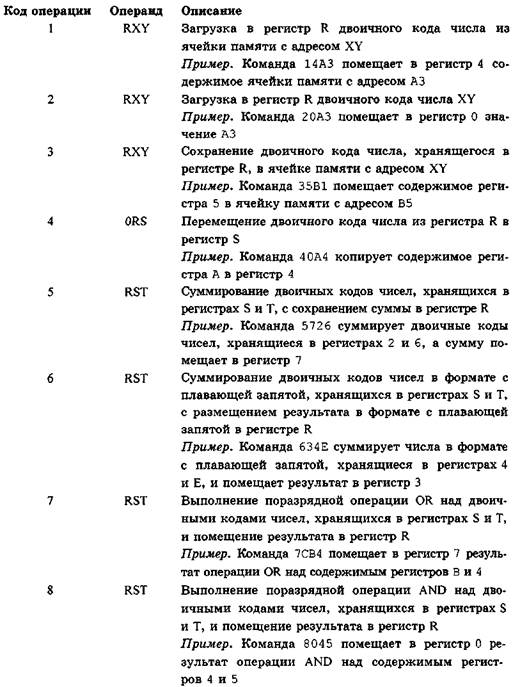

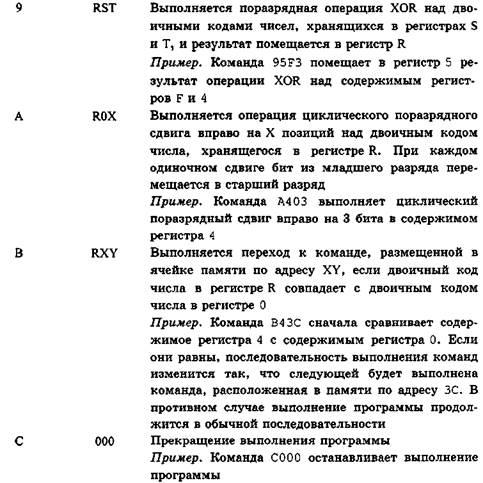

Машинный язык

Длина каждой машинной команды равна двум байтам. Первые четыре бита содержат код операции, последние 12 битов образуют поле операндов. В приведенной ниже таблице перечислены и кратко описаны команды, показанные в шестнадцатеричном представлении. Буквы R, S и Т используются для указания в поле операндов позиции шестнадцатеричных цифр, являющихся идентификаторами регистров, которые меняются в зависимости от конкретной команды. Буквы X и Y используются для указания в поле операндов позиций тех шестнадцатеричных цифр, которые не являются идентификаторами регистров.

|

||

|

Последнее изменение этой страницы: 2016-04-21; просмотров: 480; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.102 (0.01 с.) |