Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Приклад встановлення біт регістру TCCR0Содержание книги

Поиск на нашем сайте FOC0 = 0 WGM00 = 0 COM01 = 0 COM00 = 0 WGM01 = 1 CS02 = 1 CS01 = 1 CS00 = 0

ldi r16, ((1<<WGM01) | (1<<CS02) | (1<<CS01)) out TCCR0, r16

Опис деяких мнемонік інструкцій, які використовуються у цій лабораторній роботі і не були описані у описах до попередніх лабораторних робіт AND – «Логічне І» Здійснює логічне І між вмістимим регістру Rd і регістром Rr – результат поміщається у регістр призначення Rd.

Вплив на регістри статусу:

Біт S:

Біт V: Очищується. Біт N: Встановлюється, якщо MSB встановлений, у іншому випадку – скидається. Біт Z: Встановлюється, якщо результатом є число $00, у іншому випадку – скидається.

Наприклад: and r2,r3;Побітне І між регістрами R2 і R3, результат у R2

OR – «Логічне АБО» Здійснює логічне АБО між вмістимим регістру Rd і регістром Rr – результат поміщається у регістр призначення Rd.

Вплив на регістри статусу:

Біт S:

Біт V: Очищується. Біт N: Встановлюється, якщо MSB встановлений, у іншому випадку – скидається. Біт Z: Встановлюється, якщо результатом є число $00, у іншому випадку – скидається.

Наприклад: or r2,r3;Побітне АБО між регістрами R2 і R3, результат у R2

XOR – «Логічне ВИКЛЮЧАЮЧЕ АБО» Здійснює логічне ВИКЛЮЧАЮЧЕ АБО між вмістимим регістру Rd і регістром Rr – результат поміщається у регістр призначення Rd.

Вплив на регістри статусу:

Біт S:

Біт V: Очищується. Біт N: Встановлюється, якщо MSB встановлений, у іншому випадку – скидається. Біт Z: Встановлюється, якщо результатом є число $00, у іншому випадку – скидається.

Наприклад: xor r2,r3;Побітне ВИКЛЮЧАЮЧЕ АБО між регістрами R2 і R3, результат у R2

COM – «Виконання порозрядного доповнення до одиниці (зворотній код)» Ця інструкція виконує порозрядне доповнення до одиниці (зворотній код числа) регістру Rd. Ця операція еквівалентна побітному інвертуванню вмістимого регістра і результат записується у той самий регістр.

Вплив на регістри статусу:

Біт S:

Біт V: Очищується. Біт N: Встановлюється, якщо MSB встановлений, у іншому випадку – скидається. Біт Z: Встановлюється, якщо результатом є число $00, у іншому випадку – скидається. Біт C: Встановлюється завжди.

Наприклад: com r4; Виконання порозрядного доповнення до одиниці (зворотній код) регістра R4

NEG – «Виконання порозрядного доповнення до двох (додатковий код)» Ця інструкція виконує порозрядне доповнення до двох (додатковий код числа) регістру Rd. У випадку виконання цієї інструкції над регістром значення якого рівне $80, то тоді значення регістру не змінюється після виконання цієї команди. Ця операція еквівалентна зміни знаку вмістимого регістра із збереженням модуля числа (у випадку, коли число розглядається однобайтним знаковим з інтервалу

Вплив на регістри статусу:

Біт H: Встановлюється, якщо відбулася «позика» з третього біту. У іншому випадку очищується Біт S:

Біт V: Встановлюється, якщо переповнення числа в додатковому коді від уявного віднімання від нуля. У іншому випадку віднімаються. Переповнення в додатковому коді відбудеться, тоді і тільки тоді, коли вмістиме регістру після виконання цієї операції (результат) буде $80 Біт N: Встановлюється, якщо MSB встановлений, у іншому випадку – скидається. Біт Z: Встановлюється, якщо результатом є число $00, у іншому випадку – скидається. Біт C: Встановлюється, якщо відбулася «позика» в уявного віднімання від нуля. У іншому випадку віднімаються. Біт C встановиться у всіх випадках за винятком, коли вмістиме регістру після виконання цієї операції (результат) буде $00

Наприклад: neg r4; Виконання порозрядного доповнення до двох (додатковий код) регістра R4

SBRC – «Пропустити наступну інструкцію, якщо біт регістру очищений» Ця інструкція перевіряє вибраний біт у вказаному регістрі і пропускає наступну інструкцію, якщо біт очищений якщо Rr(b) = 0 то

Вплив на регістри статусу:

Наприклад: sub r0, r1; Віднімання регістра R1 від R0 sbrс r0, 7; Пропустити наступну інструкцію, якщо біт 7 регістра R0 очищений sub r0, r1; Виконується тільки тоді, коли 7 регістра R0 очищений nop;продовження

SBRS – «Пропустити наступну інструкцію, якщо біт регістру встанвлений» Ця інструкція перевіряє вибраний біт у вказаному регістрі і пропускає наступну інструкцію, якщо біт встановлений якщо Rr(b) = 1 то

Вплив на регістри статусу:

Наприклад: sub r0, r1; Віднімання регістра R1 від R0 sbrs r0, 7; Пропустити наступну інструкцію, якщо біт 7 регістра R0 встановлений sub r0, r1; Виконується тільки тоді, коли 7 регістра R0 встановлений nop;продовження

SBIC – «Пропустити наступну інструкцію, якщо біт регістру вводу/виводу очищений» Ця інструкція перевіряє вибраний біт у вказаному регістрі вводу/виводу і пропускає наступну інструкцію, якщо біт очищений. Ця інструкція працює тільки з першими 32 регістрами вводу/виводу – адреси 0÷31

якщо I/O(A,b) = 0 то

Вплив на регістри статусу:

Наприклад: sbiс $1C, 1; Пропустити наступну інструкцію, якщо біт 1 регістра EEWE очищений sub r0, r1; Виконується тільки тоді, коли 1 регістра EEWE очищений nop;продовження

SBIS – «Пропустити наступну інструкцію, якщо біт регістру вводу/виводу встановлений» Ця інструкція перевіряє вибраний біт у вказаному регістрі вводу/виводу і пропускає наступну інструкцію, якщо біт встановлений. Ця інструкція працює тільки з першими 32 регістрами вводу/виводу – адреси 0÷31

якщо I/O(A,b) = 1 то

Вплив на регістри статусу:

Наприклад: sbis $1C, 1; Пропустити наступну інструкцію, якщо біт 1 регістра EEWE встановлений sub r0, r1; Виконується тільки тоді, коли 1 регістра EEWE встановлений nop;продовження

Завдання: 1. Проініціалізувати стек 2. Здійснити стартову настройку таймера лічильника 0 2.1 Регістр порогу порівняння OCR0 рівним 78 (десяткове число) 2.2 Регістр управління таймером-лічильником 0 TCCR0 2.2.1 Біт примусової установка результату порівняння FOC0 = 0b0 2.2.2 Режим Скидання при збігу (CTC): WGM01, WGM00 = 0b10 2.2.3 Вихід OC0 відключений: COM01, COM00 = 0b00 2.2.4 Тимчасово таймер відключений: CS02, CS01, CS00 = 0b000 2.3 Регістр маски переривань скидаємо TIMSK = 0 2.4 Запускаємо таймер лічильник 0 з встановленням подільника частоти 256[52]: CS02, CS01, CS00 = 0b110 3. Написати підпрограму очистки біту OCF0 у регістрі TIFR[53] 3.1 Регістри, які будуть використовуватися у підпрограмі попередньо зберегти у стеку, для того, щоб їх використання не вплинуло на виконання всієї програми 3.2 Підготувати маску регістра з встановленим бітом під номером OCF0, всі інші біти мають бути очищеними 3.3 Записати цю підготовлену маску у регістр вводу-виводу TIFR – ця процедура очистить біт OCF0 у регістрі вводу-виводу TIFR. 3.4 Відновити регістри збережені у стеку 3.5 Вийти з підпрограми 4. Реалізувати безперервний цикл, який перевіряє чи лічильник досяг пирогового значення 4.1 Завантажити у регістр загального призначення регістр вводу-виводу TIFR 4.2 У разі, якщо біт під номером OCF0 встановлений, то перейти на підпрограму очистки біту OCF0 у регістрі TIFR 4.3 Перейти на пункт 4.1 5. Хід виконання програми 5.1 Зайти у стимулятор 5.2. Відкрити настройки стимулятора Debug→AVR Simulator 2 Options

5.3 Найти поле Frequency MHz – тактова частота процесора

5.4 Встановити поле Frequency MHz 10.000000 МГц – нову тактову частота процесора

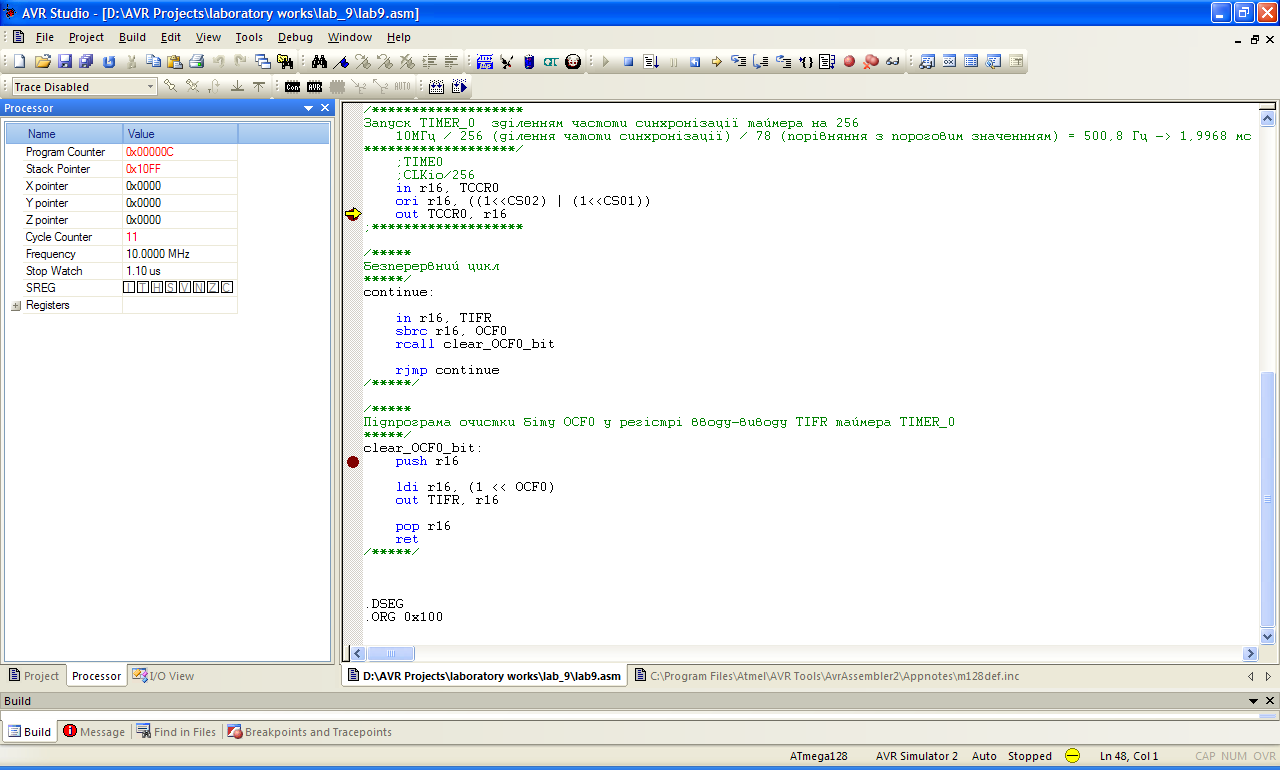

5.5 В такому разі у режимі CTC (поріг порівняння OCR0 рівне 78) і подільнику частоти 256 (CS02, CS01, CS00 = 0b110 регістра TCCR0) 10 МГц/256/78 ≈ 500 Гц (2 мс період встановлення біту OCF0) 5.6 Стати курсором на рядку, де запускається таймер-лічильник 0, (де виконується встановлення CS02, CS01, CS00 = 0b110) і у цьому місця поставити точку зупинки (breakpoint) Debug→Toggle Breakpoint або функціональною кнопкою F9

5.7 Переконатися, що точка зупинки встановлена – збоку рядка буде червоний кружечок

5.8 Аналогічно пунктам 5.6 і 5.7 встановити точку зупинки ум підпрограмі очищення біту OCF0 у регістрі вводу виводу TIFR 5.9 Запустити програму на виконання (не покроково) Debug→Run, або функціональною кнопкою F5 5.10 Програма має зупинитися у першій точці зупинки 5.11 Перейти у вікно Processor (якщо воно не відкрите, то його можна відкрити View→Toolbars→Processor)

5.11 Переконатися, що поле Frequency рівне 10.0000 МГц 5.12 Правою кнопкою мишки клікнути по полю Stop Watch вікна Processor – контекстне меню, яке зображено нижче

5.13 Якщо після числового значення у полі Stop Watch вікна Processor (яке відповідає за час, який пройшов або з моменту запуску програми, або обнулення часу операцією Reset Cycle Counter з контекстного меню, яке було описане вище) стоїть us, то час відображається у мікросекундах, якщо ms – у мілісекундах. Переключення відображення часу з мікросекунд у мілісекунди виконується операцією Show Stopwatch as milliseconds з контекстного меню, яке описане вище, а з мілісекунди у мікросекунди - Show Stopwatch as microseconds 5.14 Обнулити час у полі Stop Watch вікна Processor командою Reset Cycle Counter, описаною вище і переконатися, що час справді рівний 0. При цьому вибір відображення часу у мікросекундах чи мілісекундах можна вибрати на розсуд виконавця лабораторної роботи (студента)

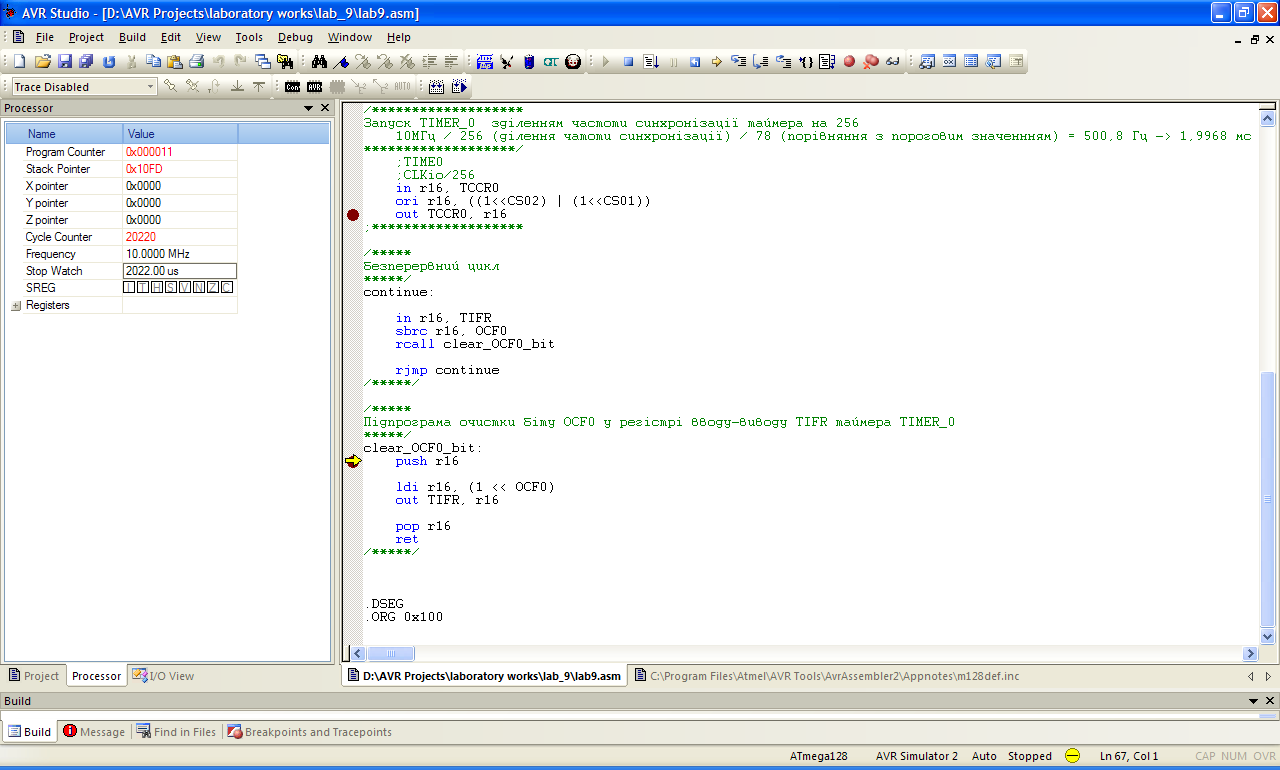

5.15 Запустити програму на виконання (не покроково) Debug→Run, або функціональною кнопкою F5 5.16 Програма має зупинитися у підпрограмі очищення біту OCF0 у регістрі вводу виводу TIFR 5.17 Переконатися з допомогою поля Stop Watch вікна Processor, що час, за який встановився біт OCF0 у регістрі вводу виводу TIFR становить ≈2 мс

5.18 Декілька разів продовжувати виконання програми (не покроково) Debug→Run, або функціональною кнопкою F5 – переконатися, що програма заходить у підпрограму очистки OCF0 у регістрі вводу виводу TIFR через ≈2 мс.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-18; просмотров: 474; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.214 (0.007 с.) |

. Використовується для тестування знаку результату.

. Використовується для тестування знаку результату.

).

).

інакше

інакше