Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Розрядний таймер-лічильник 0 з функціями широтно-імпульсної модуляції і асинхронного тактуванняСодержание книги

Поиск на нашем сайте Таймер-лічильник 0 - модуль багатофункціонального одноканального 8-розрядного таймера-лічильника з апаратним виходом для генерації ШІМ-сигналу і вбудованим асинхронним опціональним тактовим генератором, який оптимізований під використання часового кварцу (32768Гц) для асинхронного по відношенню до системної синхронізації тактування.

Основні властивості: - одноканальний лічильник - Режим скидання таймера при успішному порівнянні (автоматичне перезавантаження) - Широтно-імпульсна модуляція без генерації помилкових імпульсів при записі нового порогу порівняння в OCR0 (подвійна буферизація) і з фазовою корекцією - генератор частоти - 10-розрядний дільник частоти - Генерація переривань про переповненні та виконання умови порівняння (TOV0 і OCF0) Можливість асинхронного тактування спільно із зовнішнім кварцовим резонатором частотою 32 кГц незалежно від частоти синхронізації вводу-виводу.

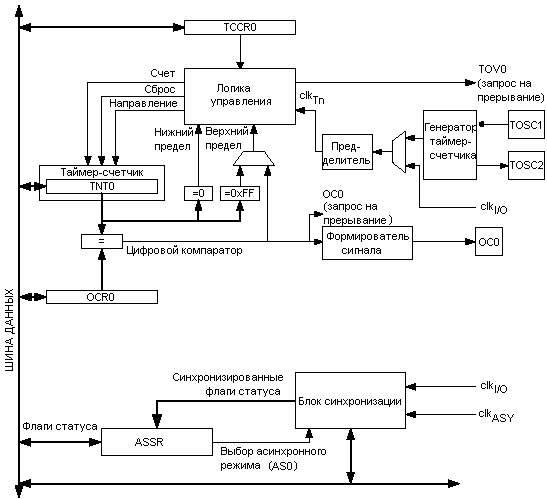

Короткий огляд Функціональна схема 8-розр. таймера-лічильника представлена на рисунку нижче. Зв'язки з регістрами, до яких здійснює доступ ЦПУ, в т.ч. біти вводу-виводу і лінії вводу-виводу показані жирною лінією.

Регістри (з області вводу-виводу) Регістр таймера-лічильника (TCNT0) і регістр порогу порівняння (OCR0) - 8-розр. регістри. Сигнали запиту на переривання представлені як мітки переривань таймера в регістрі TIFR. Всі переривання індивідуально маскуються за допомогою регістра маски переривань таймерів (TIMSK). Регістри TIFR і TIMSK не представлені на функціональній схемі, тому що вони спільно використовуються з іншими таймерами мікроконтролера. Таймер-лічильник може тактуватися через дільник частоти внутрішньо або асинхронно через зовнішні виходи TOSC1/2. Асинхронна робота управляється регістром асинхронного стану (ASSR). Блок синхронізації здійснює вибір, яке тактове джерело використовується для інкрементування (декрементування) стану таймера-лічильника. Якщо джерело тактування не задане, то таймер-лічильник знаходиться в неактивному стані. Вихід логіки вибору синхронізації позначений як синхронізація таймера (clkT0). Значення регістра порога порівняння з подвійною буферизацією (OCR0) безперервно порівнюється зі значенням таймера-лічильника. Результат порівняння може використовуватися для генерації сигналів з ШІМ або прямокутних імпульсів змінної частоти на виводі OC0. Збіг порога порівняння зі значенням таймера-лічильника призводить до встановлення мітки результату порівняння (OCF0), який може використовуватися для генерації запиту на переривання по результату порівняння. Визначення Деякі визначення та їх скорочені найменування, які інтенсивно використовуються в цьому розділі, представлені в таблиці Таблиця визначень

Тактові джерела таймера-лічильника 0 Таймер-лічильник 0 може тактуватися внутрішньо синхронно або зовні асинхронно (по відношенню до внутрішньої системної синхронізації). По замовчуванню використовується тактовий сигнал clkT0, еквівалентний тактовому сигналу мікроконтролера clkI/O. Якщо в біт AS0 регістра ASSR записати лог.1 то в якості джерела синхронізації виступає генератор таймера-лічильника, зв’язаний з виводами підключення низькочастотного кварцового резонатора TOSC1 і TOSC2. Блок лічби Основу 8-розр. таймера-лічильника 0 складає програмований двонаправлений лічильник. Рисунок показує функціональну схему лічильника і оточуючих його елементів.

Опис сигналів (внутрішні сигнали): «Счет» - інкрементується або декрементується TCNT0 на 1. «Направл.» - Задає напрям лічби: інкрементування (+1, пряма лічба) або декрементування (-1, зворотнаа лічба). «Сброс» - Скидає вміст TCNT0 (запис лог. 0 в усі розряди). clkT0 - Синхронізація таймера-лічильника. «Верхний предел» - Визначає максимальне значення, яке може досягти TCNT0. «Нижний предел» - Задає мінімальне значення, яке може досягти TCNT0 (нуль). В залежності від обраного режиму роботи лічильник скидається, інкрементується або декрементується на кожному такті синхронізації (clkT0). Тактовий сигнал clkT0 може бути внутрішнім або зовнішнім, а його частота вибирається за допомогою біт вибору частоти синхронізації CS02-CS00. Якщо джерело синхронізації не задане (CS02-CS00 = 0b000), то таймер зупиняється. Проте стан TCNT0 доступне CPU незалежно від того працює синхронізація таймера чи ні. Запис в регістр таймера через CPU перекриває будь-які дії самого лічильника: скидання або лічбу, тобто має більш високий пріоритет. Послідовність рахунку визначається установкою біт WGM01 і WGM00, розташованих в регістрі управління таймером-лічильником (TCCR0). Є точний зв'язок між поведінкою лічильника (алгоритмом рахунку) і генерованою на виході OC0 формою сигналу. Мітка переповнення таймера-лічильника (TOV0) встановлюється відповідно до режиму роботи, який вибирається бітами WGM01, WGM00. Біт TOV0 може використовуватися для генерації переривання CPU. Блок порівняння 8-розрядний цифровий компаратор безперервно виконує порівняння вмісту регістра таймера-лічильника TCNT0 з регістром порогу порівняння OCR0. Кожного разу, коли значення TCNT0 збігається зі значенням OCR0 компаратор встановлює мітку збігу OCF0 наступним тактом синхронізації таймера. Якщо дозволено переривання бітом OCIE0 = 1, то установка мітки збігу викликає запит на переривання. Прапор OCF0 автоматично скидається під час виконання процедури обробки переривання. Альтернативно, прапор OCF0 можна скинути програмно шляхом запису лог. 1 в позицію даного биту. Генератор сигналу використовує сигнал результату порівняння для генерації прямокутних імпульсів по одному з алгоритмів, який вибирається бітами задання режиму роботи таймера WGM01, WGM00 і бітами задання режиму формування вихідного сигналу (COM01, COM00). Верхній і нижній межі дічби використовуються в деяких режимах роботи для виконання спеціальних дій. На рисунку наведена функціональна схема блоку порівняння.

Регістр OCR0 виконаний за схемою подвійної буферизації при використанні режимів з широтно-імпульсною модуляцією (ШІМ). У нормальному режимі і режимі скидання таймеру при збігу (CTC) схема подвійної буферизації відключається. Подвійна буферизація дозволяє синхронізувати оновлення регістра порівняння OCR0 по досягненні верхньої або нижньої межі лічби. Така синхронізація запобігає можливість виникнення несиметричних ШІМ-імпульсів непарної довжини, тим самим гарантуючи відсутність збоїв при генерації прямокутних імпульсів. Після дозволу подвійної буферизації CPU здійснює доступ до буферного регістру OCR0, а після відключення - безпосередньо адресується до регістру OCR0.

|

||||||||

|

Последнее изменение этой страницы: 2016-04-18; просмотров: 537; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.214 (0.009 с.) |