Мы поможем в написании ваших работ!

ЗНАЕТЕ ЛИ ВЫ?

|

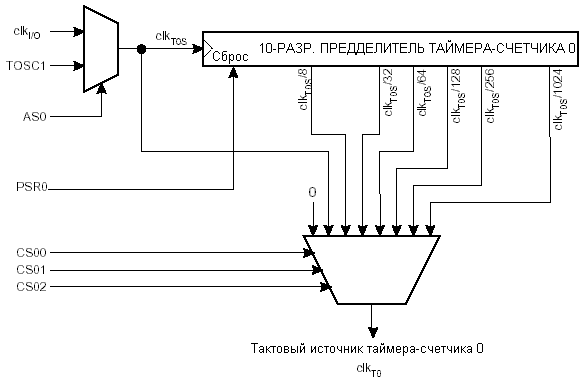

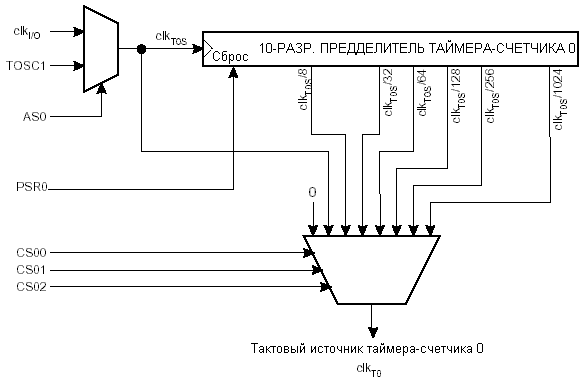

Дільник частоти таймера-лічильника 0

Дільник частоти таймер-лічильника 0

Тактове джерело таймера-лічильника 0 позначено як clkT0. По замовчуванню clkT0 підключений до системного джерела синхронізації вводу-виводу clkI/O. Шляхом установки біта AS0 в регістрі ASSR таймера-лічильника 0 тактується асинхронно з виходу TOSC1. Ця функція дозволяє використовувати таймер-лічильник 0 в якості годин реального часу (RTC[50]). Якщо AS = 1, то виводи TOSC1 і TOSC2 більше не виконують функції ліній порту С, а між ними може бути підключений кварцовий резонатор в якості окремого тактового джерела таймера-лічильника 0. Генератор оптимізований під використання кварцу на частоту 32768 Гц. Підключення до виводу TOSC1 зовнішнього тактового джерела не рекомендується.

Дільник частоти таймера-лічильника 0 дозволяє вибрати наступні тактові сигнали: clkT0S/8, clkT0S/32, clkT0S/64, clkT0S/128, clkT0S/256 і clkT0S/1024. Крім того, є можливість зупинити синхронізацію. Установка біта PSR0 в регістрі SFIOR скидає дільник частоти. Ця функція дозволяє програмісту працювати з більш прогнозованим поведінкою дільника частоти.

Регістр спеціальних функцій вводу-виводу SFIOR

| Розряд

|

|

|

|

|

|

|

|

|

| |

| TSM

| -

| -

| -

| ACME

| PUD

| PSR0

| PSR321

| SFIOR

| | Читання/запис

| Чт./Зп.

| Чт.

| Чт.

| Чт.

| Чт./Зп.

| Чт./Зп.

| Чт./Зп.

| Чт./Зп.

|

| | Поч. значення

|

|

|

|

|

|

|

|

|

|

Розряд 7 - TSM: Режим синхронізації таймера-лічильника

Установка біта TSM активізує режим синхронізації таймерів-лічильників. В даному режимі після установки біта PSR0 або PSR321 відповідний дільник частоти буде постійно перебувати в скинутому стані. У цьому стані гарантується, що всі відповідні таймери-лічильники будуть зупинені і можуть бути однаково налаштовані без ризику зміни стану одного з них під час конфігурації. Якщо після цього скинути біт TSM, то біти PSR0 і PSR321 скидаються апаратно, а таймери-лічильники починають лічбу одночасно.

Розряд 1 - PSR0: Скидання дільника частоти таймера-лічильника 0

Якщо даний біт дорівнює лог. 1, то дільник частоти таймера-лічильника 0 скидається. Даний біт зазвичай скидається апаратно відразу після установки. Якщо даний біт встановлюється, коли таймер-лічильник 0 працює в асинхронному режимі, то він залишається рівним 1 поки не скинеться дільник частоти таймера-лічильника 0. Даний біт не скидається апаратно, якщо біт TSM = 1.

Оператори над константами у AVR-асемблері

Асемблер підтримує ряд операторів, які описані тут. Чим вище пріоритет операції, тим вищий пріоритет виконання. Вирази можуть бути укладені в дужки, і такі вирази завжди обчислюються перед поєднанням з чимось поза дужками. Асоціативність бінарних операторів вказує порядок обчислення ланцюгових операторів, ліва асоціативність означає обчислюються зліва направо, тобто  , в той час як права асоціативність означає , в той час як права асоціативність означає  . Деякі оператори не асоціативні, тому значення ланцюжка не має сенсу . Деякі оператори не асоціативні, тому значення ланцюжка не має сенсу

| Символ

| Назва

| Опис

| Пріоритет операції

| Асоціативність

| Приклад

| | !

| Логічне НІ

| Унарна операція, яка повертає 1, якщо вираз був нулем і вертає 0, якщо вираз не був нулем

|

| Нема

| ldi r16,!0xf0

/*Завантаження у r16 числа 0x00

*/

| | ~

| Побітне НІ

| Унарна операція, яка вертає вхідний вираз з інвертованими всіма бітами

|

| Нема

| ldi r16, ~0xf0

/*Завантаження у r16 числа 0x0f

*/

| | -

| Унарний мінус

| Унарна операція, яка змінює знак виразу

|

| Нема

| ldi r16, -2

/*Завантаження у r16 числа -2 (0xfe)

*/

| | *

| Множення

| Операція над двома елементами виразу, яка повертає добуток двох виразів

|

| Ліва

| ldi r16, label*2

/*Завантаження у r16 числа label*2

*/

| | /

| Ділення

| Операція над двома елементами виразу, яка повертає цілу частину ділення лівої частину на праву частину

|

| Ліва

| ldi r16, label/2

/*Завантаження у r16 числа label/2

*/

| | %

| Виділення остачі (тільки для AVRASM2)

| Операція над двома елементами виразу, яка повертає остачу ділення лівої частину на праву частину

|

| Ліва

| ldi r16, label % 2

/*Завантаження у r16 числа label % 2

*/

| | +

| Додавання

| Операція над двома елементами виразу, яка повертає суму двох виразів

|

| Ліва

| ldi r16, c1+c2

/*Завантаження у r16 числа c1+c2

*/

| | -

| Віднімання

| Операція над двома елементами виразу, яка повертає результат віднімання ліва частина мінус права частина

|

| Ліва

| ldi r16, c1-c2

/*Завантаження у r16 числа c1-c2

*/

| | <<

| Зміщення вліво

| Операція над двома елементами виразу, яка повертає результат лівого зміщення лівого виразу на стільки біт, скільки вказано у правій частині

|

| Ліва

| ldi r16, c1<<c2

/*Завантаження у r16 числа c1 побітно зміщеного вліво c2 разів*/

| | >>

| Зміщення вправо

| Операція над двома елементами виразу, яка повертає результат правого зміщення лівого виразу на стільки біт, скільки вказано у правій частині

|

| Ліва

| ldi r16, c1>>c2

/*Завантаження у r16 числа c1 побітно зміщеного вправо c2 разів*/

| | <

| Менше

| Операція над двома елементами виразу, яка повертає 1, якщо вираз (враховуючи знак) зліва є меншим від виразу (враховуючи знак) справа. У іншому випадку - 0

|

| Нема

| ori r16, bitmask*(c1<c2)+1

/*Логічне АБО r16 з виразом*/

| | <=

| Менше або рівне

| Операція над двома елементами виразу, яка повертає 1, якщо вираз (враховуючи знак) зліва є меншим або рівним від виразу (враховуючи знак) справа. У іншому випадку - 0

|

| Нема

| ori r16, bitmask*(c1<=c2)+1

/*Логічне АБО r16 з виразом*/

| | >

| Більше

| Операція над двома елементами виразу, яка повертає 1, якщо вираз (враховуючи знак) зліва є більшим від виразу (враховуючи знак) справа. У іншому випадку - 0

|

| Нема

| ori r16, bitmask*(c1>c2)+1

/*Логічне АБО r16 з виразом*/

| | >=

| Більше або рівне

| Операція над двома елементами виразу, яка повертає 1, якщо вираз (враховуючи знак) зліва є більшим або рівним від виразу (враховуючи знак) справа. У іншому випадку - 0

|

| Нема

| ori r16, bitmask*(c1>=c2)+1

/*Логічне АБО r16 з виразом*/

| | ==

| Рівне

| Операція над двома елементами виразу, яка повертає 1, якщо вираз (враховуючи знак) зліва є рівним виразу (враховуючи знак) справа. У іншому випадку - 0

|

| Нема

| ori r16, bitmask*(c1==c2)+1

/*Логічне АБО r16 з виразом*/

| | !=

| Не рівне

| Операція над двома елементами виразу, яка повертає 1, якщо вираз (враховуючи знак) зліва є рівним виразу (враховуючи знак) справа. У іншому випадку - 0

|

| Нема

| .EQU flag=(c1!=c2)

/*

Встановлення символьної константи рівною 1 або 0

*/

| | &

| Побітне І

| Операція над двома елементами виразу, яка повертає побітне І між двома виразами

|

| Ліва

| ldi r16, High(c1&c2)

/*Завантаження у r16 виразу*/

| | ^

| Побітне ВИКЛЮЧАЮЧЕ АБО

| Операція над двома елементами виразу, яка повертає побітне ВИКЛЮЧАЮЧЕ АБО між двома виразами

|

| Ліва

| ldi r16, High(c1^c2)

/*Завантаження у r16 виразу*/

| | |

| Побітне АБО

| Операція над двома елементами виразу, яка повертає побітне АБО між двома виразами

|

| Ліва

| ldi r16, High(c1|c2)

/*Завантаження у r16 виразу*/

| | &&

| Логічне І

| Операція над двома елементами виразу, яка повертає 1, якщо два вирази є ненульовими, у іншому випадку - 0

|

| Ліва

| ldi r16, High(c1&&c2)

/*Завантаження у r16 виразу*/

| | ||

| Логічне АБО

| Операція над двома елементами виразу, яка повертає 1, якщо два вирази є ненульовими, у іншому випадку - 0

|

| Ліва

| ldi r16, High(c1||c2)

/*Завантаження у r16 виразу*/

| | ?

| Умовний оператор (тільки для AVRASM2.1)

| Синтаксис

умова? вираз 1: вираз 2

Опис

Термальний (трійний) оператор, який повертає значення виразу 1, якщо умова справджується, у іншому випадку – вираз 2.

|

| Нема

| ldi r16, a>b? a:b

/*Завантаження у r16 більшого числа між a і b*/

| Регістри вводу/виводу (які треба знати при виконанні цієї лабораторної роботи)

| Адреса

| Номер регістру вводу/виводу[51]

| Назва

| Біт 7

| Біт 6

| Біт 5

| Біт 4

| Біт 3

| Біт 2

| Біт 1

| Біт 0

| | Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128

| | $65

|

| PORTG

| -

| -

| -

| PORTG4

| PORTG3

| PORTG2

| PORTG1

| PORTG0

| | $64

|

| DDRG

| -

| -

| -

| DDG4

| DDG3

| DDG2

| DDG1

| DDG0

| | $63

|

| PING

| -

| -

| -

| PING4

| PING3

| PING2

| PING1

| PING0

| | $62

|

| PORTF

| PORTF7

| PORTF6

| PORTF5

| PORTF4

| PORTF3

| PORTF2

| PORTF1

| PORTF0

| | $61

|

| DDRF

| DDF7

| DDF6

| DDF5

| DDF4

| DDF3

| DDF2

| DDF1

| DDF0

| | $60

|

| Резерв

| -

| -

| -

| -

| -

| -

| -

| -

| | $5F

| $3F

| SREG

| I

| T

| H

| S

| V

| N

| Z

| C

| | $5E

| $3E

| SPH

| SP15

| SP14

| SP13

| SP12

| SP11

| SP10

| SP9

| SP8

| | $5D

| $3D

| SPL

| SP7

| SP6

| SP5

| SP4

| SP3

| SP2

| SP1

| SP0

| | Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128

| | $57

| $37

| TIMSK

| OCIE2

| TOEI2

| TICIE1

| OCIE1A

| OCIE1B

| TOIE1

| OCIE0

| TOIE0

| | $56

| $36

| TIFR

| OCF2

| TOV2

| ICF1

| OCF1A

| OCF1B

| TOV1

| OCF0

| TOV0

| | Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128

| | $53

| $33

| TCCR0

| FOC0

| WGM00

| COM01

| COM00

| WGM01

| CS02

| CS01

| CS00

| | $52

| $32

| TCNT0

| Регістр таймера-лічильника 0 (8 біт)

| | $51

| $31

| OCR0

| Регістр порогу порівняння таймера-лічильника 0

| | $50

| $30

| ASSR

| -

| -

| -

| -

| AS0

| TCN0UB

| OCR0UB

| TCR0UB

| | Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128

| | $40

| $20

| SFIOR

| TSM

| -

| -

| -

| ACME

| PUD

| PSR0

| PSR321

| | Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128

| | $3B

| $1B

| PORTA

| PORTA7

| PORTA6

| PORTA5

| PORTA4

| PORTA3

| PORTA2

| PORTA1

| PORTA0

| | $3A

| $1A

| DDRA

| DDA7

| DDA6

| DDA5

| DDA4

| DDA3

| DDA2

| DDA1

| DDA0

| | $39

| $19

| PINA

| PINA7

| PINA6

| PINA5

| PINA4

| PINA3

| PINA2

| PINA1

| PINA0

| | $38

| $18

| PORTB

| PORTB7

| PORTB6

| PORTB5

| PORTB4

| PORTB3

| PORTB2

| PORTB1

| PORTB0

| | $37

| $17

| DDRB

| DDB7

| DDB6

| DDB5

| DDB4

| DDB3

| DDB2

| DDB1

| DDB0

| | $36

| $16

| PINB

| PINB7

| PINB6

| PINB5

| PINB4

| PINB3

| PINB2

| PINB1

| PINB0

| | $35

| $15

| PORTC

| PORTC7

| PORTC6

| PORTC5

| PORTC4

| PORTC3

| PORTC2

| PORTC1

| PORTC0

| | $34

| $14

| DDRC

| DDC7

| DDC6

| DDC5

| DDC4

| DDC3

| DDC2

| DDC1

| DDC0

| | $33

| $13

| PINC

| PINC7

| PINC6

| PINC5

| PINC4

| PINC3

| PINC2

| PINC1

| PINC0

| | $32

| $12

| PORTD

| PORTD7

| PORTD6

| PORTD5

| PORTD4

| PORTD3

| PORTD2

| PORTD1

| PORTD0

| | $31

| $11

| DDRD

| DDD7

| DDD6

| DDD5

| DDD4

| DDD3

| DDD2

| DDD1

| DDD0

| | $30

| $10

| PIND

| PIND7

| PIND6

| PIND5

| PIND4

| PIND3

| PIND2

| PIND1

| PIND0

| | Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128

|

Це корисно!

Для зручності використання AVR Studio при написанні програм для різних мікроконтролерів, у яких регістри вводу/виводу чи розширених регістрів вводу/виводу, а також деяких перепозначень регістрів регістрового файлу (зокрема X, Y і Z), абсолютні адреси яких у різних мікроконтролерах можуть бути різні, але назва і функціональне призначення є однакове – розробниками AVR Studio у папці \Program Files\Atmel\AVRTools\AVRAssembler\Аppnotes\ знаходяться *.inc файли у яких директивами EQU і DEF описані визначені всі регістри і відповідні біти регістрів, а також здійснено деякі визначення.

У цьому файлі також визначені символьними змінними номери бітів регістрів вводу виводу.

Зокрема,

.equ WGM01 = 3

Це опис біту WGM01 (номер його є 3) регістру TCCR0, який відноситься до регістрів вводу виводу і відповідає за налаштування таймера-лічильника 0 мікроконтролера ATMEGA128

Для того, щоб включити у проект визначення регістрів мікроконтролера ATMEGA128 треба в проект включити m128def.inc файл.

|

, в той час як права асоціативність означає

, в той час як права асоціативність означає  . Деякі оператори не асоціативні, тому значення ланцюжка не має сенсу

. Деякі оператори не асоціативні, тому значення ланцюжка не має сенсу