Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Триггеры, регистры, счетчикиСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Логические элементы служат основой для создания более сложных цифровых устройств, одним из которых является триггер. Триггер – это целый класс электронных устройств, которые могут длительно находиться в одном из двух устойчивых состояний после прекращения сигнала, меняющего состояние. Состояние выхода триггера определяется не только сигналами на его входах, но и предыдущим состоянием устройства. Таким образом, триггер является простейшей однобитной ячейкой памяти. RS-триггер Самый простой триггер можно получить из двух логических элементов 2ИЛИ-НЕ:

Рис. 30. Схема триггера на основе двух логических элементов и его обозначение на схемах

Такая схема представляет собой асинхронный RS-триггер. Он имеет два входа: S (set) – установка, R (reset) – сброс, и два выхода: Q (прямой) и Q с чертой сверху (инверсный, НЕ_Q). При подаче сигнала логического нуля на оба входа триггера, его выходы будут установлены в произвольное состояние. Допустим, Q = 0, а НЕ_Q =1. Если на вход S подать «1», то состояние выхода Q скачкообразно изменится на «1», а НЕ_Q - на «0». И это состояние будет поддерживаться в независимости от того «0» или «1» подано на вход S, что и является проявлением свойства памяти.

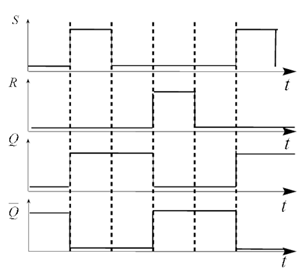

Рис. 31. Временные диаграммы работы RS - триггеров.

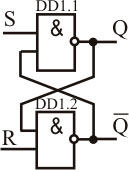

Соответственно, при подаче уровня «1» на вход R выход Q станет «0», а НЕ_Q – «1». Длительность устанавливающих импульсов может быть очень короткой, и ограничена физическим быстродействием логических модулей, из которых построен триггер. Ситуация, когда на входах R и S действует высокий уровень, является недопустимой, поскольку при этом схема не может работать корректно. В этом есть недостаток RS-триггера. RS-триггер также можно построить из двух элементов И-НЕ, такие элементы более распространены:

Рис. 31. Триггер на основе элементов 2И-НЕ

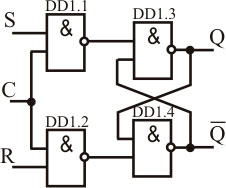

Установка и сброс триггера на элементах 2И-НЕ, в отличие от предыдущего, производится низким уровнем входного сигнала. Если к последней схеме добавить еще два вентиля 2И-НЕ, то мы получим синхронный RS-триггер.

Рис. 32. Синхронный RS - триггер.

Изменение состояния такого триггера производится только при воздействии на вход С (Clock) синхронизирующего (тактового) импульса. Поэтому такие триггеры иногда называют тактируемыми.

Рис. 33. Временные диаграммы работы синхронного RS - триггера.

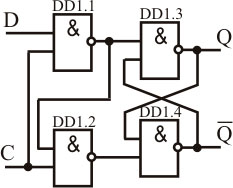

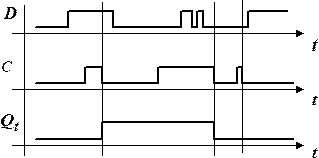

D-триггер Немного изменив схему синхронного RS-триггера, можно получить D-триггер. (D-delay, задержка). У него только один информационный вход D. Если на этот вход подать «1», а затем подать импульс на вход C, то на выходе Q будет «1», если на вход подать «0», затем импульс на C, то на выходе Q будет «0». Таким образом, D-триггер осуществляет фиксацию информации, поступающей на вход. Иногда такой триггер называют триггер - защёлку, т.к. он как бы защёлкивает состояние на входе D в момент прихода импульсов на вход С, и не реагирует на изменение состояния входа D в промежутках между этими импульсами (рисунок

Рис. 34. Схема D - триггера на основе 2И-НЕ элементов.

На рисунке 35 приведена временная диаграмма работы D -триггера.

Рис. 35. Временные диаграммы работы D- триггера.

Если вход D соединить с выходом НЕ_Q, то триггер будет менять свое состояние при каждом изменении состояния входа С от «0» к «1». При изменении от «1» к «0» состояние триггера меняться не будет. Таким образом, частота выходных импульсов будет вдвое меньше частоты входных импульсов. Такой триггер называется счетным или T-триггером. Делитель частоты используется очень широко в цифровой технике.

Рис. 36. Работа Т-триггера.

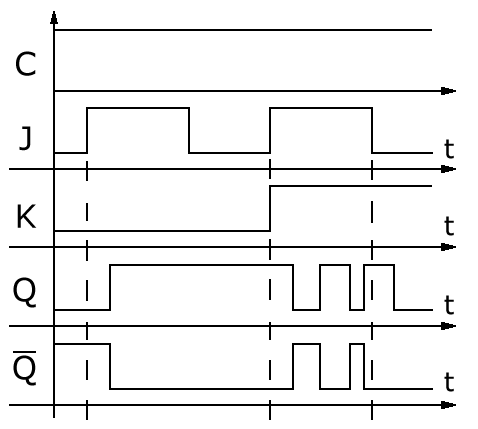

Существует разновидность синхронного RS-триггера, не имеющая запрещенной комбинации – JK-триггер. Он имеет три входа: J (вместо R), K (вместо S), и C. Если на оба информационных входа подана «1», то JK-триггер работает как счетный T-триггер с входом C.

Рис. 37. Работа JK - триггера.

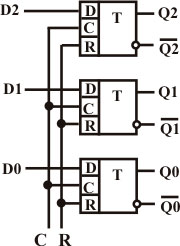

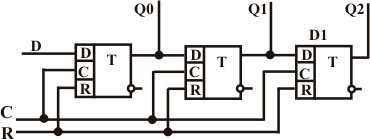

Регистр хранения На триггерах можно строить более сложные цифровые устройства, например, такие, как регистры. Регистры предназначены для хранения многобитовой информации, то есть чисел, записанных в двоичном коде. Рассмотри трех битовый регистр хранения на D-триггерах:

Рис. 38. Регистр хранения (или памяти).

Каждый триггер может хранить один разряд (бит) числа. Вход R служит для установки выходов всех триггеров в нулевое (исходное) состояние перед записью числа, которое подается на входы D0,D1 и D2. При подаче импульса на вход C производится запись информации с этих входов. Информация может храниться сколь угодно долго, пока на вход С не подаются импульсы и подается питание. Регистр сдвига Другой разновидностью регистров является регистр сдвига. Он предназначен для преобразования информации путем ее побитного сдвига в ту или иную сторону. На следующем рисунке приведена схема простейшего регистра сдвига информации вправо (по схеме):

Рис. 39. Регистр сдвига

В отличие от регистра хранения выход предыдущего триггера соединен с входом последующего. Информация в виде логического уровня подается на вход первого (крайнего слева) триггера. При воздействии импульса на входе C присутствующая на входе D информация записывается в первый триггер. При подаче второго импульса информация из первого триггера переписывается во второй триггер, а в первый записывается информация, которая в этот момент присутствует на входе D, и так далее. Таким образом, с подачей каждого синхроимпульса информация в регистре сдвигается вправо на 1 разряд. Сдвиговые регистры используются во многих схемотехнических решениях при построении цифровых устройств, прежде всего для преобразования последовательного кода в параллельный, а также для выполнения арифметических операций (умножения и деления на 2)с двоичными числами, организации линий задержки, формирования импульсов заданной длительности, генерирования псевдослучайных последовательностей (кодов) и т.п.

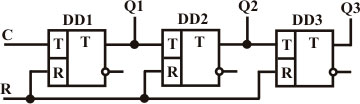

Счетчик Еще один класс цифровых устройств, которые можно построить на триггерах – счетчики. Как следует из названия, они осуществляют счет входных импульсов в заданном коде и могут хранить результат. Простейший счетчик с последовательным переносом можно получить с помощью счетных T-триггеров:

Рис. 40. Счётчик с последовательным переносом.

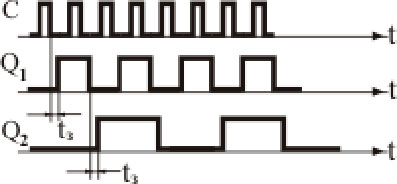

Рис. 41. Временные диаграммы работы счётчика

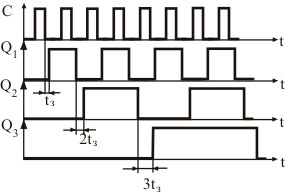

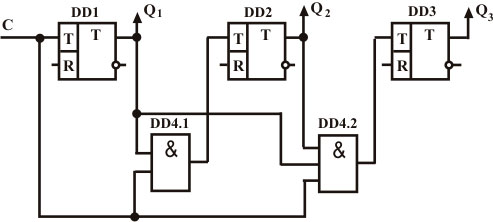

Подачей импульса на вход R счетчик приводится в исходное состояние, когда на выходах Q1-Q3 – уровень логического нуля. На вход C подаются импульсы для счета. С приходом заднего фронта первого импульса первый (левый) по схеме триггер устанавливается в «1». Если читать код справа налево, то он соответствует единице. Для нашего трехразрядного счетчика это код 001. С приходом второго импульса в «1» переключается второй триггер, а первый переключается в «0». Таким образом, код на выходах счетчика будет 010, что соответствует десятичной цифре 2. Следующий импульс установит код 011, то есть 3. Трехразрядный счетчик может досчитать до кода 111, что соответствует десятичной цифре 7. При этом наступает так называемое переполнение счетчика, и с приходом следующего импульса счетчик обнулится. Поскольку триггеры счетчика соединены последовательно, то и переключаться они будут также последовательно. Этот процесс отображен на графике, из которого видно, что время задержки переключения tз будет удваиваться и утраиваться. С увеличением числа разрядов задержка может оказаться неприемлемой, что является недостатком счетчиков с последовательным переносом. Для повышения быстродействия применяются счетчики с параллельным переносом, что достигается одновременной подачей входных импульсов на входы всех триггеров счетчика. Это реализуется с помощью введения в схему логических элементов И:

Рис. 42. Счётчик с параллельным переносом.

Рис. 43. Работа счётчика с параллельным переносом

Из схемы видно, что на вход второго триггера счетный импульс поступит только тогда, когда на выходе первого триггера будет «1», а на третий – когда «1» будет на выходах и первого, и второго триггеров. Очевидно, что с увеличением числа разрядов необходимо увеличивать как число логических элементов И, так и число их входов, что, в свою очередь, является недостатком такого типа счетчиков. Регистры и счетчики, в свою очередь, могут применяться для построения более сложных цифровых устройств: сумматоров, ОЗУ и ПЗУ (оперативных и постоянных запоминающих устройств), АЛУ (арифметическо-логических устройств), входящих в состав процессоров, и так далее, к все более сложным цифровым устройствам.

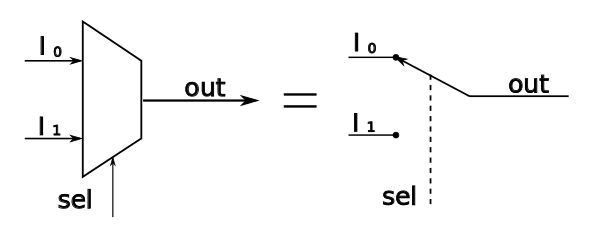

Мультиплексор Mультипле́ксор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из нескольких входов на один выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

Рис. 44. Схема мультиплексора 2-к-1.

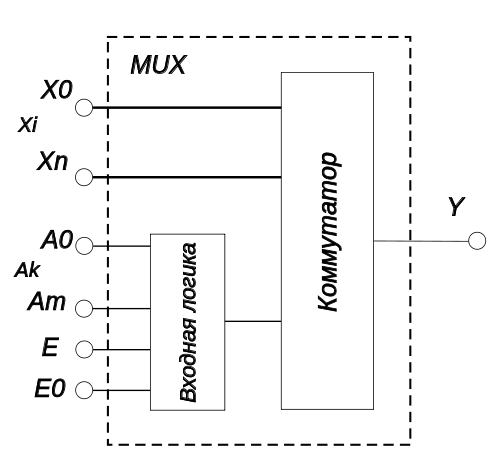

Аналоговые и цифровые мультиплексоры значительно различаются по принципу работы. Первые электрически соединяют выбранный вход с выходом (при этом сопротивление между ними невелико — порядка сотен или десятков ом). Вторые же не образуют прямого электрического соединения между выбранным входом и выходом, а лишь «копируют» на выход логический уровень ('0' или '1') с выбранного входа. Аналоговые мультиплексоры иногда называют ключами или коммутаторами. Устройство, противоположное мультиплексору по своей функции, называется демультиплексором. В случае применения аналоговых мультиплексоров (с применением ключей на полевых транзисторах) не существует различия между мультиплексором и демультиплексором; такие устройства могут называться коммутаторами. Устройство Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Коммутатор обслуживает управляющая схема, в которой имеются адресные входы и, как правило, разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов и числом адресных входов действует соотношение, то такой мультиплексор называют полным. Если, то мультиплексор называют неполным. Разрешающие входы используют для расширения функциональных возможностей мультиплексора. Они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, то есть могут блокировать действие всего устройства. В качестве управляющей схемы обычно используется дешифратор. В цифровых мультиплексорах логические элементы коммутатора и дешифратора обычно объединяются. Обобщённая схема мультиплексора

Рис. 45. Обобщённая схема мультиплексора.

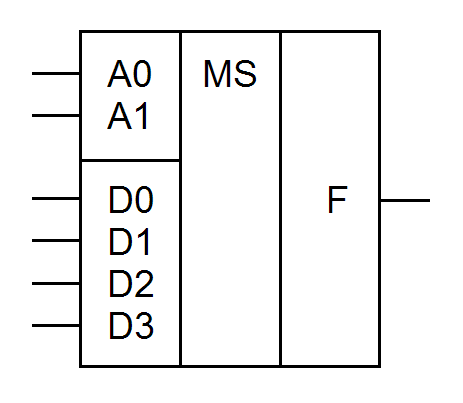

Входные логические сигналы Xi поступают на входы внутреннего коммутатора и через коммутатор передаются на выход Y. На вход управляющей схемы подаётся слово адресных сигналов Ak (от англ. Address). Мультиплексор также может иметь дополнительный управляющий вход E (от англ. Enable), иногда этот вход обозначают на схемах CS (от англ. Chip Select — «выбор микросхемы»), который разрешает или запрещает прохождение входного сигнала на выход Y. Логический уровень разрешающего сигнала в разных конкретных моделях мультиплексоров может быть как логическая 1, так и логический 0, но в подавляющем количестве типов мультиплексоров выпускаемых промышленностью разрешающий сигнал логический 0. В разных типах мультиплексоров при запрещающем состоянии передачи на входе E на выходе Y может быть состояние 0 или 1. Кроме этого, некоторые мультиплексоры имеют выход, который может принимать три состояния: два логических состояния 0 и 1, и третье состояние — отключённый выход (высокоимпедансное состояние, часто говорят, Z -состояние — выходное сопротивление велико, выходной внутренний логический вентиль отключается от выхода специальным внутренним ключом). Такое техническое решение облегчает наращивание количества входных сигналов мультиплексора каскадированием нескольких микросхем мультиплексоров, при этом выходы микросхем просто электрически соединяются. Перевод мультиплексора в третье состояние производится подачей на вход OE (от англ. Output Enable) логической 1, чаще логического 0 — опять же зависит от модели конкретного мультиплексора. Использование Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах, сдвигающих устройствах и др. Мультиплексоры могут использоваться для преобразования параллельного двоичного кода в последовательный. Для такого преобразования достаточно подать на информационные входы мультиплексора параллельный двоичный код, а сигналы на адресные входы подавать в такой последовательности, чтобы к выходу поочередно подключались входы, начиная с первого и заканчивая последним. Обозначение Мультиплексоры обозначают сочетанием MUX (от англ. multiplexer), а также MS (от англ. multiplexer selector).

Рис. 46. Условное графическое обозначение (УГО) мультиплексора «4 в 1».

Демультиплексор

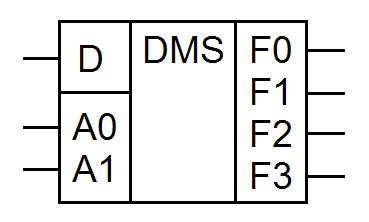

Рис. 47. Условное графическое обозначение (УГО) демультиплексора «1 в 4».

Демультиплексор — это логическое устройство, предназначенное для переключения сигнала с одного информационного входа на один из информационных выходов. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. На схемах демультиплексоры обозначают через DM или DMS. Суть и схема реализации В случае ТТЛ логики для коммутации каналов применяются логические элементы "И". В КМОП-микросхемах широко применяются ключи на полевых транзисторах. Поэтому в них отсутствует понятие демультиплексора. Информационные входы и выход можно поменять местами, в результате чего мультиплексор может служить в качестве демультиплексора. Если между числом выходов и числом адресных входов действует соотношение n=2m для двоичных демультиплексоров или n=3m для троичных демультиплексоров, то такой демультиплексор называют полным. Если n<2m для двоичных демультиплексоров или n<3m для троичных демультиплексоров, то демультиплексор называют неполным. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют функцию входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров в отечественных микросхемах используются одинаковые буквы — ИД. Демультиплексоры выполняют унарные (одновходовые, однооперандные) логические функции с n-арным выходом.

|

||||

|

Последнее изменение этой страницы: 2021-07-18; просмотров: 487; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.133.153.224 (0.01 с.) |