Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Реверсивные двоичные счетчики

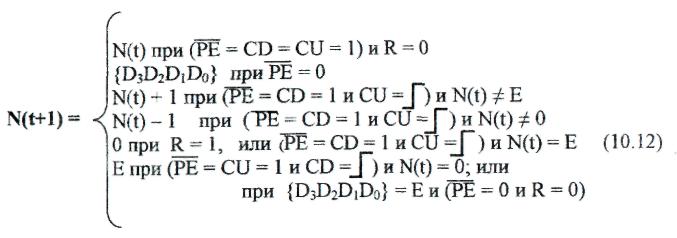

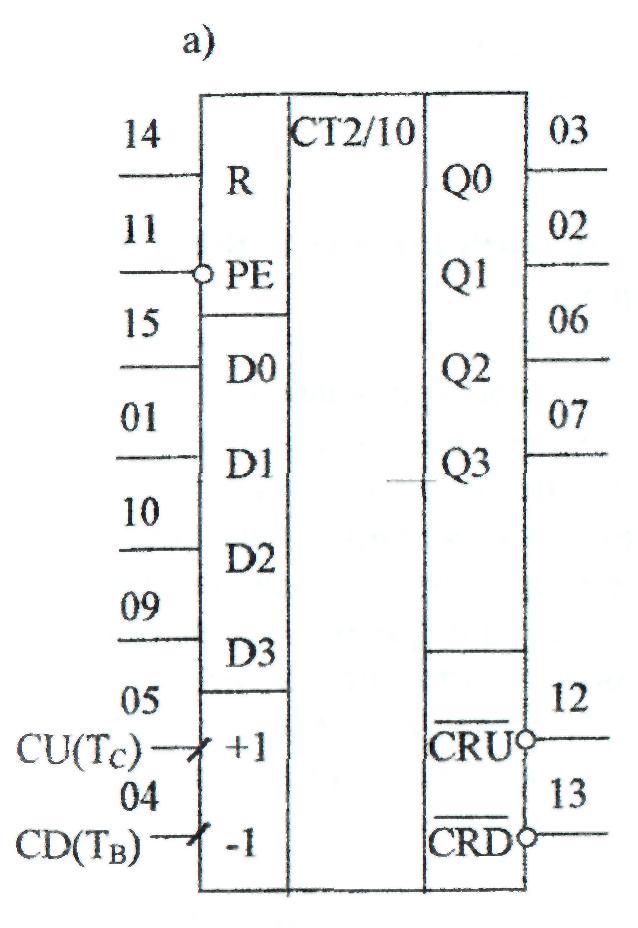

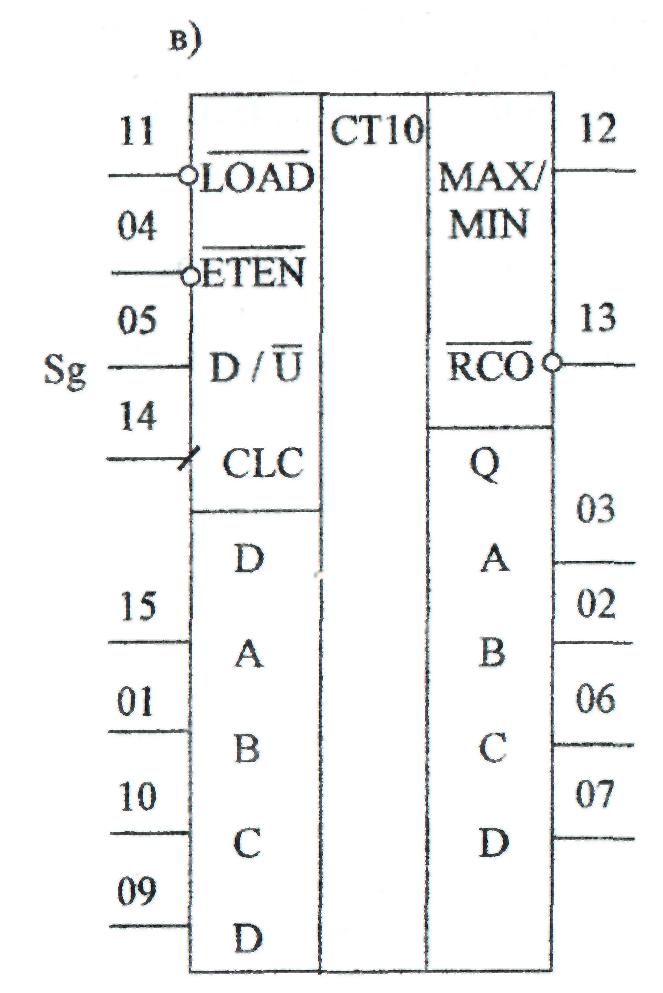

Промышленность выпускает две основные разновидности реверсивных двоичных счетчиков, условное графическое обозначение которых представлено на рис. 10.7(a) и (б). Первая из указанных разновидностей счетчиков содержит раздельные тактовые динамические входы счета на уменьшение CD и на увеличение CU соответственно. Направление счета определяется тем, на какой из тактовых входов подается положительный перепад (фронт) импульсного сигнала. При этом на второй тактовый вход должен быть подан высокий («единичный») уровень напряжения. Примером реверсивных двоичных счетчиков первой разновидности могут служить счетчики типа КР1533ИЕ7, КР1554ИЕ7, К555ИЕ7. Для предварительной записи в счетчик необходимого числа необходимо подать его на информационные входы { D 3 D 2 D 1 D 0 }, а на вход В соответствии с изложенным выше алгоритм управления работой счетчика рис. 10.7(a) может быть представлен следующей системой уравнений: 23

Вторая из указанных разновидностей реверсивных двоичных счетчиков (рис. 10.7.б) содержит вход D/

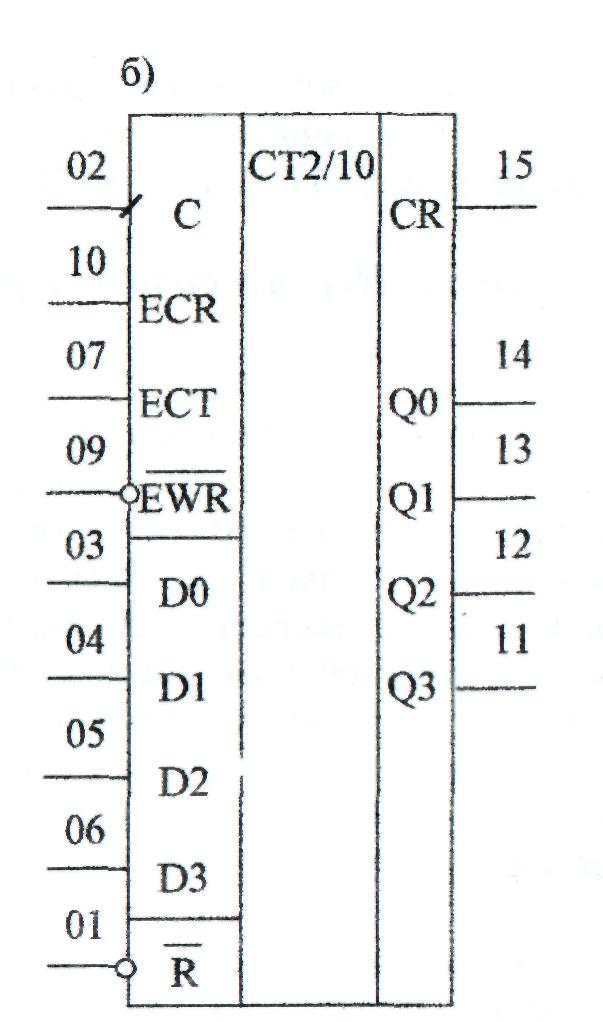

В счетчиках рис. 10.7(б) прямой счет осуществляется при низком уровне напряжения на входе выбора направления счета а обратный – при высоком уровне напряжения на этом входе. При этом на входе разрешения счета ETEN должен быть установлен низкий уровень напряжения, вследствие чего срабатывание счетчика будет происходить по положительному фронту тактового импульса на входе CLC. Асинхронная установка счетчика в состояние, заданное на входах A, B, C, D производится при подаче низкого уровня напряжения на входе разрешения предустановки 24 Из числа выпускаемых промышленностью интегральных микросхем реверсивных двоичных счетчиков второй разновидности можно привести в качестве примера ИМС типа К555 ИЕ13, КР1533 ИЕ13. 10.5.3. Нереверсивные и реверсивные двоично-десятичные

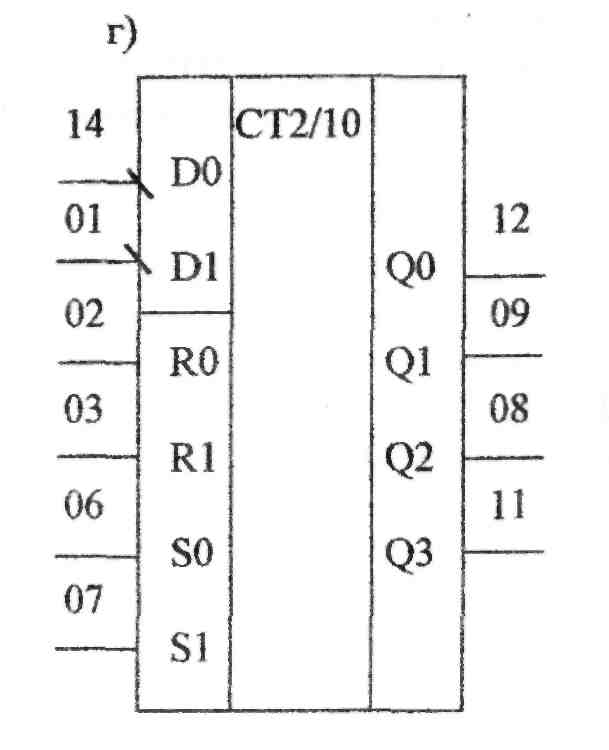

счетчики Условные графические обозначения ИМС нереверсивных двоично-десятичных счетчиков приведены на рис. 10.8(б) и (г), а ИМС реверсивных счетчиков - на рис. 10.8(a) и (в). Сравнение интегральных микросхем двоичных счетчиков рис. 10.6(б) и двоично-десятичных счетчиков рис. 10.8(б) показывает, что указанные счетчики имеют одинаковую систему управляющих входов. Таким образом, алгоритм управления двоично-десятичных счетчиков рис. 10.8(б) может быть описан системой уравнений (10.9), представленной в разделе 10.5.1 применительно к двоичным счетчикам рис. 10.6(б). Вместе с тем, необходимо сделать некоторые уточняющие замечания: • Система уравнений (10.9) справедлива для описания работы двоично - десятичных счетчиков рис.10.8(б) в нормальном счетном режиме при Е = 9, как без использования предварительной параллельной загрузки данных { D 3 D 2 D 1 D 0}, так и с их загрузкой при условии, что код загруженного в счетчик числа не превышает число 9, то есть { D 3 D 2 D 1 D 0} ≤ {1001}. • При параллельной загрузке в счетчик рис. 10.8(б) кода числа { D 3 D 2 D 1 D 0} > {1001} его работа будет развиваться в соответствии с той частью графа переходов рис.10.3, которая относится к его вершинам 10, 11, 12, 13, 14, 15 со втекающими в них и вытекающими из них ориентированными дугами ребер графа. Двоично - десятичные счетчики КР1533 ИЕ9, К555 ИЕ9, КР1533 ИЕ11 имеют структуру и систему управления их работой, аналогичную описанной выше. Четырехразрядный двоично-десятичный счетчик, условное графическое обозначение которого представлено на рис.10.8(г), содержит две секции: счетчик - делитель на 2 и трехразрядный счетчик - делитель на 5. Каждая секция может использоваться отдельно. Для получения десятичного счетчика используется внешняя связь с входа Qo 25

Рис. 10.8. Условное графическое обозначение двоично-десятичных счетчиков.

26

первой секции счетчика на вход D1 второй трехразрядной секции счетчика. Алгоритм управления работой десятичного счетчика рис.10.8(г) может быть описан следующей системой уравнений:

В системе уравнений (10.14) для данного счетчика имеем: Е = 9(1001). Отметим, что в соответствии с указанной системой уравнений реализуется управление работой ИМС четырехразрядных двоично-десятичных счетчиков типа КР1533 ИЕ2, КМ155 ИЕ2 и других аналогичных им ИМС.

Интегральные микросхемы рис. 10.8(a) представляют собой четырехразрядные реверсивные двоично-десятичные счетчики с асинхронной предустановкой, асинхронным сбросом и раздельными тактовыми входами счета на увеличение CD и на уменьшение CU. Иными словами, эти счетчики по алгоритму управления их функционированием могут быть отнесены к описанному выше первому типу реверсивных счетчиков. При Е = 9(1001) алгоритм управления работой счетчика рис.10.8 (а) может быть описан системой уравнений (10.12). Примером счетчиков, представленного здесь типа, являются ИМС реверсивных двоично - десятичных счетчиков КР1533 ИЕ6, KP 1554 ИЕ6, КМ155 ИЕ6 и др.

ИМС рис. 10.8(b) представляет собой четырехразрядный синхронный двоично-десятичный реверсивный счетчик второго типа. В качестве примера такого счетчика можно привести ИМС КР1533 ИЕ12. Предлагаем читателям самостоятельно составить систему уравнений, описывающую алгоритм управления двоично-десятичных реверсивных счетчиков данной разновидности.

27 10.6. Каскадное построение счётчиков

Для построения счётчиков с высоким значением модуля счёта Кк интегральные микросхемы счётчиков с малым значением их модулей Kj могут быть соединены каскадно. В этом случае выходы переноса ИМС счётчиков младших разрядов соединяют со счётными входами ИМС счётчиков старших разрядов (рис. 10.9)

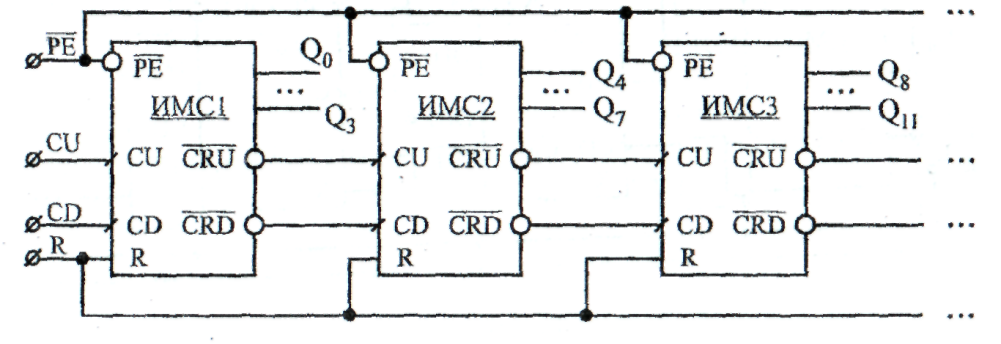

Модуль счёта Кк счётчика, полученного в результате каскадного соединения, равен

Это означает, что на выходе переноса последнего счётчика каскадного соединения импульсный сигнал формируется при поступлении каждого Кк тактового сигнала. Таким образом, при использовании указанного выхода переноса счетчика в качестве информационного, счётчик может выполнять функции делителя частоты ft входных сигналов в Kk раз. То есть

Аналогично этому на промежуточных выходах переноса счётчика могут быть получены импульсные сигналы с частотой (ƒ1/ K 1 · K 2);(ƒ1/ K 1 · K 2 · K 3) и т.д. 28 Каскадный счётчик рис. 10.9 работает следующим образом. Пусть в начальный момент все ИМС счётчиков находятся в нулевом состоянии, {N1=0; N2=0,...,NN =0}. После подачи K1 импульсов на счётный вход первой ИМС в ней возникает ситуация переполнения и на её выходе переноса формируется сигнал переноса, который поступает на счётный вход второй ИМС и воспринимается ею, как счётный. При этом код числа N1, зафиксированный в первой ИМС принимает значение 0, а код N2 числа во второй ИМС увеличивается на единицу. После подачи на вход первой ИМС ещё К1 импульсов ситуация повторится.

Одновременное переполнение двух первых ИМС наступает после подачи на вход (К1 · К2) импульсов, трёх первых ИМС - после подачи (К1·К2 ·К3) импульсов, а одновременное переполнение всех ИМС каскадного счётчика - после подачи на его счётный вход Кк импульсов. Общее число импульсов N, сосчитанных каскадным счётчиком, равно N = (K1K2·…·KN_1) ·NN + (K 1 ·K2·…·KN-2) ·NN-1+...+ K1·K2·N3 +K1·N2 + N1 (10.17) где N 1, N 2,..., NN - число импульсов, сосчитанное 1 -й, 2-й,..., N -й ИМС каскадного счётчика. В том случае, когда соединяемые ИМС счётчиков имеют одинаковые модули счёта К = К 2 =... = К N = К соотношение (10.17) преобразуется к виду N= KN-1 ·NN + KN-2·NN-1 +...+K1 ·N2 +K° ·N 1 (10.18) Анализ соотношения (10.18) показывает, что каскадный счётчик, построенный на интегральных микросхемах с одинаковым модулем счёта, можно рассматривать как счётчик, выходной, код которого представляет число в позиционной системы счисления по основанию К. При каскадном построении счётчиков важную роль играет процесс формирования сигналов на выходах переноса ИМС, образующих каскадированный счётчик. Рассмотрим особенности каскадного построения счётчиков на примере реализации реверсивных счётчиков с высоким значением модуля счёта Кк. 29 10.6.1. Каскадные счётчики на основе ИМС реверсивных счёт чиков первого типа. Интегральные микросхемы реверсивных счетчиков первого типа содержат два выхода переноса: • инверсный выход прямого переноса

• инверсный выход обратного переноса Формирование сигналов на указанных выходах осуществляется в соответствии со следующей системой уравнений: • • Режим прямого счёта

• • Режим обратного счёта

где N (t) - предыдущее состояние счётчика; N (t +1) - текущее состояние счётчика, ∫ - фронт сигнала. Соотношения (10.19), (10.20) совместно с полученными ранее соотношениями (10.12) описывают алгоритм функционирования ИМС реверсивных счётчиков первого типа. Анализ указанных соотношений показывает, что при каскадном соединении ИМС данного типа должны быть выполнены следующее операции:

• В каскадированной цепочке ИМС реверсивных счётчиков выходы прямого переноса цепочке, а выходы обратного переноса • Для обеспечения возможности установки каскадного счётчика в исходное (нулевое) состояние R - входы всех его ИМС соединяют в параллель. Аналогично этому соединяют входы разрешения параллельной загрузки

30

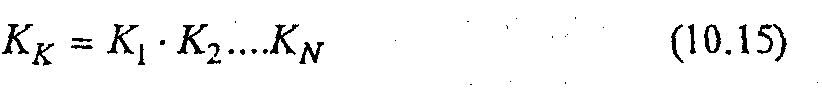

Блок-схема рис. 10.10 иллюстрирует построение реверсивного каскадного счётчика на основе интегральных микросхем реверсивных двоичных счётчиков первого типа. Заметим, что в указанной схеме тактовые входы счёта на увеличение CU и счёта на уменьшение CD первой в каскадном соединении микросхемы (ИМС1) являются соответственно входами CU и CD каскадного счётчика в целом, а информационные выходы Q 0, Q 1, Q 2, Q 3 этой ИМС являются выходными его младших разрядов.. В свою очередь объединённые в параллель R - входы (

Рис.10.10 Из рис. 10.9 и рис.10.10 видно, что при каскадном построении счётчиков распространение сигналов переноса происходит последова тельно: от ИМС1 - к ИМС2; от ИМС2 - к ИМСЗ;...; от HMCn-i - к ИМСN. Поэтому время задержки распространения сигналов Тзд в каскадном счётчике с последовательным переносом определяется соотношением

где N- число ИМС в каскадном соединении. Известно, что каскадное построение счётчиков с последовательным переносом (рис. 10.9, рис.10.10) характеризуется снижением их быстродействия, приводит к возникновению неоднозначности счёта и ложным срабатываниям, присущим в принципе асинхронным счётчикам с последовательным переносом. Эти недостатки могут быть уст- 31 ранены при синхронном построении каскадных счетчиков с реализацией в них параллельного переноса. На рис. 10.11 приведена блок - схема, иллюстрирующая построение синхронного каскадного счётчика, в котором осуществляются па раллельный перенос информации между ИМС реверсивных двоичных счётчиков И MC 1, ИМС2,... И MCN первого типа. Все ИМС каскадного счётчика в режиме счёта работают по переднему фронту сигналов на их тактовых входах CU 1, CU 2,..., CUN (CD1, CD2,..., CDN).

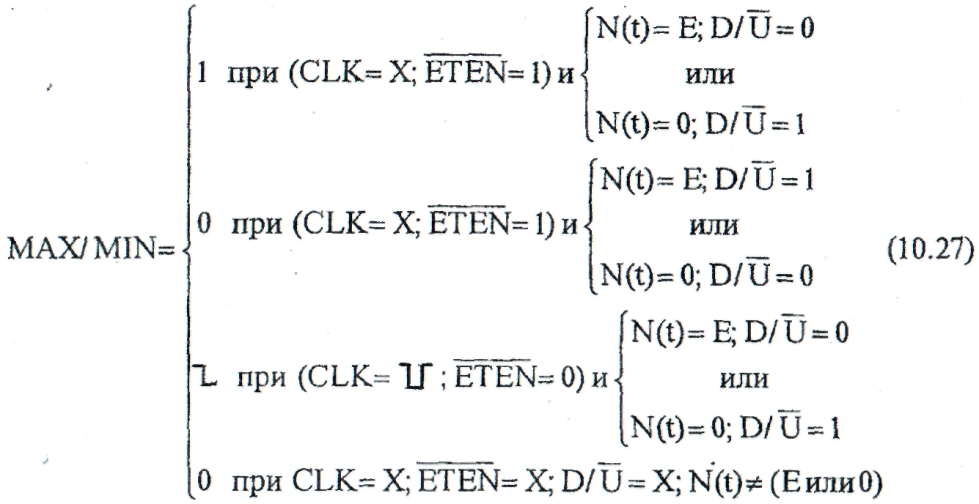

Для обеспечения синхронной работы каскадного счётчика в целом и каждого его каскада (то есть ИМС1, ИМС2,... ИМС N) сигналы прямого (обратного) переноса

С U = С U = где j Каскадный счётчик рис. 10.11 работает следующим образом. Интегральная микросхема ИМС1 выполняет прямой (обратный) счёт входных импульсов CUBX (CDBX) от 0 до Е1 (от E 1 до 0), после чего на её выходе 32 щий прохождение (Е+1) - го входного импульса CUBX (CDBX) через логический элемент DD 1.1 (DD 1.2) на вход CU 2 (CD 2) ИМС2. Где Е1 ёмкость счётчика ИМС1. Вследствие этого по фронту указанного импульса происходит увеличение (уменьшение) на 1 числа N 2, записанного в ИМС2, и обнуление счётчика ИМС1 (N1 = 0). После этого на выходах Аналогично описанному выше взаимодействуют в режиме счёта ИМС2 и ИМСз,... ИMCn-i и ИМСN. При полном заполнении каскадного счётчика в режиме суммирования, то есть, когда N 1 = Е1, N 2 = Е2,..., NN = EN, фронт следующего счётного сигнала CUBX поступает синхронно на входы CU 1, CU 2,..., CUN и вызывает обнуление всех ИМС данного счётчика. В режиме вычитания при N1= 0, N2 =0, …, NN =0 фронт счётного сигнала CDBX синхронно воздействует на входы CD 1, CD 2,..., CDN и переводит все ИМС каскадного счётчика в режим записи максимального числа: N1 = Е1, N2 = Е2, …, NN=EN. Из представленных выше материалов следует, что для синхронного каскадного счётчика с параллельным переносом время задержки распространения сигналов Тзд может быть определенно из соотношения Тзд. = Тзд. j + Тл (10.24) где T зд. j - время задержки распространения сигналов j - ой ИМС от тактового входа CU (CD) к выходу переноса Сравнение соотношений (10.24) и (10.21) показывает, что при применении для построения анализируемых схем идентичных ИМС каскадные счётчики с параллельными переносом имеют более высокое быстродействие, чем счётчики с последовательным переносом. 33 Интегральные микросхемы счётчиков рис. 10.10 и рис. 10.11 имеют входы указанные ИМС могут начинать счёт не только с нуля, но и с любого числа Nx и с любого состояния. Для этого достаточно предварительно загрузить это число Nx = { Dp... D 1, D 0,} в счётчик. Тогда обнуление счётчика (N 1 =0, N 2 = 0,..., NN =0), при котором формируется сигнал прямого переноса nj = Ej - Nx (10.25) В режиме обратного счёта сигнал переноса (займа) счётчик ИМСj числа Nx сигнал переноса nj = Nx + l (10.26) Предварительная установка счётчика в заданное состояние широко используется в делителях частоты для регулирования их коэффициента деления. 10.6.2. Каскадные счётчики на основе ИМС реверсивных счётчиков второго типа Алгоритм функционирования одиночной интегральной микросхемы реверсивного счётчика второго типа описывается полученной ранее системой уравнения (10.13). Вместе с тем, для описания функционирования указанной ИМС в каскадном счётчике системы уравнений (10.13) оказывается недостаточно. В дополнение к ней должна быть введена система уравнений, описывающая процесс формирования сигналов ИМС на выходе переноса MAXI / MIN и на выходе наращивания счёта Система уравнений, описывающая формирование сигналов переноса MAXI / MIN в ИМС реверсивных счётчиков второго типа, имеет следующий вид: 34

где Х=(1 или 0); Формирование сигналов на выходе наращивания счёта

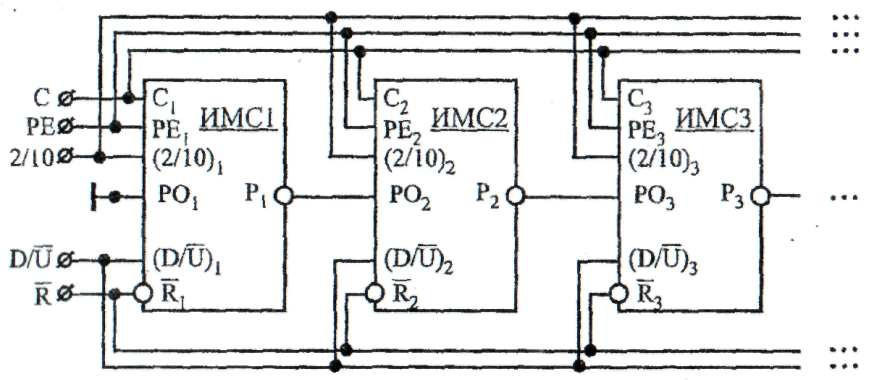

35 Типичным примером ИМС реверсивных двоичных счётчиков второго типа является 4- разрядные интегральные ТТЛШ микросхемы типа К555ИЕ13, КЕ555ИЕ13-4, КР1533ИЕ13, ЭКФ1533ИЕ13 и другие (рис.10.8.в). Соотношения (10.27), (10.28) описывают работу их выходов переноса MAX / MIN и наращивания счёта Таблица 10.6 Наличие в данных ИМС выхода переноса MAX / MIN, выхода наращивания счёта • Счёт реализуется по положительному фронту тактового импульса CLK при "нулевом" уровне напряжения на входе разрешения счёта • Напряжение "единичного" уровня на выходе переноса MAX / MIN устанавливается при достижении счёта 15 (1111)2для прямого счёта и "ноль" (0000)2 для обратного • Установка "нулевого" уровня напряжения на выходе наращивания счёта 36 состояние Nj (t) = 0 в состояние Nj (t + 1) = 15 в режиме обратного счёта. Одной из разновидностей реверсивных счётчиков второго типа являются счётчики у которых отсутствует, вход разрешения счёта Из рис. 10.12 видно, что для построения каскадного счётчика на основе ИМС рассматриваемого типа необходимо выход переноса Pj -1 каждой ИМС предыдущего каскада соединить со входом переноса POj ИМС следующего каскада, а управляющие входы D /

и 2/10 - соединить в параллель, образуя, таким образом, общие для всех ИМС каскадного счётчика шины управления направлением счёта, предустановки и др. Рис. 10.12 Интегральные микросхемы типа К1561ИЕ11 и К561ИЕ14 ЭКФ561ИЕ14) относятся к описанной выше разновидности ИМС реверсивных счётчиков второго типа. Первая из указанных ИМС представляет собой четырёхразрядный двоичный реверсивный счётчик, а вторая - 4-разрядный двоичный/двоично-десятичный реверсивный 37 счетчик. Их таблицы рабочих режимов представлены в таблицах 10.7 и 10.8 соответственно. Таблица 10.7

Таблица 10.8

38

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2021-04-05; просмотров: 529; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.21.244.172 (0.106 с.) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

стробирования (разрешения) параллельной загрузки - отрицательный импульс напряжения.

стробирования (разрешения) параллельной загрузки - отрицательный импульс напряжения.

. выбора направления счета, вход разрешения счета

. выбора направления счета, вход разрешения счета  , вход тактирования CLC и вход стробирования предварительной записи

, вход тактирования CLC и вход стробирования предварительной записи  . Управление работой счетчиков данной разновидности осуществляется подачей сигналов на указанные входы управления в соответствии со следующей системой уравнений:

. Управление работой счетчиков данной разновидности осуществляется подачей сигналов на указанные входы управления в соответствии со следующей системой уравнений:

и

и .

.

всех ИМС счётчика для успешной реализации управления режимом предуставки каскадного счётчика в заданное состояние.

всех ИМС счётчика для успешной реализации управления режимом предуставки каскадного счётчика в заданное состояние.

подают на тактовые входы CU (CD) всех ИМС, кроме ИМС1, через логические элементы ИЛИ совметнос входными счётными сигналами CUBX (CDBX). При этом формирование сигналов на счётных входах j - ой ИМС осуществляется в соответствии со следующими логическими соотношениями:

подают на тактовые входы CU (CD) всех ИМС, кроме ИМС1, через логические элементы ИЛИ совметнос входными счётными сигналами CUBX (CDBX). При этом формирование сигналов на счётных входах j - ой ИМС осуществляется в соответствии со следующими логическими соотношениями: j -1 +С U вх (10.22)

j -1 +С U вх (10.22) j -1 +С D вх (10.23)

j -1 +С D вх (10.23) {2,3,…, N }.

{2,3,…, N }. .

.

- переход из “1” в “0” на выходе MAX/MIN по фронту нарастания сигнала на входе CLK;

- переход из “1” в “0” на выходе MAX/MIN по фронту нарастания сигнала на входе CLK;

и тактового входа CLK обеспечивает возможность их каскадного включения. Действительно, в рассматриваемых интегральных микросхемах имеем:

и тактового входа CLK обеспечивает возможность их каскадного включения. Действительно, в рассматриваемых интегральных микросхемах имеем: , вход разрешения установки РЕ, вход переноса РО, тактовый вход С, вход установки нуля R, информационные D - входы параллельной загрузки числа, информационные Q - выходы результатов счёта и выход переноса Р. В том случае, когда ИМС счётчика представляет собой двоичный/двоично-десятичный реверсивный счётчик к указанной группе входов добавляется вход 2/10 переключения счётчика из двоичного режима работы в двоично-десятичный и наоборот. Каскадирование ИМС счётчиков данной разновидности иллюстрирует рис. 10.12.

, вход разрешения установки РЕ, вход переноса РО, тактовый вход С, вход установки нуля R, информационные D - входы параллельной загрузки числа, информационные Q - выходы результатов счёта и выход переноса Р. В том случае, когда ИМС счётчика представляет собой двоичный/двоично-десятичный реверсивный счётчик к указанной группе входов добавляется вход 2/10 переключения счётчика из двоичного режима работы в двоично-десятичный и наоборот. Каскадирование ИМС счётчиков данной разновидности иллюстрирует рис. 10.12.

/U

/U