Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Оцінка верхньої фінітної частоти вхідного аналогово сигналуСодержание книги

Поиск на нашем сайте

Для визначення верхньої фінітної частоти, тобто значення максимальної частоти, що може міститися в аналоговому вхідному сигналі, необхідно порахувати максимальну кількість тактів при виконані обміну і обробки інформації.

Таблиця 9. Кількість тактів, що виконуються основним циклом програми

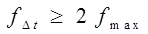

Кількість тактів в циклі очікування головної програми розраховується у відповідності з tпер АЦП. Отже загальна кількість тактів основного циклу програми: N= 2570. На основі теореми про вибірки (дискретизації) визначимо фінітну частоту роботи МПП. Дана теорема в ряді випадків називається теоремою Котельникова, Шеннона або Уіттекера – на честь вчених, що її сформували і довели незалежно один від одного. Теорема стверджує можливість представлення аналогово сигналу дискретним рядом, отриманим з АЦП, у випадку виконання умови:

де fDt – частота дискретизації; fmax – фінітна частота вхідного аналогово сигналу. При тактовій частоті роботи МП КР580ВМ80 рівній 2,5 МГц отримаємо тривалість виконання основного циклу програми:

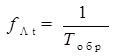

що відповідає частоті обміну і обробки інформації в МПП, яка рівна:

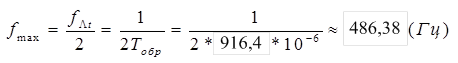

За теоремою про вибірки фінітна частота вхідного аналогово сигналу має бути вдвічі менша fDt, тобто

Отже, МПП ефективно з великою достовірністю проводить перетворення за функціональною залежністю аналогових сигналів з верхньою обмежувальною частотою 486,38Гц. Опис функціонального вузла

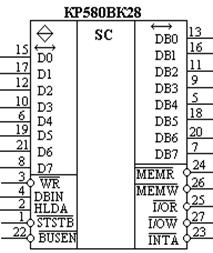

Системний контролер КР580ВК28 призначений для фіксації слова стану процесора КР580МВ80А, формування сигналів які керують пам’ятю і зовнішніми пристроями і буферизації шини даних.

Таблиця 10. Технічні характеристики

На схемі 15 зображено корпус системного контролера, а на умовне графічне зображення схеми електричної принципової. Функціональне призначення виводів контролера приведено в таблиці.

Схема 15.Схематичне зображення корпусуКР580ВК28.

До складу системного контролера входять: регістр стану; декодуюча схема шинний формувач. В кінці першого такту кожного машинного циклу генератор КР580ГФ24 видає на вхід STSTB системного контролера строб відємної полярності. По цьому імпульсу виконується фіксація слова стану мікропроцесора в регістрі стану системного контролера, які потім дешифруються з допомогою декодуючої схеми, і на відповідному керуючому виході (MEMR, MEMW, I/OR, I/OW) появляється сигнал, призначений для керування пам’яттю або зовнішніми пристроями. Вхід BUSEN використовується для керування виходами DB0-DB7, які приєднуються до системної шини. Якщо на цей вхід подати сигнал високого рівня, то виводи DB0-DB7 переходять у високоімпендансний стан, цим самим дозволяючи другим пристроям обінюватись даними через шину даних. Якщо до входу INTA підключити через опір 1кОм джерело живлення +12В, то системний контролер виставить на шину даних код команди RST7. Якщо у відповідь на підтверджуючий сигнал низького рівня системного контролера INTA зовнішні пристрої видадуть на системну шину перший байт команди CALL (1101101), то системний контролер видасть ще два сигнали INTA для того щоб прочитати останні два байти команди CALL. Схема підключення системного контролера до мікропроцесора КР580МВ80А зображена на схемі в додатку.

Таблиця 11.Функціональне ризначення.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2020-03-02; просмотров: 217; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.102 (0.006 с.) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||