Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Синтез аналогової схеми фільтруСтр 1 из 6Следующая ⇒

Завдання на курсову роботу

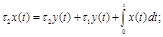

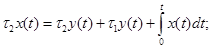

Тема курсової роботи: “Мікропроцесорна обробка аналогової інформації”. Постановка задачі: Розробити компоненти технічного і програмного забезпечення мікропроцесорного пристрою на базі МП КР580ВМ80, який включає аналогово-цифровий і цифро-аналоговий перетворювачі і виконує функцію цифрової обробки аналогової інформації. Обробка описується заданим пропорційно-інтегро-диференціальним рівнянням, що пов’язує аналогові сигнали x(t) на вході і y(t) на виході системи. Термін здачі курсової роботи: 29.12.2004 року. Початкові дані: Функціональна залежність: Розрядність АЦП і ЦАП: 12; Полярність вхідного сигналу: двополярний; Організація обміну з АЦП: через переривання RST 5; використати 1-й режим роботи КР580ВВ55; Об’єм ОЗП: 8Кб; організація мікросхеми пам’яті: 2048x8; Вид функціонального вузла: системний контролер з використанням КР580ВК28. Анотація

“Пристрій мікропроцесорної обробки аналогової інформації”. Курсова робота. – НУ ”Львівська політехніка”, каф.: САПР, дисципліна: “Комп’ютери і мікропроцесорні системи”, 2004. Курсова робота складається з 35 сторінок, 11 таблиць, 16 схем, 1 додатку. В даній роботі розроблено компоненти апаратного і програмного забезпечення мікропроцесорного пристрою, який включає аналого - і цифро-аналогові перетворювачі і виконує обробку за функціональною залежністю Виконання курсової роботи має за мету: поглиблення теоретичних знань, технічних і програмних засобів мікропроцесорних пристроїв; розвиток навиків самостійної розробки загальної структури МПП з аналогово-цифровим і цифро-аналоговим перетворенням інформації, побудови принципових схем окремих вузлів принципів, розробки та відлагодження програмного забезпечення на мові асемблеру мікропроцесора КР580ВМ80; набуття навиків роботи з технічною та довідниковою літературою з питань реалізації ряду вузлів МПП, вибору аналого-цифрового і цифро-аналогово перетворювачів (АЦП і ЦАП), використання стандартних підпрограм з прикладного програмного забезпечення МП КР580ВМ80.

Зміст

Перелік умовних скорочень Вступ 1. Синтез аналогової схеми фільтру 2. Синтез структурної схеми цифрового фільтру 3. Вибір і обґрунтування типу АЦП і ЦАП 3.1 Вибір типу АЦП 3.2 Вибір типу ЦАП 3.3 Структура представлення даних 4. Структурна схема та алгоритм функціонування МПП 4.1 Опис структурної схеми МПП 4.2 Розподіл адресного простору 4.3 Алгоритм функціонування МПП 5.Загальна структура програми роботи МПП 5.1 Опис програм вводу, виводу 5.2 Опис програми обробки інформації 5.3 Оцінка верхньої фінітної частоти вхідного аналогового сигналу 6. Опис функціонального вузла Аналіз результатів та висновки Список використаної літератури Додаток 1 Перелік умовних скорочень

Вступ

Сучасний рівень автоматизації в промисловості значною мірою забезпечується застосуванням систем програмного керування на базі мікропроцесорних обчислювальних пристроїв. Тому спеціалісти, які експлуатують та проектують системи автоматичного керування, повинні володіти відповідними знаннями не тільки для програмування мікропроцесорних обчислювальних пристроїв, але й для побудови та функціонування мікропроцесорних систем, мати навики роботи з ними для використання під час проектування та експлуатації систем програмного керування найрізноманітнішими пристроями та механізмами. Адже сфери використання мікропроцесорних пристроїв та систем надзвичайно різноманітні. Це універсальні обчислювальні пристрої – комп’ютери та калькулятори, а поза тим – системи керування електроприводами промислових механізмів та установок, робототехніка, системи контролю та сигналізація, електропобутова техніка, електричні системи і комплекси транспортних засобів тощо.

Електроніка як галузь техніки розвивається виключно швидкими темпами. Вона пройшла шлях від громіздких ламп до компактних транзисторів які з часом майже повністю замінили великі інтегральні схеми з густиною розміщення компонентів до десятків мільйонів транзисторів на одному кристалі. Зараз відбувається глобальні інтеграція електронних пристроїв: наприклад ядро мікропроцесора Pentium II з частотою 400 MHz запросто поміщається на монеті в 25 копійок, а сам персональний комп’ютер на його основі без проблем поміщається на письмовий стіл, тоді як років 10 назад набагато менш потужні системи займали величезні приміщення і коштували купу грошей; мобільний телефон, процесор якого по потужності наближається до всієї обчислювальної потужності Пентагону 70-х років запросто ховається в долоні. Забезпечення високого технічного рівня автоматичних систем управління, радіотехнічних комплексів, засобів зв’язку, гнучких автоматизованих виробництв можливе лише на основі оптимального розподілу функцій між цифровими та аналоговими частинами в межах конкретної системи. Тому аналогові мікросхеми поряд із цифровими мікросхемами широко застосовуються у сучасних радіоелектронних засобах для підсилення, перетворення та обробки аналогових сигналів. Одночасно з розвитком інтегральної технології методи розробки та застосування аналогових мікросхем стають дійовим засобом успішного розв’язання складних інженерних задач проектування радіоелектронної апаратури за умови оволодіння ними інженером-розробником. Вибір типу АЦП

Вибір типу АЦП здійснювався за такими критеріями: Кількість розрядів повинно відповідати умовам індивідуального завдання; Керування роботою здійснюватиметься з мінімальними апаратними і програмними затратами; Цифрові виходи повинні мати логічні рівні ТТЛ-логіки, тобто допускається пряме підключення до каналів вводу-виводу; Відповідність полярності вхідного сигналу до завдання. Проаналізувавши запропоновані мікросхем ЦАП, зокрема К572ПВ1 (КР572ПВ1) і К1108ПВ2, я дійшов висновку що найкраще вище перерахованим критеріям відповідає ВІС АЦП К572ПВ1. Дамо коротку характеристику цій мікросхемі. Напівпровідникова ВІС 12-ти розрядного АЦП, типу К572ПВ1 (А, Б, В) є універсальним багатофункціональним вузлом для пристроїв вводу-виводу МП систем низької і середньої швидкодії. Разом із зовнішніми ОП, ГТІ мікросхема виконує функції АЦП послідовного наближення з виводом паралельного двійкового коду через вихідні каскади з трьома станами, а також помножуючого АЦП з паралельним і послідовним вводом інформації. Конструктивно ВІС виконана в плоскому металокерамічному герметичному корпусі типу 4134.48-2. У склад ВІС входять пристрої для організації побайтового обміну інформації з 8-розрядною шиною даних МП. В режимі АЦП існує можливість організації синхронної і циклічної роботи, довільного зменшення числа розрядів і виводу даних в послідовному коді.

Основні електричні параметри мікросхеми при температурі довколишнього середовища 25 ± 10 0С Не менше Не більше Нелінійність dL, %: К572ПВ1А -0,05 0,05 К572ПВ1Б -0,1 0,1 К572ПВ1В -0,2 0,2 Диференційна не лінійність dLD, %: К572ПВ1А -0,1 0,1 К572ПВ1Б -0,2 0,2 К572ПВ1В -0,4 0,4 Вихідна напруга низького рівня U0L, B: –– 0.3 Вихідна напруга високого рівня U0H, B: 2,4 –– Струм споживання ІСС1, мА: –– 3 Струм споживання ІСС2, мА: 5 –– Типове значення вихідного струму при UREF = 10 В становить 50 мА. Вхідний струм управління не перевищує 1 мкА. Нормальне функціонування ВІС забезпечується при тактовій частоті до 250 кГц. Кількість виводів мікросхеми становить 48. Їх нумерація і призначення наведені у таблиці 1.

Таблиця 1.Призначення виводів ВІС К572ПВ1

Мікросхема працює від двох джерел живлення UCC1 = (5 ¸15) В ± 5 % і UCC2 = 15 В ± 5 %. При узгоджені мікросхеми з ТТЛ схемами, напругу живлення UCC1 установлюють 5 В± 5%, а при узгоджені з КМОП схемами – 15 В ± 5 %. При любій UCC2 напруга високого рівня на вході порівняння не повинна бути менша за 10 В. Гранично допустимі і граничні значення електричних режимів експлуатації: Гранично допустимі Граничні Не менше Не більше Не менше Не більше

Зразкова напруга UREF, В: -10,29 10,29 -15 15 Вхідна напруга високого рівня UIH, В: -2,4 5,25 2,4 17 Вхідна напруга низького рівня UIL, В: 0 0,4 0 0,4 Вихідний струм високого рівня I0H, мА: –– 0,04 –– 0,04 Вхідний струм низького рівня I0L, мА: –– 0,4 –– 0,4 Робота ВІС в режимі АЦП проходить у відповідності з добре відомим принципом послідовного наближення з програмованим зсувом. Часова діаграма АЦП наведена на схемі 4. Перетворення здійснюється за 12 робочих тактів, кожен з яких за тривалістю рівний двом імпульсам ГТІ. Допоміжний такт використовується для формування сигналу “кінець перетворення”. По цьому сигналу відбувається зчитування цифрової інформації.

Схема 4. Часова діаграма роботи ВІС К572ПВ1 в режимі АЦП.

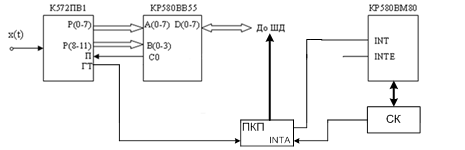

В циклічному режимі роботи за періодом зчитування йде період повернення АЦП в початковий стан (скидання) по сигналу з виводу 22 (Цикл). Включення резисторів R/2 або 2R на вході компаратора А1 (див. Додаток 2) забезпечує зміну UIRN від 0,5 до 2 UREF відповідно. Типовий час перетворення складає 110 мкс. Полярність діапазону вхідної напруги може бути любою і встановлюється вибором полярності UREF. Число розрядів перетворення може бути зменшено шляхом подачі на вхід 27 повторного сигналу “Запуск” по закінченню (n+1) такту. З’єднання виводів 22 і 28 переводить схему з синхронного режиму роботи в циклічний, при цьому на вхід 27 подається логічний 0. Особливістю конструктивного-технологічного виконання ВІС АЦП К572ПВ1 дає можливість її сумісній роботі із серійними МП комплексами без застосування додаткових зовнішніх пристроїв. Для спряження АЦП з МП доцільно використовувати програмований паралельний інтерфейс (ППІ) КР580ВВ55. У даній роботі використовується 1-й режим роботи ППІ. На схемі 4 наведено фрагмент схеми підключення ВІС АЦП К572ПВ1 до шин МПП через КР580ВВ55 в режимі вводу інформації через ПКП.

Схема 4. Фрагмент схеми підключення ВІС АЦП К572ПВ1 до шин МПП.

На аналоговий вхід АЦП подається сигнал х(t). Цифрові виходи P(0-7) АЦП (молодші 8 біт) підключені до каналу А ППІ, а цифрові виходи P(8-11) АЦП (старші 4 біти) – до молодшої тетради каналу В ППІ. Вивід АЦП П (пуск) підключений до розряду 0 порта С. Цей сигнал кожен раз буде формуватись програмно. Обмін між ППІ і МП здійснюється через виводи D(0-7), які підключені до шини даних. Канал А та В ППІ запрограмовані на ввід, розряди каналу С використовуються для керування обміном. Запуск АЦП (сигнал П), здійснюється через паралельний інтерфейс КР580ВВ55 (розряд 0 каналу С).При поступлені на АЦП x(t) і при закінченні перетворення він виробляє сигнал готовності ГТ, який підключений до ПКП.Який в свою чергу подає сигнал INT на МП, і дочекавшись сигналу INTA від СК подає на шину даних код команди CALL і діставши іще два сигнали INTA подає на шину даних два байти адреси підпрограми обробника переривання. По такомуж алгоритму і буде підключена ВІС до нашого Програмованого Контроллера Переривань.

Вибір типу ЦАП

Вибір типу ЦАП здійснювався з урахуванням наступних вимог: Кількість розрядів ЦАП співпадає із АЦП і відповідає умовам індивідуального завдання; Цифрові входи мають логічні рівні ТТЛ - логіки, тобто допускають пряме підключення до каналів вводу-виводу; Відповідність полярності вихідного сигналу до завдання і схем вибору ЦАП. Проаналізувавши такі мікросхеми ЦАП, як К572ПА2 (КР572ПА2), К594ПА1, К1108ПА1, я зупинився на виборі мікросхеми К594ПА1. Мікросхема типу К594ПА1 являє собою паралельний ЦАП з сумуванням струмів, комбінованою матрицею (зважених і R-2R резисторів), використовується для перетворення двійкового 12 розрядного коду в струм та працює зі стандартними рівнями сигналів від ТТЛ та КМОН ЦІС. Конструктивно ЦАП створений на двох кристалах, які знаходяться в металокерамічному корпусі. Мікросхема створена по біполярній планарно-епітаксіальній технології з p-n-p та n-p-n транзисторами. Основні електричні параметри при температурі навколишнього середовища 25±10 оС: Не менше Не більше Число розрядів......12 Диференціальна нелінійність δ(%)..............-0,012 0,012 Діапазон вихідних струмів Iorn (мА): Уніполярний............................................1,8 2,2 Біполярний....................................................0,9 1,1 Струм витоку (утєчкі) на виході (мкА)........... 0,7 Вхідна напруга низького рівня (В), про роботі з: ТТЛ........................ 0,8 КМОН..................................................……. 0,3 Вхідна напруга високого рівня (В), про роботі з: ТТЛ...................................................................…….................... 2,0 КМОН......................................................................……............. 0,7Ucc1 Струм живлення Icc1(мА)................................................ 25 Струм живлення Icc2(мА).............................................…….. 35 Вихідний струм Io(мА)...........................................................…….. 2,2 Час встановлення вихідного струму (при зміні коду від 00...00 до 11...11) (мкс)............................ 3,5 Гранично допустимі значення електричних режимів експлуатації: Не менше Не більше Напруга джерела живлення Ucc1(В)................................................. 6,0 Напруга джерела живлення Ucc2(В).................................................-18 Напруга опорного джерела Uref(В)...................................9,0 11,0 Вхідна напруга високого рівня (В)......................................2,0 6,0 Вхідна напруга низького рівня (В)...................................0 1,0 Типові залежності електричних параметрів ЦАП від зміни напруги джерел живлення та температури навколишнього середовища:

Схема 6. Типові залежності нелінійності та диференціальної не лінійності ІС ЦАП К594ПА1 від напруг джерел живлення

а) б) Схема 7. Типові залежності не лінійності (а) і часу встановлення (б) ІС ЦАП К594ПА1 від температури навколишнього середовища

Схема 8. Типова залежність часу встановлення ЦАП К594ПА1 від ємності навантаження С

Мікросхема К594ПА1 експлуатується без додаткового тепло відводу. При температурі навколишнього середовища 85 С та більше поверхню ІС необхідно охолоджувати повітрям зі швидкістю 3 м/с. Забороняється подавати які-небудь електричні сигнали на поверхню кришки корпусу і незадіяні виводу ІС. Резистор 10 кОм (виводи 1,2) забезпечує режим роботи з біполярним струмом в діапазонах напруги ±2,5; ±5; ±10В. Номінальні значення ємності навантаження ІС 10 пФ. Загальна ємність навантаження може перевищувати номінальне значення, але при цьому норми на часові параметри ЦАП не гарантуються. В режимі роботи ЦАП з струмовим виходом допускається підключення джерела опорного навантаження до виводу 22 ІС. При цьому величина вихідного струму перетворювача буде залежати від стабільності підключеного резистору.

Таблиця 2. Нумерація та призначення виводів ІС ЦАП К594ПА1

Мікросхема К594ПА1 забезпечує норми на електричні параметри, при номінальному значенні Uref=10,24B з допустимими відхиленнями ± 3% і стабільності підтримки напруги 0,005%. Амплітудні значення пульсацій джерела опорної напруги можуть досягати 150 мкВ, але значення напруг перехідних і паразитних сигналів не повинні перевищувати 200 мкВ при тривалій дії не більше 0,3 мкс.

Схема 9. Структурна схема підключення МП і ЦАП Опис структурної схеми МПП

Структурна схема МПП включає крім АЦП і ЦАП всі необхідні для функціонування компоненти МПС: МП КР580ВМ80, тактовий генератор КР580ГФ24, системний контролер КР580ВК28, оперативну та постійну пам’ять (ОЗП, ПЗП), два програмованих паралельних інтерфейси КР580ВВ55, до яких підключаються АЦП і ЦАП.

Схема 10. Структурна схема МПП

Позначення елементів на схемі 11: СК – системний контролер; ША – шина адрес (16-ти розрядна); ШД– шина даних (8-ми розрядна); ШК – шина керування; ВШД – внутрішня шина даних мікропроцесора (8-ми розрядна); ВШК – внутрішня шина керування мікропроцесора; ДШП – дешифратор пам’яті; ДШВ/В – дешифратор каналів вводу-виводу; x(t) – вхідний аналоговий сигнал; y(t) – вихідний аналоговий сигнал. У таблиці 5 наведено елементи, які використовуються в структурній схемі МПП, їх опис, та мікросхеми, що їм відповідають.

Таблиця 5. Опис та мікросхеми елементів структурної схеми МПП

Наведемо коротко призначення кожного з елементів структурної схеми МПП. МП. Головна частина МПП. Виконує функції зчитування інформації із зовнішніх пристроїв чи пам’яті і виконання над нею арифметичних чи логічних операції; аналізу результатів обчислення; запису даних у пам’ять чи зовнішні пристрої; ГТІ. Використовується для вироблення тактуючих синхросерій F1, F2 для мікропроцесора; сигналу початкової установки RESET; сигналу готовності READY; сигналу стробу стану STB, який поступає на системний контролер і служить для фіксації слова стану мікропроцесора; СК. Призначений для фіксації слова стану мікропроцесора, сигналів керування зовнішньою пам’яттю та пристроями вводу-виводу, буферизації шини даних; ПЗП. Використовується для зберігання та зчитування інформації. Відмінність від ОЗП полягає у тому, що в ПЗП інформація записується один раз і режимі експлуатації використовується лише при зчитуванні; ОЗП. Призначений для зберігання, зчитування та запису інформації. В режимі експлуатації інформацію можна як зчитувати, так і записувати; ППІ. Використовується для організації вводу-виводу паралельної інформації різних форматів і дозволяє здійснювати обмін в більшості відомих протоколах паралельної передачі даних; АЦП. Призначений для перетворення аналогово сигналу у цифровий код відповідної розрядності; АЦП. Призначений для перетворення цифрової комбінації певної розрядності у аналоговий сигнал; ПКП призначений для контролю за перериваннями, та при поступленні запиту на переривання подачу адреси підпрограми обробки переривання. ША, ШД, ШД. Використовуються для інформаційного обміну між елементами МПП; ВШД, ВШК. Використовуються для інформаційного обміну в самому МП; ДШП, ДШВ/В,ДАК. Використовуються для вибору відповідних мікросхем пам’яті та зовнішніх пристроїв. Таймер. Використовується як подільник частоти для ТІ АЦП.

Розподіл адресного простору

В адресний простір МП КР580ВМ80 входить 64К адрес пам’яті (216 ), що визначається 16-ти розрядною адресною шиною. МП КР580ВМ80 може здійснювати синхронний і асинхронний обмін інформацією за даними адресами з пам’яттю (ПЗП, ОЗП) та зовнішніми пристроями. При обробці інформації МП зчитує коди команд, операнди і записує одержаний вміст в РЗК або виконує обмін інформації з пам’яттю та зовнішніми пристроями. Можливі два підходи до організації звертання до пристроїв обміну інформації. Перший підхід використовує звертання до зовнішніх пристроїв, як до комірок пам’яті. До переваг даного підходу можна віднести можливість використання різноманітних команд пересилання даних. Інший підхід використовує роздільне керування пам’яттю і зовнішніми пристроями. Лиш тільки дві команди IN і OUT, в цьому випадку, призначені для обміну інформації з зовнішніми пристроями. Так, як для цих команд адрес для зовнішнього пристрою 8-ми розрядний, то МП КР580ВМ80 може звертатись до 256 пристроїв вводу і 256 пристроїв виводу. При цьому адресний простір пам’яті буде максимальним. Організація адресного простору пам’яті наступна:

Таблиця 6.

Розподіл адресного простору для зовнішніх пристроїв: 1.Для програмованого контролера переривань.

Таблиця 7.

2.Для програмованих паралельних інтерфейсів

Таблиця 8.

3. Для програмованого таймера Таблиця 9.

У схемі 12 приведені адреси, що відводяться для програм, підпрограм, даних.

Схема 12. Розподіл простору адрес в МПП обробки аналогово сигналу

Алгоритм функціонування МПП

Схема 13. Алгоритм функціонування МПП На цьому етапі відбудеться переривання, обробник якого встановить змінну Ind в1 При одночасному включені живлення –5В, +5В,12В і поступленні тактових імпульсів на мікропроцесор, всі регістри і прапорці МП встановлюються в довільні стани. Після цього подається з ГТІ на вхід RESET МП сигнал високого рівня тривалістю не менше 3 такітв. Лічильник команд (PC), тригер дозволу переривання (вихід INTE), а також тригер підтвердження захоплення (вихід HLDA) скидаються, і мікропроцесор починає вибірку з пам’яті команд, розміщених з нульової адреси. Алгоритм головної програми включає наступні пункти. Ініціалізація зовнішніх пристроїв, запис коефіцієнтів a0, a1, a2 і початкове обнулення змінних. ППІ, до якого підключений АЦП програмується на режим роботи 0, порт А і порт В – на ввід. ППІ, до якого підключений ЦАП також програмується на 0-й режим роботи, однак порти А і В працюють на вивід. У програмованому таймері лічильник 0 ініціюється як двійковий, на 2-й режим роботи (подільник частоти) і в цей лічильник записується значення 8 (частота сигналу F2(TTL) ділиться на 8). Обнулення змінних (xn-1, xn-2,) виконується у зв’язку з тим, що вони використовуються як множники у рівнянні цифрового фільтру, однак при першому звертання до цього рівняння ще не сформовані (отже повинні бути нульовими). Подання на АЦП сигналу “Запуск”. Затримка, пов’язана із перевіркою змінної Ind на рівність 1, використовується у зв’язку з тим, що подавши на АЦП сигнал “Запуск” останній не одразу виробить двійковий код вхідного аналогово сигналу (для ВІС АЦП К512ПВ1 tпер=110мкс.), тобто мікропроцесору потрібно почекати доки АЦП не видасть сигналу “готовність”, тим самим викликавши переривання. Обробник цього переривання прочитає дані з АЦП, запише їх в пам’ять і встановить зміну Ind в 1, що після повернення до головної програми призведе до виходу із циклу очікування і виконанню наступних дій. Обробка отриманої інформації і вивід її на ЦАП. Обробка включає перемноження і сумування елементів у відповідності до рівняння цифрового фільтру, тобто знаходження кінцевої вихідної величини yn, яка і виводиться на ЦАП. Після цього здійснюється перехід до пункту 2. Для збільшення фінітної частоти вхідного сигналу запуск АЦП проводиться перед підпрограмою виводу (а не безпосередньо перед циклом очікування), тобто в розрахований час МП АЦП працюють паралельно. Функціонування МПП припиняється після вимкнення живлення. Блок-схема програми обробки переривання приведена на схемі 14. Під час виконання команд обробника всі переривання заборонено. Пісня збереження в стеку регістрів, які будуть використовуватись, скидається сигнал “Запуск” АЦП, і відбувається читання портів ППІ. Прочитана інформація записується в пам’ять. Наступними діями є встановлення в 1 змінної Ind, відновлення зі стеку регістрів, дозвіл переривань і повернення до перерваної програми.

Схема 13. Алгоритм програми обробки переривання за адресою 00E4h(IR1) Виконавши команду, мікропроцесор збереже у стеку адресу (тобто поточне значення лічильника команд PC) перерваної програми і почне вибирати з пам’яті команди, які розташовані за адресою 00E4h. Перша команда – це безумовний перехід на програму обробки переривання. Таким чином реалізовується механізм обміну даних з АЦП через переривання. Отже нам задано адресу 00E4h, це значить,що старший байт це ICW2 = 00h, а молодший байт формується на основі ICW1.Отже E4h = 11100100b, а це означає що спосіб формування молодшого байта буде першим, тобто другий біт ICW1,буде 1.Так як ПКП один, то третій біт ICW1 буде 1.Так як молодший байт адреси підпрограми обробника переривання формується першим способом то його структура буде така: XXXYYY00, де ХХХ – задається старші три біта молодшого байта адреси (у нашому випадку – 111), а YYY – номер порта на який поступив запит (у нашому випадку 001b=1) Тобто сигнал готовності АЦП має бути підклбючений до IR1, а ICW1 = F6h (порожні біти ICW1 взяли за 0).Також в цій курсовій я використав маскування входів ПКП, використавши OCW1 = F7, але це не суттєво Вивід обробленої інформації здійснюється в три етапи. На першому етапі в порт А ППІ записуються молодші 8 біт результату. Із буфера порта А ці дані одразу ж переписуються в перший з буферних регістрів. На другому етапі старші 4 біти результату (інші 4 біти рівні нулеві) записуються в порт В і відповідно у другий буферний регістр. На третьому етапі одночасною подачею сигналу низького рівня на входи “дозвіл видачі” (ЕО) обох буферних регістрів, здійснюється подача 12-ти розрядного коду на входи ЦАП. Цей сигнал подається програмно, встановленням в 0 четвертого біта (не зарезервованого) порта С. Опис програми вводу, виводу

Вводом даних займається програма обробки переривання, в задачу якої входить прочитати дані з АЦП, тобто з портів А і В ППІ1, і записати їх в оперативну пам’ять. ; Обробник переривання IR1: DI ; Інші переривання заборонені PUSH PSW; Збереження в стеку регістра прапорців і акумулятора IN 04H; Читання молодших 8 інформаційних розрядів із порта А STA 403H; їх запис в оперативну пам’ять. IN 05H; Читання старших 4-ох інформаційних розрядів із порта В STA 404H ; їх запис в оперативну пам’ять. MVI A,1; Інкрементування “індикатора” на 1, тобто вказівка головній STA 40BH ; програмі, що переривання відбулося. POP PSW; відновлення зі стеку регістра прапорців і акумулятора EI ; дозвіл переривань RET ; повернення в перервану програму Підпрограма виводу обробленої інформації на ЦАП викликається в кінці робочого циклу головної програми, і в її задачу входить почергово записати у буферні регістри інформаційні розряди результату, для того, щоб потім одночасно подати їх на ЦАП. Запис у буферні регістри здійснюється через програмований паралельний інтерфейс (ППІ2). ; Підпрограма виводу інформації на ЦАП CAP: LDA 408H ; Завантаження з пам’яті 8 молодших розрядів результату OUT 0CH; Їх вивід в порт А ППІ2 (запис в 1-й буферний регістр) LDA 409H ; Завантаження з пам’яті 4 старших розрядів результату OUT 0DH; Їх вивід в порт В ППІ2 (запис в 2-й буферний регістр) MVI A,08H; Дозвіл виводу інформації із буферних регістів на ЦАП OUT 0FH ; (встановлення 4-го біту порта С ППІ2 в 0) MVI A,09H; Заборона виводу інформації із буферних регістів на ЦАП OUT 0FH ; (встановлення 4-го біту порта С ППІ2 в 1) RET ; Повернення в головну програму

Опис функціонального вузла

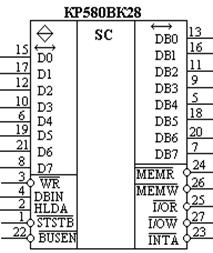

Системний контролер КР580ВК28 призначений для фіксації слова стану процесора КР580МВ80А, формування сигналів які керують пам’ятю і зовнішніми пристроями і буферизації шини даних.

Таблиця 10. Технічні характеристики

На схемі 15 зображено корпус системного контролера, а на умовне графічне зображення схеми електричної принципової. Функціональне призначення виводів контролера приведено в таблиці.

Схема 15.Схематичне зображення корпусуКР580ВК28.

До складу системного контролера входять: регістр стану; декодуюча схема шинний формувач. В кінці першого такту кожного машинного циклу генератор КР580ГФ24 видає на вхід STSTB системного контролера строб відємної полярності. По цьому імпульсу виконується фіксація слова стану мікропроцесора в регістрі стану системного контролера, які потім дешифруються з допомогою декодуючої схеми, і на відповідному керуючому виході (MEMR, MEMW, I/OR, I/OW) появляється сигнал, призначений для керування пам’яттю або зовнішніми пристроями. Вхід BUSEN використовується для керування виходами DB0-DB7, які приєднуються до системної шини. Якщо на цей вхід подати сигнал високого рівня, то виводи DB0-DB7 переходять у високоімпендансний стан, цим самим дозволяючи другим пристроям обінюватись даними через шину даних. Якщо до входу INTA підключити через опір 1кОм джерело живлення +12В, то системний контролер виставить на шину даних код команди RST7. Якщо у відповідь на підтверджуючий сигнал низького рівня системного контролера INTA зовнішні пристрої видадуть на системну шину перший байт команди CALL (1101101), то системний контролер видасть ще два сигнали INTA для того щоб прочитати останні два байти команди CALL. Схема підключення системного контролера до мікропроцесора КР580МВ80А зображена на схемі в додатку.

Таблиця 11.Функціональне ризначення.

Завдання на курсову роботу

Тема курсової роботи: “Мікропроцесорна обробка аналогової інформації”.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2020-03-02; просмотров: 215; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.118.227.69 (0.158 с.) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

. Дана робота охоплює ввід і первинну обробку аналогової інформації, подальшу цифрову обробку інформації за програмою і вхідними даними, а також вивід обробленої інформації в аналоговій формі для подальшого використання.

. Дана робота охоплює ввід і первинну обробку аналогової інформації, подальшу цифрову обробку інформації за програмою і вхідними даними, а також вивід обробленої інформації в аналоговій формі для подальшого використання.