Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Линейные коды с сохранением тактовой частотыСодержание книги

Поиск на нашем сайте

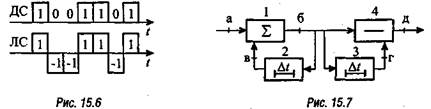

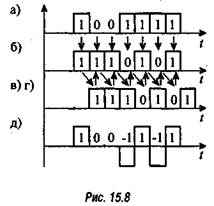

Существует несколько основных вариантов преобразования двоичного RZ или ЛТ сигнала в линейный код: 1) без изменения тактовой частоты двоичного сигнала; 2) с увеличением.тактовой частоты; 3) с уменьшением тактовой частоты линейного сигнала. Первый вариант преобразования предполагает, что частота следования отдельных символов линейного кода не изменяется и равна исходной частоте следования ft отдельных символов ДС. Здесь возможны два способа преобразования. Первый способ— с активной паузой (рис. 15.6), при котором передача нулей в исходном видеосигнале заменяется на передачу посылок отрицательной полярности. Такой ЛС называется двоично-симметричным (ДСС). Поскольку в среднем число нулей и единиц в исходном сигнале одинаково, то постоянная составляющая преобразованного сигнала равна нулю, однако за счет возможности «скопления» нулей (или единиц) постоянная составляющая начинает изменяться во времени, и межсимвольные искажения второго рода не устраняются. На практике часто применяют второй способ преобразования ДС, когда униполярный сигнал в коде RZ или NRZ преобразуется в квазитроичный код, или код ЧПИ (сигнал с чередованием полярности импульсов). При таком преобразовании «0» передается без изменения, а «1» передается так, что каждая следующая единица меняет свой знак на противоположный. Этот способ легко реализуем на практике, он устраняет межсимвольные искажения второго рода, не требуя расширения полосы пропускания в области верхних частот. Одна из возможных структурных схем преобразования двоичного сигнала в квазитроичный приведена на рис. 15.7. Осциллограммы сигналов в контрольных точках представлены на рис. 15.8. Цифровой сигнал в двоичной форме (рис. 15.8, а) поступает на сумматор по модулю 2. На другой вход сумматора поступает сигнал, прошедший через линию задержки 1 и задержанный на один тактовый интервал (рис. 15.8, в). Выходной сигнал сумматора (рис. 15.8, 6) поступает на вычитающее устройство 4. Этот же сигнал, задержанный на тактовый интервал (рис. 15.8, г), поступает на Другой вход блока 4. На выходе вычитающего устройства получаем сигнал в квазитроичном коде (рис.15.8, д).

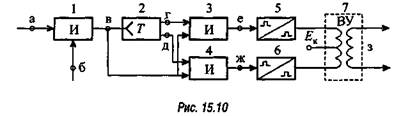

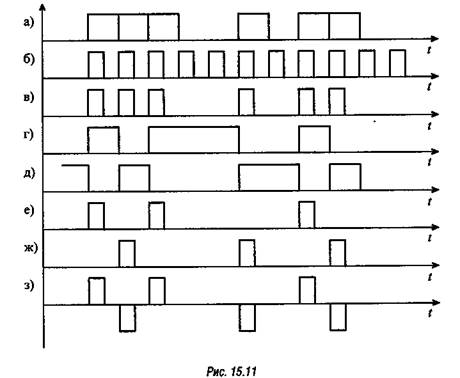

Достоинством квазитроичного кода является то, что он не имеет постоянной составляю щей и легко преобразуется в исходный двоичный код путем его пропускания через безынерционный двухполупериодный выпрямитель. Кроме того, он удобен тем, что в нем легко обнаруживаются ошибочные символы по признаку нарушения чередования полярности импульсов. Схема преобразователя квазитроичного кода, изображенного на рис. 15.7, очень сложная. На входы логической ячейки И1 поступают входной цифровой сигнал (рис. 15.11, а) и стробирующие импульсы (рис. 15.11, б). Далее сигнал (рис. 15.11, в) поступает на вход триггера. С прямого (рис. 15.11, г) и инверсного (рис. 15.11,д) выходов триггера сигналы поступают на входы логических ячеек ИЗ,И4, куда поступает также сигнал с выхода схемы совпадения И1. На выходе логических схем 3, 4 будут вырабатываться определенные импуль сы (рис. 15.11, е, ж). Формирователи импульсов 5,6 укорачивают импульсы по длительности до

Сигнал с ЧПИ обладает одним существенным недостатком — при появлении в нем длинных серий пробелов (нулей) возможен сбой системы тактовой синхронизации. Чтобы этого не происходило, следует ограничить в линейном сигнале, передаваемом в коде ЧПИ, число подряд следующих нулей. Эта задача была решена созданием кодов с высокой плотностью единиц Если в «пакете» нулей их число больше Полярности вводимых импульсов В и К выбираются так, чтобы на интервале в

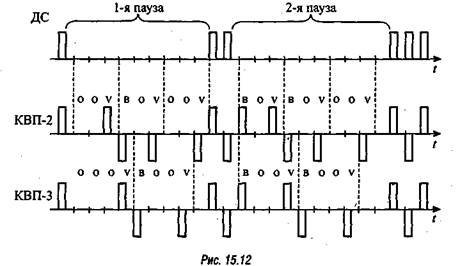

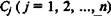

В процессе заполнения очень длинной паузы пакет из (q + 1) нулей заменяется комбинацией BOO V, если предшествующее число «пакетов» в паузе нечетное; «пакет» из (q + 1) нулей заменяется комбинацией 000 V, если предшествующее число «пакетов» в паузе четное (или нуль). Пример использования алгоритма формирования кода КВП-2 и КВП-3 приведен на рис. 15.12. Линейный сигнал в коде МЧПИ (HDB), передаваемый трехуровневым кодом с той же тактовой частотой, что и исходный двоичный сигнал, широко используется в первичных, вторичных и третичных ЦСП (ИКМ-30, ИКМ-120, ИКМ-480), работающих по металлическим кабелям (симметричным и коаксиальным). Кроме того, он применяется и как «стыковой» сигнал в оконечной аппаратуре для соединения разных иерархических структур. Возможность исключения длинных пакетов нулей или единиц обеспечивает также третий способ преобразования ДС в ЛС с сохранением тактовой частоты и числа разрешенных уровней, называемый скремблированием. При этом ДС подвергается операции перемножения с некоторой, известной заранее псевдослучайной двоичной последовательностью (ПСП): ЛС = ДС + ПСП. На приемной стороне выполняется обратная операция: ДС = ЛС + ПСП (знак + здесь и далее означает сложение по модулю 2). Для правильного восстановления исходного сигнала псевдослучайные последовательности, вырабатываемые на приемной и передающей сторонах, должны быть засинхронизированы. Для того чтобы сделать операцию дескремблирования самосинхронизирую- щейся, применяют решение, приведенное на рис. 15.13. Здесь скремблер 1 содержит сумматор по модулю 2 и формирователь псевдослучайной последовательности (ФПСП) 3. Дескремблер 4 содержит аналогичные блоки (рис. 15.13, а).

Для того чтобы сделать операцию дескремблирования самосинхро- низирующейся, т.е. не требующей формирования специального сигнала синхронизации на передающей стороне и его поиска на приемной стороне, применяют решение, приведенное на рис. 15.13. Здесь скремблер 1 содержит сумматор по модулю 2 и формирователь псевдослучайной последовательности (ФПСП) 3. Дескремблер 4 содержит аналогичные блоки (рис. 15.13, а). Формирователь двоичной ПСП включает в себя n-разрядный регистр сдвига (триггеры

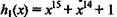

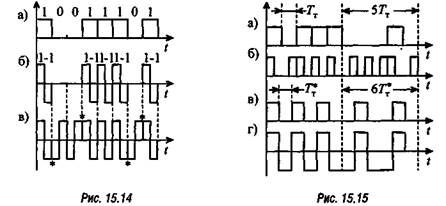

Скремблированный сигнал S представляет собой результат потактового Блочные двоичные коды Второй вариант перекодирования исходного сигнала в линейный подразумевает получение линейного кода с тактовой частотой, которая больше частоты следования отдельных импульсов исходного двоичного сигнала. Здесь также возможны два способа преобразования. Первый — преобразование ДС (рис. 15.14, а) в биимпульсный сигнал, при котором нуль передается, как и прежде, а сигнал единицы передается биимпульсным сигналом, например вида +1—1 (рис. 15.14, б). Используется также вариант, когда и нулевой символ заменяется биимпульсной комбинацией, но уже другого вида -1+1 (рис. 15.14, в). Такой метод позволяет полностью устранить постоянную составляющую в ЛС и межсимвольные искажения второго рода, но передача линейного сигнала требует увеличения полосы пропускания в области верхних частот по крайней мере в 2 раза. Кроме этого метода, возможен еще один способ преобразования, при котором каждая группа из Наиболее простыми и весьма эффективными являются линейные коды класса Например, единица исходной последовательности (рис. 15.15, а) может быть передана комбинацией 10, а нуль — 01 (рис. 15.15, б).

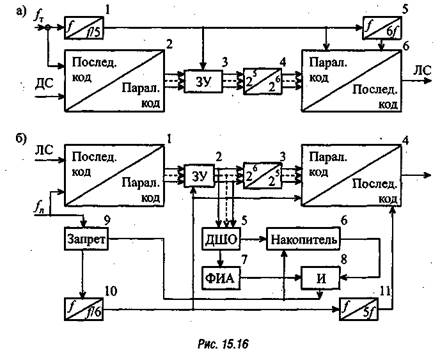

Такое кодирование всегда обеспечивает одно и то же значение постоянной составляющей ЛС при любом содержании 1 и 0 в исходном ДС, но при этом приводит к удвоению тактовой частоты линейного сигнала: В условиях ограниченной полосы линии связи при необходимости можно построить более экономные блочные коды (например, код 5В6В), когда блок из т символов исходной последовательности (см. рис 15.15, я) заменяется блоком из n = т + 1 символов линейного кода (рис. 15.15, в). При этом увеличение тактовой частоты может быть незначительным: При построении блочных кодов очень важным является выбор алфавита кода, т.е. таблицы соответствия между каждой исходной m-битовой и разрешенной m-битовой комбинациями. В частности, в коде 5В6В алфавит 6-битовых слов выбирают следующим образом. В первую очередь используют те блоки, у которых количество символов «1» равно половине общего числа бит в блоке, что обеспечивает неизменность постоянной составляющей. Таких «хороших» комбинаций будет 20 (число сочетаний из 6 по 3), и каждая из них используется для кодирования одной из 20 исходных 5-битовых комбинаций. Для остальных 5-битовых комбинаций (их число равно 12 = 25 — 20) в алфавит отбирают еще 24 шестибитовых слова (по два на каждую 5-битовую комбинацию, причем в одном слове количество символов «1» равно 4, а в другом — 2). Слова, входящие в такую пару, передаются поочередно при появлении одной и той же исходной 5-битовой комбинации. Таким образом, и для этих 12 комбинаций обеспечивается сохранение постоянной составляющей в линейном сигнале. Некоторые из возможных 6-битовых комбинаций (их число равно 20=26-20-24) не входят в алфавит и являются запрещенными. Обнаружение их в линейном сигнале свидетельствует о появлении ошибки или о нарушении синхронизации при декодировании линейного кода. Отметим, что блочное кодирование типа тВпВ оставляет линейный сигнал униполярным, однако в нем, как и при скремблировании, постоянная составляющая меняется в очень малых пределах. Это позволяет при необходимости легко устранить ее из сигнала, а затем восстановить (рис. 15.15, г). Для декодирования блочного кода на приемной стороне, когда из n -разрядной кодовой группы восстанавливается исходная m -разрядная, необходимо сначала определить границы этой группы. В большинстве случаев эту задачу удается решить 6eз использования специального сигнала синхронизации за счет обнаружения в линейном сигнале запрещенных кодовых комбинаций. Эти комбинации отсутствуют в алфавите кода и могут образовываться только на границах двух соседних групп. Например, в коде 1В2В, показанном на рис. 15.14, в, запрещенными являются комбинации вида +1+1 или -1-1 (они отмечены звездочкой). По ним и определяются границы 2-разрядных кодовых комбинаций линейного сигнала. В качестве примера рассмотрим построение преобразователей кода передачи и приема для блочного кода 5В6В. На стороне передачи исходный двоичный сигнал ДС (рис. 15.16, а) поступает в блок 2, который преобразует 5-разрядные кодовые комбинации из последовательного кода в параллельный. Делитель частоты /, который делит тактовую частоту RCfr в 5 раз, формирует импульсы блочной частоты Они совпадают по времени с последним, пятым импульсом 5-разрядной кодовой комбинации. Именно в это время и происходит запись кодовой комбинации в параллельном коде в запоминающее устройство (ЗУ) 3. Затем 5-разрядная комбинация в соответствии с выбранным алфавитом в цифровом преобразователе 4 преобразуется в 6-разрядную комбинацию и записывается в блок 6. В этом блоке с помощью тактовых импульсов линейной частоты На стороне приема (рис. 15.16, б) двоичные символы линейного сигнала, следующие с линейной частотой

Преобразование выполняется с помощью импульсов тактовой частоты ДШО 5 обнаруживает любую из 20 возможных запрещенных кодовых комбинаций, которые возникают вследствие ошибок в линейном тракте или отсутствия блочной синхронизации, т.е. неправильного разделения линейного сигнала на 6-символьные блоки. При обнаружении запрещенной комбинации ДШО 5 формирует одиночные импульсы сбоя, которые поступают параллельно в накопитель ошибок 6 и на вход формирователя интервалов анализа (ФИА) 7. Если за интервал анализа Коэффициент накопления

|

||||||

|

Последнее изменение этой страницы: 2017-02-19; просмотров: 430; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.142.198.250 (0.008 с.) |

и подают их на вычитающее устройство 7(ВУ), на выходе которого формируется полный квазитроичный сигнал (рис. 15.11, з)

и подают их на вычитающее устройство 7(ВУ), на выходе которого формируется полный квазитроичный сигнал (рис. 15.11, з)

; такой код еще называют модифицированным квазитроичным кодом (МЧПИ). Здесь

; такой код еще называют модифицированным квазитроичным кодом (МЧПИ). Здесь  — некоторое максимально допустимое число следующих подряд нулей после предыдущей единицы в исходном ДС. Обычно принимают

— некоторое максимально допустимое число следующих подряд нулей после предыдущей единицы в исходном ДС. Обычно принимают  или 3, что соответствует кодам КВП-2 и КВП-3 (или HDB-2, -3 в англоязычной терминологии). Если в реальном «пакете» нулей их число будет меньше

или 3, что соответствует кодам КВП-2 и КВП-3 (или HDB-2, -3 в англоязычной терминологии). Если в реальном «пакете» нулей их число будет меньше  , то линейное кодирование осуществляется по коду ЧПИ, т.е. нули не преобразуются, а каждая единица имеет длительность в половину тактового интервала

, то линейное кодирование осуществляется по коду ЧПИ, т.е. нули не преобразуются, а каждая единица имеет длительность в половину тактового интервала  , причем ее полярность противоположна полярности предыдущей единицы.

, причем ее полярность противоположна полярности предыдущей единицы. , то каждый пакет из

, то каждый пакет из  нулей заменяется сигналами 000 V или 500 V (для КВП-3).

нулей заменяется сигналами 000 V или 500 V (для КВП-3). тактов происходило одно нарушение правила чередования полярности. По этому нарушению на приемной стороне оконечной станции при преобразовании ЛС в ДС принимают решение об истинном содержании пакета. При выборе конкретного вида сигнала (000 V или В00 V) исходят из следующих условий: полярность импульса В всегда противоположна полярности предшествующего импульса; если между двумя соседними паузами в двоичном сигнале, имеющими число нулей больше, чем q+1 = 3 + 1=4, насчитывается четное число единиц, то заполнение второй паузы начинается с сигнала В00 V; если число единиц между двумя вышеупомянутыми паузами нечетное, то заполнение второй паузы начинается с сигнала 000V.

тактов происходило одно нарушение правила чередования полярности. По этому нарушению на приемной стороне оконечной станции при преобразовании ЛС в ДС принимают решение об истинном содержании пакета. При выборе конкретного вида сигнала (000 V или В00 V) исходят из следующих условий: полярность импульса В всегда противоположна полярности предшествующего импульса; если между двумя соседними паузами в двоичном сигнале, имеющими число нулей больше, чем q+1 = 3 + 1=4, насчитывается четное число единиц, то заполнение второй паузы начинается с сигнала В00 V; если число единиц между двумя вышеупомянутыми паузами нечетное, то заполнение второй паузы начинается с сигнала 000V.

, управляемый импульсами тактовой частоты ИУ от генераторного оборудования, а также некоторое количество сумматоров по модулю 2, соединенных с выходами соответствующих триггеров (рис. 15.13, б). Элемент

, управляемый импульсами тактовой частоты ИУ от генераторного оборудования, а также некоторое количество сумматоров по модулю 2, соединенных с выходами соответствующих триггеров (рис. 15.13, б). Элемент  на схеме отражает наличие

на схеме отражает наличие  ) или отсутствие

) или отсутствие  связи триггера 7} со схемой сложения.

связи триггера 7} со схемой сложения.

Дескремблированный сигнал

Дескремблированный сигнал  равен соответственно

равен соответственно  При отсутствии ошибок в канале связи, когда

При отсутствии ошибок в канале связи, когда  , имеем

, имеем  ,= D. Параметры ФПСП определяются видом алгебраического полинома, описывающего структуру ПСП,

,= D. Параметры ФПСП определяются видом алгебраического полинома, описывающего структуру ПСП,  ,.С увеличением числа п растет период ПСП, равный

,.С увеличением числа п растет период ПСП, равный  , и соответственно сдвигается влево «провал» в спектре скремблированного сигнала S (см. штриховую функцию на рис. 15.5, б). С увеличением числа k ненулевых коэффициентов Cj этот «провал» углубляется и расширяется по частоте, однако при этом в случае появления в канале передачи одиночных ошибок дескремблер «размножает» их в (k + 1) раз. Практическое применение получили ФПСП с компромиссными параметрами[23]:

, и соответственно сдвигается влево «провал» в спектре скремблированного сигнала S (см. штриховую функцию на рис. 15.5, б). С увеличением числа k ненулевых коэффициентов Cj этот «провал» углубляется и расширяется по частоте, однако при этом в случае появления в канале передачи одиночных ошибок дескремблер «размножает» их в (k + 1) раз. Практическое применение получили ФПСП с компромиссными параметрами[23]:  (т.е. «=15,

(т.е. «=15,  ) и

) и

(

( = 10,

= 10,  = 1; k = 3). Отметим, что линейный сигнал, полученный путем скремблирования (см. рис. 15.13, а), остается униполярным и имеет постоянную составляющую, которая хотя и не равна 0, но изменяется в очень малых пределах. Это позволяет «потерять» ее в линейном тракте (из-за разделительных элементов), а затем «восстановить» в регенераторе, не искажая форму импульсов.

= 1; k = 3). Отметим, что линейный сигнал, полученный путем скремблирования (см. рис. 15.13, а), остается униполярным и имеет постоянную составляющую, которая хотя и не равна 0, но изменяется в очень малых пределах. Это позволяет «потерять» ее в линейном тракте (из-за разделительных элементов), а затем «восстановить» в регенераторе, не искажая форму импульсов. символов исходного двоичного сигнала заменяется группой из я символов двоичного линейного сигнала, что выражается формулой

символов исходного двоичного сигнала заменяется группой из я символов двоичного линейного сигнала, что выражается формулой  , Поскольку

, Поскольку  , то для каждой из

, то для каждой из  возможных комбинаций нулей и единиц в пакете из

возможных комбинаций нулей и единиц в пакете из  символов ДС можно подобрать свою комбинацию, заранее определенную из

символов ДС можно подобрать свою комбинацию, заранее определенную из  возможных (в пакете из

возможных (в пакете из  двоичных символов ЛС), что позволяет избавиться от длинных серий нулей (или единиц) и сохранить возможности контроля за качеством работы регенераторов без прерывания связи и использования специальных испытательных сигналов.

двоичных символов ЛС), что позволяет избавиться от длинных серий нулей (или единиц) и сохранить возможности контроля за качеством работы регенераторов без прерывания связи и использования специальных испытательных сигналов. , в которых с каждым отдельным символом исходной последовательности сопоставляются два двоичных символа линейного кода.

, в которых с каждым отдельным символом исходной последовательности сопоставляются два двоичных символа линейного кода.

. Одной из модернизаций приведенного кода является код AMI, в котором каждый исходный символ ДС кодируется одной из двух возможных двухразрядных комбинаций. Например, вместо 0 передается 10 или 01, а вместо 1 — соответственно 11 или 00. При этом каждый следующий одноименный символ принимает обязательно другое возможное значение. Например, комбинация ДС вида 110010 будет кодироваться в виде 11.00.01.10.11.01. В таком коде при нормальной работе никогда не может быть более двух импульсов или более двух пауз подряд. Нарушение этой закономерности свидетельствует о появлении ошибки.

. Одной из модернизаций приведенного кода является код AMI, в котором каждый исходный символ ДС кодируется одной из двух возможных двухразрядных комбинаций. Например, вместо 0 передается 10 или 01, а вместо 1 — соответственно 11 или 00. При этом каждый следующий одноименный символ принимает обязательно другое возможное значение. Например, комбинация ДС вида 110010 будет кодироваться в виде 11.00.01.10.11.01. В таком коде при нормальной работе никогда не может быть более двух импульсов или более двух пауз подряд. Нарушение этой закономерности свидетельствует о появлении ошибки. если

если

с длительностью

с длительностью  .

. , которые формируются на выходе умножителя частоты 5, осуществляется преобразование из параллельного кода в последовательный.

, которые формируются на выходе умножителя частоты 5, осуществляется преобразование из параллельного кода в последовательный. поступают в блок 1, который осуществляет преобразование 6-битовых комбинаций из последовательно- го кода в параллельный. Далее эти комбинации переписываются в ЗУ 2 при поступлении разрешающих импульсов блочной частоты

поступают в блок 1, который осуществляет преобразование 6-битовых комбинаций из последовательно- го кода в параллельный. Далее эти комбинации переписываются в ЗУ 2 при поступлении разрешающих импульсов блочной частоты  которые формируются на выходе делителя частоты 10 с коэффициентом деления 6. Выходы ЗУ 2 подключены параллельно к входам цифрового преобразователя 3 и дешифратора ошибок (ДШО) 5. Блок 3 в соответствии с алфавитом кода 5В6В осуществляет обратное преобразование 6-битовой кодовой комбинации в 5-битовую, которая затем в блоке 4 преобразуется из параллельного кода в последовательный.

которые формируются на выходе делителя частоты 10 с коэффициентом деления 6. Выходы ЗУ 2 подключены параллельно к входам цифрового преобразователя 3 и дешифратора ошибок (ДШО) 5. Блок 3 в соответствии с алфавитом кода 5В6В осуществляет обратное преобразование 6-битовой кодовой комбинации в 5-битовую, которая затем в блоке 4 преобразуется из параллельного кода в последовательный.

, формируемых на выходе умножителя частоты 11

, формируемых на выходе умножителя частоты 11  .

. в накопитель б поступит

в накопитель б поступит  импульсов сбоя, где

импульсов сбоя, где  -емкость накопителя, то последний из них пройдет через схему совпадения И8 и поступит на схему запрета 9. В результате будет запрещен один импульс линейной частоты, что вызовет задержку на один такт импульсов блочной частоты на выходе делителя 10. Одновременно при этом производится сброс в первоначальное состояние накопителя ошибок и ФИА. Очередной сдвиг на один такт импульсов блочной частоты будет продолжаться до тех пор, пока не найдется их правильное положение, при котором они совпадают по времени с приходом последнего, шестого импульса 6-битовой комбинации линейного сигнала. В этом случае поток ошибок резко сокращается, поэтому хотя ФИА и «запускается» от случайной ошибки, но за время анализа Та вряд ли пройдет d ошибок. Соответственно не изменится и режим блочной синхронизации.

-емкость накопителя, то последний из них пройдет через схему совпадения И8 и поступит на схему запрета 9. В результате будет запрещен один импульс линейной частоты, что вызовет задержку на один такт импульсов блочной частоты на выходе делителя 10. Одновременно при этом производится сброс в первоначальное состояние накопителя ошибок и ФИА. Очередной сдвиг на один такт импульсов блочной частоты будет продолжаться до тех пор, пока не найдется их правильное положение, при котором они совпадают по времени с приходом последнего, шестого импульса 6-битовой комбинации линейного сигнала. В этом случае поток ошибок резко сокращается, поэтому хотя ФИА и «запускается» от случайной ошибки, но за время анализа Та вряд ли пройдет d ошибок. Соответственно не изменится и режим блочной синхронизации. и интервал анализа

и интервал анализа  выбираются из компромиссных соображений и с учетом ступени иерархии ЦСП. Максимальное время поиска блочной синхронизации, которое для линейного кода 5В6В равно

выбираются из компромиссных соображений и с учетом ступени иерархии ЦСП. Максимальное время поиска блочной синхронизации, которое для линейного кода 5В6В равно  , должно быть в 2—3 раза меньше, чем время поиска цикловой синхронизации группового двоичного сигнала (см. параграф 13.6).

, должно быть в 2—3 раза меньше, чем время поиска цикловой синхронизации группового двоичного сигнала (см. параграф 13.6).