Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Загальні відомості про мову описання апаратури AHDLСодержание книги

Поиск на нашем сайте

Мова описання апаратури AHDL (Altera Hardware Description Language) розроблена фірмою Altera і призначена для описання комбінаційних і послідовних логічних пристроїв, групових операцій, цифрових автоматів з урахуванням особливостей ПЛІС фірми Altera. Він повністю інтегрується з системою автоматичного проектування MAX+PLUS II. Файли описання апаратури, написані на мові AHDL, мають розширення.tdf (Text design file). Для створення tdf-файлу можна використовувати як текстовий редактор системи MAX+PLUS II, так і будь-який інший. Проект, виконаний у вигляді tdf-файлу, компілюється і використовується для формування файлу програмування або завантаження ПЛІС фірми Altera. Оператори та елементи мови AHDL є достатньо потужними та універсальними засобами описання алгоритмів функціонування цифрових пристроїв. Мова описання апаратури AHDL дає можливість створювати ієрархічні проекти в рамках однєї цієї мови або ж в ієрархічному проекті використовувати як tdf-файли, написані на мові AHDL, так і інші типи текстового описання апаратури. Для створення проектів на AHDL можна, звичайно, користуватись будь-яким текстовим редактором, але текстовий редактор системи MAX+PLUS II надає ряд додаткових можливостей для введення, компіляції і верифікації проекту. Файли, створені на мові AHDL, легко інтегруються в ієрархічну структуру проекту. Система MAX+PLUS II дозволяє автоматично створювати символ компонента, алгоритм функціонування якого описано tdf-файлом, а потім вставити його в файл схемного описання (gdf-файл). Додатково, користувач може вводити власні функції, крім розроблених фірмою Altera близько 300 макрофункцій. Для всіх функцій, включених до макробібліотеки системи MAX+PLUS II, фірма Altera поставляє файли з розширенням.inc (include design file). При розподіленні ресурсів пристроїв проектувальник може користуватись програмами текстового редактору або операторами мови AHDL. Крім того, розробник може перевірити синтаксис і зробити повну компіляцію. Будь-які помилки автоматично фіксуються обробником повідомлень та інформація про їх наявність з’являється у вікні текстового редактору, що оптимізує час розробки пристрою. 7. Реалізація в інтегрованому середовищі MAX+PLUS II базових пристроїв мікроелектроніки Теоретичні відомості про тригери

Базовою структурною одиницею для побудови комбінаційних логічних схем є логічний елемент (вентиль). У випадку послідовних логічних схем роль такої структурної одиниці відіграє тригер. RS-тригер Умовне позначення RS-тригеру подано на рис. 7.1.1: RS-тригер має два входи R і S та два виходи Q1 та Q2. В тригерах виходи завжди знаходяться в протилежних (компланарних) станах. Іншою мовою, якщо на вході Q1 ми маємо логічну одиницю, то на виході Q2 буде рівень логічного нуля, і навпаки. Входи R і S розглядуваного тригера називають відповідно входом встановлення 1 і входом встановлення 0.

Рис. 7.1.1. Умовне позначення RS-тригеру

Принцип роботи RS-тригеру ілюструє його таблиця дійсності (табл. 7.1.1).

Табл. 1.1. Таблиця дійсності RS-тригеру

При поданні на обидва входи тригера рівня логічного нуля (R=S=0) на обох виходах встановлюється логічна одиниця (Q1=Q2=1). Це заборонений стан тригеру; він не використовується. Згідно другому рядку таблиці дійсності на виході Q1 встановлюється логічна 1. В даному випадку кажуть, що тригер встановлений у стан 1. Згідно третього рядка, при S=1 і R=0 відбувається скидання сигналу на вході Q1 (очищення виходу Q1) до рівня логічного 0. Це значить, що тригер встановлено у стан 0. Четвертий рядок таблиці дійсності відповідає R=S=1. В даному випадку тригер знаходиться в стані спокою: на виходах Q1 і Q2 зберігаються попередні комплементарні рівні сигналу. Це режим збереження. Із табл. 7.1.1 видно, що встановлення тригеру у стан 1 (встановлення 1 на виході Q1) ініціює логічний 0 на вході S. Аналогічно встановлення тригеру в стан 0 (встановлення 0 на виході Q1) ініціює логічний 0 на вході R. Так як зміна стану RS-тригеру обумовлена появою 0 на одному з його входів, то вірогідніше, точнішим зображенням даної схеми було б умовне графічне зображення, приведене на рис. 7.1.2.

Рис. 7.1.2. Умовне графічне позначення RS-тригеру

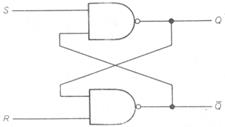

Рис. 7.1.3. RS-тригер, побудований на логічних елементах І-НЕ

Особливу увагу треба звернути на інвертуючі кола у входів R та S. Вони показують, що активним рівнем сигналу для встановлення тригеру в стан 1 і 0 є рівень логічного 0 на одному із входів. RS-тригер часто називають RS-фіксатором, або тригером з роздільними входами.

Синхронний RS-тригер Умовне графічне позначення для синхронного RS-тригеру показано на рис. 7.1.4. Воно подібне до звичайного RS-тригеру; відмінність полягає в появі одного додаткового, так званого синхронізуючого входу, що позначається CLK.

Рис. 7.1.4. Умовне графічне позначення синхронного RS-тригеру

Принцип роботи синхронного RS-тригеру ілюструє його таблиця дійсності (табл. 7.1.2).

Табл. 7.1.2. Таблиця дійсності синхронного RS-тригеру

Тільки верхні три рядки таблиці дійсності описують реальні режими роботи RS-тригеру. Нижній рядок відповідає забороненому стану і ніколи не використовується. З таблиці видно, що стан виходів синхронного RS-тригеру може змінюватись лише в моменти приходу тактових імпульсів. В даному випадку кажуть, що тригер працює синхронно: процес переключення його знаходиться в синхронізмі з тактовими імпульсами. Важливу роль в багатьох цифрових схемах відіграє ще одна характеристика RS-тригеру – наявність пам’яті. Дійсно, якщо тригер встановлений в стан 1 або 0, то він залишається в такому стані навіть при деяких змінах вхідних сигналів.

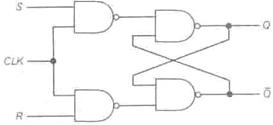

Рис. 7.1.5. Синхронний RS-тригер, побудований на логічних елементах І-НЕ

Щоб отримати синхронний RS-тригер, в схему звичайного RS-тригеру потрібно ввести два додаткових логічних елемента І-НЕ, як показано на рис. 7.1.5.

D-тригер Умовне графічне позначення D-тригеру подано на рисунку 7.1.6. У цього тригера є лише один інформаційний вхід D, а також синхронізуюзуючий вхід CLK. D-тригер часто називають тригером з затримкою. Слово “затримка” означає те, що відбувається з даними (інформацією), що поступає на вхід D. Інформаційний сигнал (0 або 1), поступаючи на цей вхід затримується у тригері рівно на один такт, перед тим як з’явитись на виході Q.

Рис. 7.1.6. Умовне графічне позначення D-тригеру

Спрощена таблиця дійсності для D-тригеру подана нижче.

Табл. 7.1.3. Таблиця дійсності D-тригеру

Слід звернути увагу, що сигнал на виході Q в такті n+1 повторює сигнал, що був на вході D в попередньому такті n. D-тригер можливо отримати з тактуємого RS-тригеру, додаючи до останнього інвертор, як показано на рис. 7.1.7.

Рис. 7.1.7. Схема D-тригера

На рис. 7.1.8 показано умовне позначення типового серійно випускаємого D-тригеру. Він має два додаткових входи – попереднього встановлення (PS) і очищення (CLR). Логічний 0 на вході PS ініціює встановлення логічної 1 на виході Q. Логічний 0 на вході CLR ініціює очистку виходу Q. В активних станах входи PS і CLR блокують дію входів D і CLK; при розблокуванні входи D і CLK діють аналогічно звичайному D-тригеру, що зображений на рис. 7.1.6.

Рис. 7.1.8. Умовне графічне позначення серійного інтегрального D-тригеру

JK-тригер JK-тригер – це універсальний тригер, що має характеристики всіх інших типів тригерів. Умовне графічне позначення JK-тригеру подано на рис. 7.1.9. JK-тригер має два інформаційні входи: J і K, і вхід синхронізації CLK і, як і всі тригери два комплементарних виходи Q1 і Q2. Таблиця дійсності для JK-тригера приведена в табл. 7.1.4. Коли на обидва входи J і K подається рівень логічного 0, тригер блокується, і стан його виходів не змінюється. В цьому випадку тригер знаходиться в режимі збереження.

Рис. 7.1.9. Умовне графічне позначення JK-тригеру

Табл. 7.1.4. Таблиця дійсності JK-тригеру

Рядки 2 і 3 таблиці дійсності описують режими, що відповідають встановленню тригера в стани 0 на 1. Рядок 4 ілюструє дуже важливий режим роботи JK-тригера – переключення. Якщо на обох входах J і K встановлена логічна 1, то наступні тактові імпульси будуть викликати перекидання рівнів сигналів на виходах тригера від 1 до 0, от 0 до 1 і так далі. Така робота подібна переключенню тумблера, звідки і походить назва режиму. Умовне графічне позначення JK-тригера, що входить до складу інтегральної схеми показано на рис. 7.1.10. В порівнянні з тригером на рис. 7.1.9 даний тригер має два додаткових асинхронних входи (вхід попереднього встановлення і вхід очищення). Синхронними входами є інформаційні входи J та K і синхронізуючий вхід CLK.

Рис. 7.1.10. Умовне графічне позначення серійного інтегрального JK-тригеру

При реалізації тригерів за допомогою мови AHDL доцільно користуватись примітивами тригерів. В табл. 7.1.5 наведено всі примітиви тригерів, що використовуються при описанні роботи апаратури.

Табл. 7.1.5. Примітиви тригерів в AHDL

Виводи тригерів: D, T, J, K, S, R – інформаційні входи; CLK – вхід тактового сигналу (активний перепад 0->1); CLRN – вхід асинхронного скидання тригера (активний рівень – логічний нуль); PRN – вхід асинхронного встановлення тригера (активний рівень – логічний нуль); ENA – вхід дозволу роботи (активний рівень – логічна одиниця).

7.1.5 Програма реалізації тригерів в інтегрованому середовищі MAX+PLUS II Програма для реалізації тригерів за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:Title "triggers"; Subdesign triggers ( D,T,J,K,S,R,CLK,CLRN,PRN,ENA: input; Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8,Q9: output; ) Begin Q1 = DFF(D,CLK,CLRN,PRN); Q2 = DFFE (D,CLK,CLRN,PRN,ENA); Q3 = TFF (T,CLK,CLRN,PRN); Q4 = TFFE (T, CLK, CLRN, PRN, ENA); Q5 = JKFF (J, K, CLK, CLRN, PRN); Q6 = JKFFE (J,K, CLK, CLRN, PRN, ENA); Q7 = SRFF (S, R, CLK, CLRN, PRN); Q8 = SRFFE (S, R, CLK, CLRN, PRN, ENA); Q9 = LATCH (D, ENA); End;

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-06; просмотров: 216; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.220 (0.007 с.) |