Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Перелік умовних позначень, символів, скорочень і термінівСтр 1 из 9Следующая ⇒

Зміст

Перелік умовних позначень, символів, скорочень і термінів Вступ 1. Генезис програмувальних логічних інтегральних схем, їх класифікація та архітектура 2. Призначення та структура системи автоматизованого проектування MAX+PLUS II 3. Додатки системи автоматизованого проектування MAX+PLUS II 4. Процедура розробки нового проекту в системі автоматизованого проектування MAX+PLUS II 5. Процедура компіляції створеного проекту в системі автоматизованого проектування MAX+PLUS II 6. Загальні відомості про мову описання апаратури AHDL 7. Реалізація в інтегрованому середовищі MAX+PLUS II базових пристроїв мікроелектроніки 7.1 Теоретичні відомості про тригери 7.1.1 RS-тригер 7.1.2 Синхронний RS-тригер 7.1.3 D-тригер 7.1.4 JK-тригер 7.1.5 Програми реалізації тригерів в інтегрованому середовищі MAX+PLUS II 7.1.6 Результати програмної реалізації тригерів 7.2 Теоретичні відомості про регістри 7.2.1 Послідовні регістри зсуву 7.2.2 Паралельні регістри зсуву 7.2.3 Програма реалізації регістрів в інтегрованому середовищі MAX+PLUS II 7.2.4 Результати програмної реалізації регістрів 7.3 Теоретичні відомості про лічильники 7.3.1 Лічильник з крізним переносом 7.3.2 Асинхронний лічильник з модулем 10 7.3.3 Лічильник віднімання 7.3.4 Програми реалізації лічильників в інтегрованому середовищі MAX+PLUS II 7.3.5 Результати програмної реалізації лічильників 7.4 Теоретичні відомості про мультиплексори, демультиплексори, шифратори, дешифратори 7.4.1 Мультиплексор 7.4.2 Демультиплексор 7.4.3 Шифратор 7.4.4 Дешифратор 7.4.5 Програми реалізації мультиплексорів, демультиплексорів, шифраторів, дешифраторів в інтегрованому середовищі MAX+PLUS II 7.4.6 Результати програмної реалізації мультиплексорів, демультиплексорів, шифраторів, дешифраторів 7.5 Теоретичні відомості про суматори, віднімачі 7.5.1 Суматори 7.5.2 Віднімачі 7.5.3 Програми реалізації суматорів, віднімачів в інтегрованому середовищі MAX+PLUS II 7.5.4 Результати програмної реалізації суматорів, віднімачів 8. Проект реалізації COM-порту в САПР MAX+PLUS II 8.1 Теоретичні відомості про послідовні порти і протокол RS-232 8.2 Структура COM-порту при його реалізації в САПР MAX+PLUS II 8.3 Програми структурних компонентів COM-порту мовою AHDL в САПР MAX+PLUS II 8.4 Результати програмної реалізації COM-порту в САПР MAX+PLUS II

Висновки Використана література

Перелік умовних позначень, символів, скорочень і термінів

АДП – апаратура передачі даних; БМК – базовий матричний кристал; ПЛІС – програмувальна логічна інтегральна схема; ПЛМ – програмувальна логічна інтегральна матриця; ПЛП – програмувальний логічний пристрій; ППЗП – програмувальній постійній запам’ятовуючій пристрій; ООД – одно кінцевий об’єкт передачі даних САПР – система автоматизованого проектування; СБФ – система булєвих функцій; AMD – Advanced Micro Devices; CLK – CLocK; CPLD – Complex Programmable Logic Device; DCE – Data Communication Equipment; DTE – Data Transfer Equipment; ENA – ENAble; FLEX – Flexible Logic Element Matrix; FPGA – Field Programmable Gate Array; GA – Gate Array; GAL – Generic Array Logic; IOB – Input/Output Element; JTAG – Joint Test Action Group; LAB – Logic Array Block; LE – Logic Element; MAX – Multiple Array Matrix; PLA – Programmable Logic Array; PLD – Programmable Logic Devices; PLS – Programmable Logic Sequencers; PROM – Programmable Read Only Memory; SPLD – Standart Programmable Logic Devices. Вступ

Широке впровадження електроніки й автоматики в усі сфери людської діяльності, що спостерігається в даний час, пред'являє все більш жорсткі вимоги до виробів електронної техніки. Це пов'язано, з одного боку, зі зростанням важливості і складності розв'язуваних задач, а, з іншого боку, необхідністю поліпшення таких характеристик, як швидкодія, надійність, споживана потужність, габарити, вартість та інше. Одним з шляхів вирішення даної проблеми є широке використання програмувальних логічних інтегральних схем (ПЛІС - Programmable Logic Devices - PLDs). ПЛІС являють собою нову елементну базу, що володіє гнучкістю замовлених ВІС і доступністю традиційної "твердої" логіки. Головною відмітною властивістю ПЛІС, на відміну від “жорсткої” логіки, є можливість настроювання на виконання заданих функцій самим користувачем. Сучасні ПЛІС характеризуються низькою вартістю, високою швидкодією, значними функціональними можливостями, багаторазовістю перепрограмування, низкою споживаною потужністю й інше. При цьому час розробки на основі ПЛІС навіть досить складних проектів може складати усього кілька годин. Власно кажучи, розробка пристроїв на основі ПЛІС являє собою нову технологію проектування електронних схем, включаючи їх виготовлення і супроводження. Доказом перспективності нової елементної бази служить щорічна поява нових поколінь ПЛІС, а також постійно зростаючий обсяг випуску вже розроблених ПЛІС.

Істотною перешкодою широкого практичного використання ПЛІС є відсутність ефективних методів синтезу. Справа в тому, що в основу архітектури сучасних ПЛІС покладена структура програмувальних логічних матриць (ПЛМ — Programmable Array Logics — PALs), що являє собою пари матриць: І й АБО, у якій програмується матриця І, а матриця АБО має фіксоване положення. Методи й алгоритми синтезу на такій структурі одержали назву двухуровнего синтезу і бурхливо розвивалися в 80-х роках. З часом інтерес дослідників на багато років залучив багаторівневий синтез, використовуваний при проектуванні цифрових систем на основі FPGA (Field Programmable Gate Array). В останні роки спостерігається явне протиріччя: архітектури ПЛІС бурхливо розвиваються й удосконалюються, а методи проектування на їх основі залишаються без зміни. Інтегроване середовище MAX+PLUS II фірми Altera пропонує повний спектр можливостей логічного дизайну: різноманітні засоби опису проектів з ієрархічною структурою, потужний логічний синтез, компіляцію з заданими часовими параметрами, розподілення на підпрограми основного проекту, функціональне і часове тестування (симуляцію), тестування декількох взаємопов’язаних властивостей, аналіз часових параметрів системи, автоматичну локалізацію помилок, а також програмування і верифікацію помилок. Відносно низьку популярність даного інтегрованого середовища серед вітчизняних проектувальників можливо пояснити відсутністю детальної та ємної документації українською мовою про можливості та властивості MAX+PLUS II. Для спрощення розуміння читачем структурної організації і функціонального призначення додатків інтегрованого середовища в роботі наведено генезис програмувальних логічних інтегральних схем, їх класифікація, архітектура, детально розписана процедура створення нового проекту і процес його компіляції. В навчальному посібнику наведено приклади опису в інтегрованому середовищі MAX+PLUS II всіх базових пристроїв мікроелектроніки, як то: 1) JK-тригера, D-тригера, RS-тригера; 2) послідовних регістрів зсуву, паралельних кільцевих регістра зсуву; 3) лічильників з крізним переносом, асинхронних лічильників, лічильників віднімання, універсального лічильника; 4) шифраторів, дешифраторів, мультиплексорів, демультиплексорів (з використанням функцій алгебри логіки і таблиць дійсності); 5) суматорів, віднімачів.

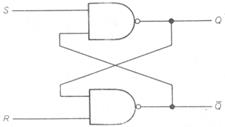

RS-тригер Умовне позначення RS-тригеру подано на рис. 7.1.1: RS-тригер має два входи R і S та два виходи Q1 та Q2. В тригерах виходи завжди знаходяться в протилежних (компланарних) станах. Іншою мовою, якщо на вході Q1 ми маємо логічну одиницю, то на виході Q2 буде рівень логічного нуля, і навпаки. Входи R і S розглядуваного тригера називають відповідно входом встановлення 1 і входом встановлення 0.

Рис. 7.1.1. Умовне позначення RS-тригеру

Принцип роботи RS-тригеру ілюструє його таблиця дійсності (табл. 7.1.1).

Табл. 1.1. Таблиця дійсності RS-тригеру

При поданні на обидва входи тригера рівня логічного нуля (R=S=0) на обох виходах встановлюється логічна одиниця (Q1=Q2=1). Це заборонений стан тригеру; він не використовується. Згідно другому рядку таблиці дійсності на виході Q1 встановлюється логічна 1. В даному випадку кажуть, що тригер встановлений у стан 1. Згідно третього рядка, при S=1 і R=0 відбувається скидання сигналу на вході Q1 (очищення виходу Q1) до рівня логічного 0. Це значить, що тригер встановлено у стан 0. Четвертий рядок таблиці дійсності відповідає R=S=1. В даному випадку тригер знаходиться в стані спокою: на виходах Q1 і Q2 зберігаються попередні комплементарні рівні сигналу. Це режим збереження. Із табл. 7.1.1 видно, що встановлення тригеру у стан 1 (встановлення 1 на виході Q1) ініціює логічний 0 на вході S. Аналогічно встановлення тригеру в стан 0 (встановлення 0 на виході Q1) ініціює логічний 0 на вході R. Так як зміна стану RS-тригеру обумовлена появою 0 на одному з його входів, то вірогідніше, точнішим зображенням даної схеми було б умовне графічне зображення, приведене на рис. 7.1.2.

Рис. 7.1.2. Умовне графічне позначення RS-тригеру

Рис. 7.1.3. RS-тригер, побудований на логічних елементах І-НЕ

Особливу увагу треба звернути на інвертуючі кола у входів R та S. Вони показують, що активним рівнем сигналу для встановлення тригеру в стан 1 і 0 є рівень логічного 0 на одному із входів. RS-тригер часто називають RS-фіксатором, або тригером з роздільними входами.

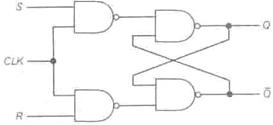

Синхронний RS-тригер Умовне графічне позначення для синхронного RS-тригеру показано на рис. 7.1.4. Воно подібне до звичайного RS-тригеру; відмінність полягає в появі одного додаткового, так званого синхронізуючого входу, що позначається CLK.

Рис. 7.1.4. Умовне графічне позначення синхронного RS-тригеру

Принцип роботи синхронного RS-тригеру ілюструє його таблиця дійсності (табл. 7.1.2).

Табл. 7.1.2. Таблиця дійсності синхронного RS-тригеру

Тільки верхні три рядки таблиці дійсності описують реальні режими роботи RS-тригеру. Нижній рядок відповідає забороненому стану і ніколи не використовується. З таблиці видно, що стан виходів синхронного RS-тригеру може змінюватись лише в моменти приходу тактових імпульсів. В даному випадку кажуть, що тригер працює синхронно: процес переключення його знаходиться в синхронізмі з тактовими імпульсами. Важливу роль в багатьох цифрових схемах відіграє ще одна характеристика RS-тригеру – наявність пам’яті. Дійсно, якщо тригер встановлений в стан 1 або 0, то він залишається в такому стані навіть при деяких змінах вхідних сигналів.

Рис. 7.1.5. Синхронний RS-тригер, побудований на логічних елементах І-НЕ

Щоб отримати синхронний RS-тригер, в схему звичайного RS-тригеру потрібно ввести два додаткових логічних елемента І-НЕ, як показано на рис. 7.1.5.

D-тригер Умовне графічне позначення D-тригеру подано на рисунку 7.1.6. У цього тригера є лише один інформаційний вхід D, а також синхронізуюзуючий вхід CLK. D-тригер часто називають тригером з затримкою. Слово “затримка” означає те, що відбувається з даними (інформацією), що поступає на вхід D. Інформаційний сигнал (0 або 1), поступаючи на цей вхід затримується у тригері рівно на один такт, перед тим як з’явитись на виході Q.

Рис. 7.1.6. Умовне графічне позначення D-тригеру

Спрощена таблиця дійсності для D-тригеру подана нижче.

Табл. 7.1.3. Таблиця дійсності D-тригеру

Слід звернути увагу, що сигнал на виході Q в такті n+1 повторює сигнал, що був на вході D в попередньому такті n. D-тригер можливо отримати з тактуємого RS-тригеру, додаючи до останнього інвертор, як показано на рис. 7.1.7.

Рис. 7.1.7. Схема D-тригера

На рис. 7.1.8 показано умовне позначення типового серійно випускаємого D-тригеру. Він має два додаткових входи – попереднього встановлення (PS) і очищення (CLR). Логічний 0 на вході PS ініціює встановлення логічної 1 на виході Q. Логічний 0 на вході CLR ініціює очистку виходу Q. В активних станах входи PS і CLR блокують дію входів D і CLK; при розблокуванні входи D і CLK діють аналогічно звичайному D-тригеру, що зображений на рис. 7.1.6.

Рис. 7.1.8. Умовне графічне позначення серійного інтегрального D-тригеру

JK-тригер JK-тригер – це універсальний тригер, що має характеристики всіх інших типів тригерів. Умовне графічне позначення JK-тригеру подано на рис. 7.1.9. JK-тригер має два інформаційні входи: J і K, і вхід синхронізації CLK і, як і всі тригери два комплементарних виходи Q1 і Q2. Таблиця дійсності для JK-тригера приведена в табл. 7.1.4. Коли на обидва входи J і K подається рівень логічного 0, тригер блокується, і стан його виходів не змінюється. В цьому випадку тригер знаходиться в режимі збереження.

Рис. 7.1.9. Умовне графічне позначення JK-тригеру

Табл. 7.1.4. Таблиця дійсності JK-тригеру

Рядки 2 і 3 таблиці дійсності описують режими, що відповідають встановленню тригера в стани 0 на 1. Рядок 4 ілюструє дуже важливий режим роботи JK-тригера – переключення. Якщо на обох входах J і K встановлена логічна 1, то наступні тактові імпульси будуть викликати перекидання рівнів сигналів на виходах тригера від 1 до 0, от 0 до 1 і так далі. Така робота подібна переключенню тумблера, звідки і походить назва режиму. Умовне графічне позначення JK-тригера, що входить до складу інтегральної схеми показано на рис. 7.1.10. В порівнянні з тригером на рис. 7.1.9 даний тригер має два додаткових асинхронних входи (вхід попереднього встановлення і вхід очищення). Синхронними входами є інформаційні входи J та K і синхронізуючий вхід CLK.

Рис. 7.1.10. Умовне графічне позначення серійного інтегрального JK-тригеру

При реалізації тригерів за допомогою мови AHDL доцільно користуватись примітивами тригерів. В табл. 7.1.5 наведено всі примітиви тригерів, що використовуються при описанні роботи апаратури.

Табл. 7.1.5. Примітиви тригерів в AHDL

Виводи тригерів: D, T, J, K, S, R – інформаційні входи; CLK – вхід тактового сигналу (активний перепад 0->1); CLRN – вхід асинхронного скидання тригера (активний рівень – логічний нуль); PRN – вхід асинхронного встановлення тригера (активний рівень – логічний нуль); ENA – вхід дозволу роботи (активний рівень – логічна одиниця).

7.1.5 Програма реалізації тригерів в інтегрованому середовищі MAX+PLUS II Програма для реалізації тригерів за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд:Title "triggers"; Subdesign triggers ( D,T,J,K,S,R,CLK,CLRN,PRN,ENA: input; Q1,Q2,Q3,Q4,Q5,Q6,Q7,Q8,Q9: output; ) Begin Q1 = DFF(D,CLK,CLRN,PRN); Q2 = DFFE (D,CLK,CLRN,PRN,ENA); Q3 = TFF (T,CLK,CLRN,PRN); Q4 = TFFE (T, CLK, CLRN, PRN, ENA); Q5 = JKFF (J, K, CLK, CLRN, PRN); Q6 = JKFFE (J,K, CLK, CLRN, PRN, ENA); Q7 = SRFF (S, R, CLK, CLRN, PRN); Q8 = SRFFE (S, R, CLK, CLRN, PRN, ENA); Q9 = LATCH (D, ENA); End;

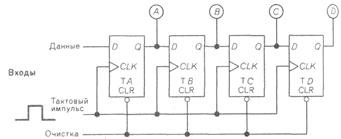

Послідовні регістри зсуву Схема одного з типових регістрів зсуву подана на рис. 7.2.1. Цей регістр реалізований на 4 D-тригерах. Такий регістр має назву 4-розрядний регістр зсуву, оскільки він дозволяє зберігати 4 двійкових розряди даних А, B, C, D.

Рис.7.2.1. 4-розрядний послідовний регістр зсуву

За допомогою табл. 7.2.1 і рис. 7.2.1 ми маємо можливість спостерігати за роботою цього пристрою. Спочатку очистимо регістр (встановимо рівні логічного нуля на його виходах А, B, C, D). Для цього потрібно подати логічний 0 на вхід очищення CLR. Отриманому стану регістра зсуву відповідає рядок 1 табл. 7.2.1 До приходу тактового імпульсу виходи регістру залишаються в стані 0000. Подамо перший імпульс на синхронізуючий вхід CLK; індикатор покаже число 1000 (рядок 3 в табл. 7.2.1), оскільки на тактовому імпульсі логічна 1 з інформаційного входу тригера TA переноситься на його логічний вихід Q. Тепер при наявності логічної 1 на інформаційному вході регістру ця одиниця з кожним тактовим імпульсом вводиться в розряд А, а введені раніше одиниці зсуваються на одну позицію (розряд) вправо (тактові імпульси 2 і 3 в табл. 7.2.1). Таким самим чином при подачі на інформаційний вхід логічного 0 цей нуль при кожному тактовому імпульсі вводиться в розряд А, а введені раніше одиниці та нулі зсуваються вправо (тактові імпульси 4-8 в табл. 7.2.1). Перед приходом тактового імпульсу 9 на інформаційному вході встановлюється 1, а перед приходом імпульсу 10 цей вхід повертається до 0. В час дії тактових імпульсів 9-13 введена в регістр на імпульсі 9 одиниця буде зміщуватись на індикаторі вправо. Рядок 15 в табл. 7.2.1 показує, на імпульсі 13 ця одиниця покидає крайній правий розряд регістру зсуву і втрачається.

Табл.7.2.1. Робота 4-розрядного регістру зсуву

Нагадаємо, що D-тригер називають також тригером з затримкою. Він просто передає інформаційний сигнал з входу D на вихід Q з затримкою на один такт. Прилад, схема якого приведена на рис. 7.2.1 має назву послідовного регістру зсуву. Термін “послідовний” відображає той факт, що в цей регістр дані вводяться порозрядно. Наприклад, щоб ввести в регістр двійкову комбінацію 0111 треба пройти всю послідовність станів від рядка 1 до рядка 6 в табл. 7.2.1. Послідовне завантаження 4-бітової комбінації 0111 в послідовний регістр відбувається за 5 тактів (рядок 2 можливо виключити). Інший спосіб завантаження регістру – паралельне (або розширене) завантаження, при якому всі інформаційні біти вводяться в регістр одночасно “за командою” одного тактового імпульсу. Регістр зсуву на рис. 7.2.1 можливо трансформувати в 5-розрядний, додав до схеми ще один D-тригер. Регістри зсуву частіше бувають 4-, 5- або 8-розрядними. В них можливо використання не тільки D-тригеру, але й тригерів іншого типу (наприклад, JK-тригера, або синхронних RS-тригерів).

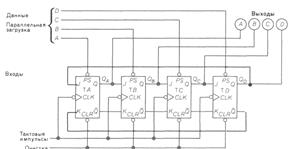

Паралельні регістри зсуву Послідовний регістр зсуву, робота якого описана вище має два суттєві недоліки: він дозволяє вводити тільки по одному біту інформації на кожному тактовому імпульсі і, крім того, кожний раз при зсуві вправо втрачається крайній правий біт. На рис. 7.2.2 показана схема 4-розрядного паралельного кільцевого регістру. Входи A, B, C, D вданому приладі є інформаційними.

Рис. 7.2.2. 4-розрядний паралельний кільцевий регістр зсуву

Цю систему можливо спорядити ще однією корисною характеристикою – можливістю кільцевого переміщення інформації, коли дані з входу приладу повертаються на його вхід і не втрачаються. В даному регістрі зсуву використовуються чотири JK-тригери. Треба звернути увагу на зворотній зв’язок виходу тригера TD та входів J і K тригера ТА. Завдяки цьому ланцюгу зворотного зв’язку введена в регістр інформація, яка звично втрачається на виході тригеру TD, буде циркулювати по регістру зсуву. Сигналом очищення регістру (встановлення його виходів в стан 0000) є рівень логічного нуля на вході CLR. Входи паралельного завантаження A, B, C, D пов’язані з входами попереднього встановлення тригерів PRN, що дозволяє встановлювати рівень логічної одиниці на будь-якому виході (A, B, C, D). Якщо на один з цих входів подати логічний 0, то на відповідному виході буде логічна 1. Подача тактових імпульсів на входи CLK всіх JK-тригерів призводить до зсуву інформації в регістрі вправо. З тригеру TD дані передаються в тригер ТА (кільцеве переміщення інформації).

Табл. 7.2.2. Робота 4-розрядного паралельного кільцевого регістру зсуву

Табл. 7.2.2 допомагає зрозуміти принцип роботи паралельного регістру зсуву. При включенні живлення на виходах регістру встановлюється будь-яка двійкова комбінація, така, наприклад як в рядку 1 таблиці 7.2.2. Подача логічного 0 на входи CLR тригерів ініціює очищення регістру (рядок 2). Далі (рядок 3) відбувається завантаження в регістр двійкової комбінації 0100. Послідовні тактові імпульси викликають зсув введеної інформації вправо (рядки 4-8). Треба звернути увагу на рядки 5 і 6: одиниця з крайнього правого тригеру TD переноситься в крайній лівий тригер ТА. В даному випадку можливо говорити про кільцеве переміщення одиниці в регістрі. Далі (рядок 9) заново ініціюється очищення регістру за допомогою входу CLR. Завантажується нова двійкова комбінація 0110 (рядок 10). Подача 5 тактових імпульсів (рядки 11-15) призводить до кільцевого зсуву інформації на 5 позицій вправо. Треба звернути увагу, що для повернення даних в початковий стан потрібно 4 тактових імпульси. Якщо в регістрі зсуву на рис. 2.2 розірвати ланцюг зворотного зв’язку, то ми отримаємо звичайний паралельний регістр зсуву; можливість кільцевого переміщення даних буде виключена.

7.2.3 Програма реалізації регістрів в інтегрованому середовищі MAX+PLUS II Програма для реалізації 4-розрядного послідовного регістру зсуву за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: Title "register1"; Parameters (WIDTH = 4); - встановлення розрядності регістру Assert (WIDTH > 0) - перевірка розрядності регістру на відмінність від 0 Report "Value of WIDTH parameter must be greater then %" WIDTH Severity Error; Subdesign register1 ( D_INPUT, SET, RESET: input = GND; - вхідні сигнали CLK: input; - вхід синхронізації ENABLE: input = VCC; - вхід дозволу роботи Q_OUTPUT: output; - вихідні сигнали ) Variable FF[WIDTH..1]: DFFE; - об'ява змінної FF, що належить до класу DFFE Begin FF[].clk = CLK; FF[].prn =!SET; FF[].clrn =!RESET; FF[].ena = ENABLE; FF[].d = (FF[WIDTH-1..1].q, D_INPUT); Q_OUTPUT = FF[WIDTH].q; End; - Примітка: на часовій діаграммі: - FF - двійкове число на виході регістру Програма для реалізації 4-розрядного паралельного кільцевого регістру зсуву за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: Subdesign register2 Parameters (WIDTH = 4); - встановлення розрядності регістру Assert (WIDTH > 0) - перевірка розрядності тригера (більша від нуля) Report "Value of WIDTH parameter must be greater then %" WIDTH Severity Error; ( I[WIDTH..1]: input = VCC; - вхідні сигнали (дані) CLK: input; RESET: input; O[WIDTH..1]: output; - вихідні сигнали (дані) ) Variable FF[WIDTH..1]: JKFF; - об'ява змінної FF, що належить до класу JKFF Begin FF[WIDTH..1].j = (FF[WIDTH-1..1].q, FF[WIDTH].q); FF[WIDTH..1].k = (!FF[WIDTH-1..1].q,!FF[WIDTH].q); FF[WIDTH..1].clk = CLK; FF[WIDTH..1].clrn =!RESET; FF[WIDTH..1].prn = I[WIDTH..1]; O[WIDTH..1] = FF[WIDTH..1].q; End;

Лічильник віднімання Вище було описано лічильники, що рахують в прямому напрямку (0, 1, 2,...). Однак в деяких цифрових системах з’являється необхідність рахування в зворотному напрямку (9, 8, 7, 6,...). Лічильники, які рахують від більших чисел до менших називають лічильниками віднімання, або лічильниками зворотної дії. Схема асинхронного лічильника віднімання за модулем 8 показано на рис. 7.3.4, відповідна відлікова послідовність чисел наведена в табл. 7.3.2.

Рис. 7.3.4. Логічна схема асинхронного 3-розрядного лічильника віднімання

Табл. 7.3.2. Відлікова послідовність для 3-розрядного лічильника віднімання

Треба звернути увагу на те, що схема лічильника віднімання нагадує схему лічильника прямої дії на рис. 7.3.1. Єдиною відмінністю є спосіб переносу від тригера Т1 до тригера Т2 і від тригера Т2 до тригера Т3. В лічильнику прямої дії синхронізуючий вхід кожного тригера пов’язаний з інверсним виходом Q попереднього тригера. Зауважимо, що в лічильнику відліку перед початком відліку в зворотному напрямку передбачене його попереднє встановлення в стан 111 (деcяткове число 7) за допомогою входу предвстановлення (PRN). Тригер Т3 – двійковий лічильник розряду одиниць (стовпець T1). Тригер Т2 – лічильник розряду двійок (стовпець T2). Тригер Т3 – лічильник розряду четвірок (стовпець T3).

7.3.4 Програми реалізації лічильників в інтегрованому середовищі MAX+PLUS II Програма для реалізації 4-розрядного асинхронного лічильника з крізним переносом за модулем 16 за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: title "counter1"; parameters (WIDTH = 4); - встановлення розрядності лічильника assert (WIDTH > 0) - перевірка розрядності лічильника report "Value of WIDTH parameter must be greater then %" WIDTH severity error; subdesign counter1 ( CLK: input; - імпульси синхронізації (CLK) лічильника RESET: input; - імпульси зкидання (CLRN) тригерів лічильника SET: input; - імпульси предвстановлеення (PRN) тригерів лічильника O [WIDTH..1]: output; - вихід лічильника ) variable TRIGGER [WIDTH..1]: JKFF; begin TRIGGER [WIDTH..1].j = vcc; TRIGGER [WIDTH..1].k = vcc; TRIGGER [WIDTH..1].clrn =!RESET; TRIGGER [WIDTH..1].prn =!SET; TRIGGER [WIDTH].clk =!CLK; TRIGGER [WIDTH-1..1].clk =!TRIGGER [WIDTH..2].q; O [WIDTH..1] = TRIGGER [1..WIDTH].q; end; Програма для реалізації асинхронного лічильника за модулем 10 за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: title "counter2"; parameters (WIDTH = 4); - встановлення розрядності лічильника assert (WIDTH > 0) - перевірка розрядності лічильника report "Value of WIDTH parameter must be greater then %" WIDTH severity error; subdesign counter2 ( CLK: input; - імпульси синхронізації (CLK) лічильника SET: input; - імпульси предвстановлення (PRN) тригерів лічильника O [WIDTH..1]: output; - вихід лічильника ) variable TRIGGER [WIDTH..1]: JKFF; begin TRIGGER [WIDTH..1].j = vcc; TRIGGER [WIDTH..1].k = vcc; TRIGGER [WIDTH..1].prn =!SET; TRIGGER [WIDTH].clk =!CLK; TRIGGER [WIDTH-1..1].clk =!TRIGGER [WIDTH..2].q; TRIGGER [WIDTH..1].clrn = (TRIGGER [3].q!& TRIGGER [1].q); O [WIDTH..1] = TRIGGER [1..WIDTH].q; end; Програма для реалізації 3-розрядного лічильника віднімання за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: title "counter3"; parameters (WIDTH = 3); - встановлення розрядності лічильника assert (WIDTH > 0) - перевірка розрядності лічильника report "Value of WIDTH parameter must be greater then %" WIDTH severity Error; subdesign counter3 ( CLK: input; - імпульси синхронізації (CLK) лічильника RESET: input; - імпульси зкидання (CLRN) тригерів лічильника SET: input; - імпульси предвстановлення (PRN) тригерів лічильника O[WIDTH..1]: output; - вихід лічильника ) variable TRIGGER[WIDTH..1]: JKFF; begin TRIGGER [WIDTH..1].j = vcc; TRIGGER [WIDTH..1].k = vcc; TRIGGER [WIDTH..1].clrn =!RESET; TRIGGER [WIDTH..1].prn =!SET; TRIGGER [WIDTH..1].clk = (CLK,!TRIGGER [WIDTH..2].q); O [WIDTH..1] =!TRIGGER [1..WIDTH].q; end; Програма для реалізації 3-розрядного універсального лічильника за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: title "counter4"; parameters (WIDTH = 3); - встановлення розрядності лічильника assert (WIDTH > 0) - перевірка розрядності лічильника report "Value of WIDTH parameter must be greater then %" WIDTH severity Error; subdesign counter4 ( CLK: input; - імпульси синхронізації (CLK) лічильника SET: input; - імпульси предвстановлення (PRN) тригерів лічильника RESET: input; - імпульси зкидання (CLRN) тригерів лічильника FWC: input; BWC: input; O[WIDTH..1]: output; - вихід лічильника ) variable TRIGGER[WIDTH..1]: JKFF; begin TRIGGER[].j = vcc; TRIGGER[].k = vcc; TRIGGER[].prn =!SET; TRIGGER[].clrn =!RESET; TRIGGER[WIDTH].clk =!CLK; TRIGGER[WIDTH-1..1].clk =!((TRIGGER[WIDTH..2].q &!FWC) &!(!TRIGGER[WIDTH..2].q &!BWC)); O[WIDTH..1] = TRIGGER[1..WIDTH].q; end; - Примітка: - Значення входів, що відповідают вставленню відліку лічильника в - зростаючому напрямку: - FWC = 1; - BWC = 0. - Значення входів, що відповідают вставленню відліку лічильника в - спадаючому напрямку: - FWC = 0; - BWC = 1.

Мультиплексор Мультиплексором називають комбінаційний логічний пристрій, призначений для керування передачею даних від кількох джерел до одного вихідного каналу.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-06; просмотров: 190; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.118.1.232 (0.314 с.) |