Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Результати програмної реалізації лічильників

На рис. 7.3.5 зображено вікно сигнального редактору проекту “counter1”.

Рис 7.3.5. Результати тестування 4-розрядного асинхронного лічильника з крізним переносом за модулем 16

На рис. 7.3.6 зображено вікно сигнального редактору проекту “counter2”.

Рис 7.3.6. Результати тестування асинхронного лічильника за модулем 10

На рис. 7.3.7 зображено вікно сигнального редактору проекту “counter3”.

Рис 7.3.7. Результати тестування 3-розрядного синхронного лічильника

На рис. 7.3.8 зображено вікно сигнального редактору проекту “counter4”.

Рис 7.3.8. Результати тестування 3-розрядного універсального лічильника

Теоретичні відомості про мультиплексори, демультиплексори, шифратори, дешифратори Мультиплексор Мультиплексором називають комбінаційний логічний пристрій, призначений для керування передачею даних від кількох джерел до одного вихідного каналу. Типове використання мультиплексорів – передача даних від кількох рознесених в просторі джерел інформації на вхід приймача. Припустимо, вимірюється температура навколишнього середовища в кількох приміщеннях й результати цих вимірів повинні бути виведені на ЕОМ. При цьому, так як температура змінюється повільно, для отримання достатньої точності зовсім не обов’язково виміряти її постійно. А достатньо мати виміри, проведені через деякі фіксовані проміжки часу. Головне, щоб проміжки між двома вимірами були суттєво менші за сталу часу, що характеризує зміну температури в приміщенні, яке контролюється. Саме цю функцію, тобто підключення різних джерел інформації до одного приймача, за заданою командою, і виконує мультиплексор. Інформацію, рознесену в просторі, він перетворює до вигляду з розділом в часі. Відповідно до визначення, мультиплексор повинен мати один вихід і дві групи входів: інформаційні і адресні. Код, що подається на адресні входи, визначає, який з інформаційних входів в даний момент підключений до вихідного виводу. Оскільки n-розрядний двійковий код може приймати 2n значень, то, якщо число адресних входів мультиплексора дорівнює n, то число його інформаційних входів повинно дорівнювати 2n. Таблиця дійсності, що відображає роботу мультиплексора з двома адресними входами має наступний вигляд (табл. 7.4.1).

Табл. 7.4.1. Таблиця дійсності для мультиплексора з двома адресними входами

В даній таблиці враховано, що мультиплексор зазвичай має додатковий інверсний вихід Функція алгебри логіки, що описує роботу мультиплексора має вид:

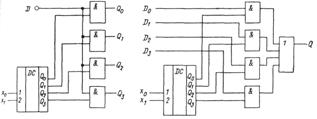

Логічна схема мультиплексора, що відповідає наведеній функції алгебри логіки та умовне позначення мультиплексора на прикладі ІС (інтегральна схема) 555КП7 показані на рис. 7.4.1 а, б.

а) б) Рис. 7.4.1. Логічна схема мультиплексора (а) і його умовне графічне позначення (б)

При передачі інформації від кількох джерел по звичайному каналу з розподілом в часі потрібні не тільки мультиплексори, але й пристрої оберненого призначення, що розподіляють інформацію, отриману з одного каналу поміж кількох приймачів. Таку задачу вирішують демультиплексори. В інтегрованому середовищі MAX+PLUS II за допомогою мови AHDL мультиплексор може бути описаний двома методами: 1) таблицею дійсності; 2) на поведінковому рівні. Описання пристрою за допомогою таблиці дійсності найбільш просте, адже вимагає знання проектувальником лише таблиці дійсності мультиплексора. Об’єм отриманої програми, порівняно з об’ємом програми описання на поведінковому рівні, має значно менший розмір, але архітектура (логічна схема) самого пристрою залишається проектувальнику невідомою. Фахівець обирає метод описання виходячи з технічного завдання, заданого об’єму програми, кількості елементарних вентилів на мікросхемі та власного досвіду. Приклади описання мультиплексора, що має два адресних, чотири інформаційних входи і один вхід дозволу роботи наведено і за допомогою таблиці дійсності, і на поведінковому рівні.

Демультиплексор Демультиплексором називається комбінаційний логічний пристрій, призначений для керування передачею даних від одного джерела інформації до декількох вихідних каналів. Відповідно до визначення, демультиплексор в загальному випадку має один інформаційний вхід, n адресних входів і 2n виходів. Таблиця дійсності, що описує роботу демультиплексора з двома адресними входами і входом дозволу роботи Е, має вид (табл. 7.4.2):

Табл.7.4.2. Таблиця дійсності для демультиплексора з двома адресними входами

Даній таблиці відповідає наступна функція алгебри логіки:

На рис. 7.4.2,а наведена логічна схема демультиплексора, що задовольняє функції алгебри логіки (2), а на рис. 7.4.2,б показано його умовне графічне зображення.

а) б) Рис. 7.4.2. Логічна схема демультиплексора (а) і його умовне графічне позначення (б)

Шифратор Шифратором, або кодером називається комбінаційний логічний пристрій для перетворення чисел з десяткової системи відліку до двійкової. Входам шифратора послідовно присвоюються значення десяткових чисел, тому подача активного логічного сигналу на один з входів сприймається шифратором як подача відповідного десяткового числа. Цей сигнал перетворюється на виході шифратора в двійковий код. Відповідно до сказаного, якщо шифратор має n виходів, то число його входів повинно бути не більше за 2n. Шифратор, що має 2n входів і n виходів, називається повним. Якщо число входів шифратора менше за 2n, то він називається неповним. Розглянемо роботу шифратору на прикладі перетворювача десяткових чисел від 0 до 9 в двійково-десятковий код. Таблиця дійсності, що відповідає даному випадку має вигляд (табл. 7.4.3). Так як число входів даного пристрою менше за 2n = 16, то ми маємо неповний шифратор. Використовуючи таблицю для Q3, Q2, Q1, Q0, стає можливо записати наступні вирази:

Q3 = x8 + x9; Q2 = x4 +x5 + x6 +x7; Q1 = x2 + x3 +x6 + x7; (3) Q0 = x1 + x3 +x5 +x7 +x9.

Табл. 7.4.3. Таблиця дійсності для перетворювача десяткових чисел від 0 до 9 в двійко-десятковий код

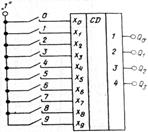

Отримана система (3) характеризує роботу шифратора. Логічна схема пристрою, що відповідає системі (3) показана на рис. 7.4.3. Неважко помітити, що в шифраторі даного типу сигнал, що подається на вхід x0 не використовується. Тому відсутність сигналу на будь-якому з входів x0, x1 трактується схемою як наявність нульового сигналу.

Рис. 7.4.3. Логічна схема шифратору десяткових чисел

Основний напрямок використання шифратора в цифрових системах – введення початкової інформації з клавіатури.

При натисканні будь-якої клавіші на відповідний вхід шифратора подається сигнал “логічна одиниця”, який і перетворюється потім в двійково-десятковий код. Варіант пристрою введення інформації показано на рис. 7.4.4.

Рис. 7.4.4. Пристрій введення інформації з клавіатури

В інтегрованому середовищі MAX+PLUS II за допомогою мови AHDL шифратор може бути описаний двома методами: 3) емульованою, за допомогою оператора CASE, таблицею дійсності; 4) на поведінковому рівні. Описання пристрою, емульованою за допомогою оператора CASE, таблицею дійсності найбільш просте, адже вимагає знання проектувальником лише таблиці дійсності шифратору. Об’єм отриманої програми, порівняно з об’ємом програми описання на поведінковому рівні, має значно менший розмір, але архітектура (логічна схема) самого пристрою залишається проектувальнику невідомою. Фахівець обирає метод описання виходячи з технічного завдання, заданого об’єму програми, кількості елементарних вентилів на мікросхемі та власного досвіду. Приклади описання шифратора 10 на 4 і за допомогою таблиці дійсності, і на поведінковому рівні.

Дешифратор Дешифратором, або декодером називається комбінаційний логічний пристрій для перетворення чисел з двійкової системи відліку до десяткової. Відповідно до визначення дешифратор відноситься до класу перетворювачів коду. Розуміється, що кожному двійковому числу ставиться у відповідність сигнал, що формується на виході пристрою. Таким чином, дешифратор виконує операцію, обернену стосовно шифратора. Якщо число адресних входів дешифратора n пов’язано з числом його виходів m співвідношенням m = 2n, то дешифратор називають повним. В оберненому випадку, якщо m < 2n, дешифратор називають неповним. Поведінку дешифратора описують таблицею дійсності, аналогічно до таблиці дійсності шифратора (дивись систему 3), але в цій таблиці вхідні і вихідні сигнали помінялися місцями. У відповідності до даної таблиці, так як вихідний сигнал дорівнює 1 тільки на одному, єдиному, наборі вхідних змінних, тобто для одної конституєнти одиниці, алгоритм роботи дешифратора описується системою рівнянь виду:

х0 = х1 = х2 =

і так далі, де Qi – значення логічної змінної на і-ому вході пристрою. В загальному випадку система (4) має вид:

хі = (Q3Q2Q1Q0)і, (5)

де, xi – сигнал на і-ому виході шифратора; (Q3Q2Q1Q0)і – конституанта одиниці, що відповідає двійковому коду і-ої десяткової цифри. Неважко помітити, що функція алгебраїчної логіки дешифратора (4) відрізняється від функції алгебраїчної логіки демультиплексора (2) лише наявністю в останній додаткового множника, що відповідає значенню сигналу на інформаційному вході D. Тому при D = 1 демультиплексор функціонує як дешифратор. Обернене перетворення дешифратора в демультиплексор вимагає введення двох допоміжних логічних елементів І, що виконують операцію логічного множення між загальним сигналом інформаційного входу D і відповідним логічним результатом множення адресних сигналів (Q3Q2Q1Q0). Використовуючи дешифратор, можливо побудувати і схему мультиплексора. Для цього схему з рис. 7.4.5,а необхідно доповнити чотирма вихідними логічними елементами АБО (рис. 7.4.5,б).

а) б) Рис. 7.4.5. Реалізація демультиплексора (а) і мультиплексора (б) з використанням дешифратора

При розробці інтегральних схем використовують декілька логічних структур дешифратора. Їх головна відмінність полягає в швидкодії і кількості використаних елементарних логічних елементів. Найбільш швидкодійним і в той же час найбільш складним є дешифратор, що прямо реалізує систему функцій алгебри логіки (4). Такий дешифратор називається одноступінчастим або паралельним. Його структурна схема аналогічна до схеми демультиплексора (дивись рис. 7.4.2) за умови D = 1. Вважаючи, що для реалізації обробки одного вхідного логічного сигналу необхідна деяка умовна одиниця апаратних засобів, число одиниць цих апаратних засобів для n-розрядного дешифратора визначається виразом:

N1 = n2n.

На рис. 7.4.6 наведено умовне графічне зображення дешифратора. Воно відповідає інтегральній схемі двійково-десяткового дешифратора типа 564ИД1. Якщо при проектуванні основною вимогою є простота системного рішення, використовують інші структурні схеми дешифраторів. Однак, спрощення структури досягається за рахунок падіння швидкодії.

Рис. 7.4.6. Умовне графічне позначення дешифратора Мікросхеми дешифраторів часто мають входом дозволу роботи E (вхід стробування). Наявність цього входу дозволяє на основі готових інтегральних схем при необхідності збільшення розрядності вхідного коду створювати структури дешифраторного дерева.

7.4.5 Програми реалізації мультиплексорів, демультиплексорів, шифраторів, дешифраторів в інтегрованому середовищі MAX+PLUS II Програма для реалізації шифратора 10 на 4 (опис таблицею дійсності шифратора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: Subdesign shifrator1 ( XIP[9..0]: input; - вхідні сигнали QOP[3..0]: output; - вихідні сигнали ) Begin Table XIP[] => QOP[]; b"0000000001" => b"0000"; b"0000000010" => b"0001"; b"0000000100" => b"0010"; b"0000001000" => b"0011"; b"0000010000" => b"0100"; b"0000100000" => b"0101"; b"0001000000" => b"0110"; b"0010000000" => b"0111";

b"0100000000" => b"1000"; b"1000000000" => b"1001"; End table; End; Програма для реалізації шифратора 10 на 4 (опис на поведінковому рівні шифратора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: Subdesign shifrator2 ( XIP[9..0]: input; - вхідні сигнали QOP[3..0]: output; - вихідні сигнали ) Begin QOP[3]= XIP[8] + XIP[9]; QOP[2]= XIP[4] + XIP[5] + XIP[6] + XIP[7]; QOP[1]= XIP[2] + XIP[3] + XIP[6] + XIP[7]; QOP[0]= XIP[1] + XIP[3] + XIP[5]+ XIP[7] + XIP[9]; End; Програма для реалізації 3-розрядного дешифратора з інверсними виходами за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: subdesign decipherer1 ( XIP[3..1]: input; - вхідні сигнали QOP[7..0]: output; - вихідні сигнали ) begin case XIP[] is when 0 => QOP = b"11111110"; when 1 => QOP = b"11111101"; when 2 => QOP = b"11111011"; when 3 => QOP = b"11110111"; when 4 => QOP = b"11101111"; when 5 => QOP = b"11011111"; when 6 => QOP = b"10111111"; when 7 => QOP = b"01111111"; end case; end; Програма для реалізації мультиплексора з 2 адресними входами, 4 інформаційними і входом дозволу роботи (опис емульованою таблицею дійсності мультиплексора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: subdesign multiplexer1 ( INFIN[4..1]: input; - інформаційні входи ADRIN[2..1]: input; - адресні входи ENA: input; - вхід дозволу роботи (вхід стробування) Q: output; - вихід мультиплексора ) begin if ENA == 0 then - емуляція таблиці дійсності case ADRIN[2..1] is when 0 => Q = INFIN[1]; when 1 => Q = INFIN[2]; when 2 => Q = INFIN[3]; when 3 => Q = INFIN[4]; end case; end if; end; - Примітка: компілятор AHDL не дозволяє присутності в - таблиці дійсності змінних (параметрів), навіть якщо - змінним (параметрам) раніше вже присвоєне фіксоване - значення. Тому за логікою таблиці дійсності, на основі - оператору вибору CASE, формується послідовність перевірки - значень вхідних сигналів системи. Програма для реалізації мультиплексора з 2 адресними входами, 4 інформаційними і входом дозволу роботи (опис на поведінковому рівні мультиплексора) за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: subdesign multiplexer2 ( INFIN[4..1]: input; - інформаційні входи ADRIN[2..1]: input; - адресні входи ENA: input; - вхід дозволу роботи (вхід стробування) Q: output; - вихід мультиплексора ) begin Q = INFIN[1] &!ADRIN[2] &!ADRIN[1] &!ENA # INFIN[2] &!ADRIN[2] & ADRIN[1] &!ENA # INFIN[3] & ADRIN[2] &!ADRIN[1] &!ENA # INFIN[4] & ADRIN[2] & ADRIN[1] &!ENA; end; - Примітка: Q - функція алгебри логіки, що описує роботу мультиплексора. Програма для реалізації демультиплексора з 3 адресними входами, 1 інформаційним і входом дозволу роботи за допомогою мови AHDL в інтегрованому середовищі MAX+PLUS II має наступний вигляд: subdesign demultiplexer1 ( ADRIN[3..1]: input; - адресний вхід INFIN: input; - інформаційний вхід ENA: input; - вхід дозволу роботи (вхід стробування) Q[7..0]: output; - виходи демультиплексора ) begin if ENA == 0 then case ADRIN[] is when 0 => Q[0] = INFIN; when 1 => Q[1] = INFIN; when 2 => Q[2] = INFIN; when 3 => Q[3] = INFIN; when 4 => Q[4] = INFIN; when 5 => Q[5] = INFIN; when 6 => Q[6] = INFIN; when 7 => Q[7] = INFIN; end case; end if; end;

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-06; просмотров: 194; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.186.173 (0.154 с.) |

і вхід дозволу роботи Е (в програмах мовою AHDL вхід дозволу роботи, по прикладу примітивів тригерів, має ім’я ENA). Якщо на вхід дозволу роботи Е подається активний логічний сигнал (Е=1), вихідний сигнал мультиплексора постійний і не залежить від його вхідних сигналів.

і вхід дозволу роботи Е (в програмах мовою AHDL вхід дозволу роботи, по прикладу примітивів тригерів, має ім’я ENA). Якщо на вхід дозволу роботи Е подається активний логічний сигнал (Е=1), вихідний сигнал мультиплексора постійний і не залежить від його вхідних сигналів. . (1)

. (1)

(2)

(2)

;

; ; (4)

; (4) ;

;