Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

VI. Последовательностные цифровые устройстваСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Определение. Цифровое устройстве называется после-довательностным, если его выходные сигналы Y зависят не только от текущих значений входных сигналов X, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. В ПЦУ предыстория поступления последовательности входных сигналов обязательно фиксируется с помощью специальных запоминающих элементов или элементов памяти. Поэтому говорят, что ПЦУ обладают памятью. Элемент памяти помимо входных и выходных сигналов характеризуется состоянием, которое может изменяться в дискретные моменты времени под воздействием сигналов на его входе. Простейший элемент памяти может принимать одно из двух состояний, например 0 или 1. Это состояние может сохраняться сколь угодно долге или по крайней мере в течение некоторого промежутка времени. ПЦУ называют также цифровыми автоматами, конечными автоматами или автоматами с памятью. Структура ПЦУ представлена на рис. 31. ПЦУ разделяется условно на комбинационное цифровое устройство (КЦУ) и запоминающее устройство (ЗУ), представляющее собой совокупность простейших элементов памяти Т1, T2,..., Tk, на которые воздействуют сигналы U=[u1, u2,..., uk]. Под воздействием сигнала ui элемент Ti может перейти в одно из двух состояний: 0 или 1. Состояние элемента Ti; отображается сигналом Zi. Совокупность сигналов Z=[z1, z2,..., zk] отображает состояние ПЦУ. Если в ПЦУ содержится k простейших элементов памяти, то общее число состояний ПЦУ равно 2k.

Рис. 31.

Комбинационное цифровое устройство, входящее в состав ПЦУ, представляет собой устройство, схема которого описывается булевыми функциями: Y = F(X, Z), U = Н (X, Z). ПЦУ работает под воздействием входных сигналов X, которые поступают в моменты времени t = 0, 1, 2,... В момент времени t=0 ПЦУ находится в начальном состоянии. При этом Z(t) = [z1(t), z2(t)...,zk(t)] принимает некоторое начальное значение Z(0) = [z1(0), z2(0),..., zk(0)]. При поступлении сигналов X(t) в ПЦУ формируются выходные сигналы Y(t) и сигналы U(t), воздействующие на запоминающие элементы. В результате ПЦУ переходит в некоторое состояние Z(t), и тем самым фиксируется воздействие входных сигналов X(t) в момент времени t. Темп работы ПЦУ определяется темпом поступления входных сигналов. Совокупность правил, определяющих последовательность переключения состояний Z(t) и последовательность выходных сигналов Y{t} в зависимости от последовательности входных сигналов X(t}, принято называть законом функционирования ПЦУ. Также как и при изучении КЦУ, рассмотрим типовые ПЦУ, к которым относят триггеры, регистры и счетчики.

ТРИГГЕРЫ

Основные определения. Триггером называют устройство, которое может находиться в одном из двух устойчивых состояний и переходить из одного состояния в другое под воздействием входного сигнала. Состояние триггера определяется по выходному сигналу. Триггер является базовым элементом ПЦУ. В нем может. храниться либо 0 либо 1. Для удобства использования в схемах ПЦУ триггеры имеют два выхода:

1) прямой Q (выход 1); 2) инверсный Q (выход 0). Состоянию триггера 1 соответствует на выходе Q высокий уровень сигнала (1). Состоянию триггера 0 соответствует на выходе Q низкий уровень сигнала (0). Входы триггера делятся на информационные и вспомогательные (управляющие). Сигналы, поступающие на информационные входы, управляют состоянием триггера. Сигналы на вспомогательных входах используются для предварительной установки триггера в требуемое состояние и синхронизации. Вспомогательные входы могут использоваться и в качестве информационных. Число входов триггера зависит от его структуры и назначения. Информационные входы триггера принято обозначать буквами S, R, J, К, D, Т, а управляющие входы С, V. Для триггера имеется стандартное обозначение (рис. 32). Здесь S и R

являются информационными входами, Q и Q — выходами, Т обозначает триггер. Инверсный выход Q отмечен кружком. Способ построения триггера с использованием схемы с обратной связью с выхода на вход является основным. Используя его, можно строить разнообразные схемы триггеров.

Рис. 32.

Классификация триггеров. Триггеры можно классифицировать по способу приема информации, по принципу построения, по функциональным возможностям. По способу приема информации триггеры подразделяются на асинхронные и синхронные. Асинхронные триггеры воспринимают информационные сигналы и реагируют на них в момент появления на входах триггера. Синхронные триггеры, реагируют на информационные сигналы при наличии разрешающего сигнала на специальном управляющем входе С, называемом входом синхронизации. Синхронные триггеры подразделяются на триггеры со статическим и динамическим управлением по входу С. Триггеры со статическим управлением воспринимают информационные сигналы при подаче на вход С уровня 1 (прямой С-вход) или 0 (инверсный С-вход). Триггеры с динамическим управлением воспринимают информационные сигналы при изменении сигнала на С - входе от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). По принципу построения триггеры со статическим управлением можно разделить на одноступенчатые и двухступенчатые. Одноступенчатые триггеры характеризуются наличием одной ступени запоминания информации. В двухступенчатых триггерах имеются две ступени запоминания информации. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. По функциональным возможностям различаются: триггер с раздельной установкой состояний 0 и 1 (RS-триггер); триггер с приемом информации по одному входу D(D-триггер или триггер задержки); триггер со счетным входом Т (T-триггер); универсальный триггер с информационными входами J и K (JK-триггер). Триггеры характеризуются быстродействием, чувствительностью, потребляемой мощностью, помехоустойчивостью, функциональными возможностями. Быстродействие определяется максимальной частотой переключения состояний триггера и достигает сотен мегагерц. Чувствительность триггера определяется наименьшим напряжением на входе (пороговым напряжением), при котором происходит переключение. Помехоустойчивость характеризует способность триггера нормально работать в условиях помех. Функциональные возможности триггера характеризуются числом входных сигналов. Для обозначения функциональных возможностей триггеров в интегральном исполнении используется следующая маркировка: TR—RS-триггер; TB—триггер; ТМ — D-триггер. Для полного описания триггера достаточно задать его структурную схему из базовых логических элементов и закон функционирования. В качестве базовых логических элементов можно использовать элементы ИЛИ-НЕ, И-НЕ. Поскольку триггер является простейшим ПЦУ, закон функционирования может быть задан таблицей переходов, в которой входные сигналы в момент их изменения и состояние триггера обозначены индексом t, а после переключения—индексом t+1 Рассмотрим триггеры основных видов.

АСИНХРОННЫЙ RS-ТРИГГЕР С ПРЯМЫМИ ВХОДАМИ Эти триггеры имеют два информационных входа S и R, используемые для установки соответственно 1 и 0, а также два выхода: прямой и инверсный. RS-триггер построен на двух логических элементах ИЛИ-НЕ, соединенных в контур (рис. 31 а). Графическое обозначение RS-триггера приведено на рис.31, б, закон функционирования может быть описан табл. 7. Таблица 7.

Как следует из таблицы, при комбинации сигналов S=1, R=0 триггер переходит в состояние 1 независимо от предыдущего состояния. При наборе сигналов S=O, R=1 триггер устанавливается в состояние 0. Комбинация сигналов S=0, R=0 не изменяет состояния триггера, т. е. состояние триггера в момент t+1 равно состоянию триггера в момент t. Набор сигналов S=1, R=1 является запрещенным, так как он приводит к нарушению работы триггера и неопределенности его состояния. В RS-триггерах с прямыми входами управляющим воздействием обладают единичные уровни сигналов. Сигналы, которые приводят к переключению элемента, называются активными. Для элементов ИЛИ-НЕ, используемых для построения RS-триггера, активным сигналом является уровень 1. Аналитическое выражение для описания функционирования RS-триггера имеет вид:

Qt+1 = St + Rt * Qt.

Из полученного выражения видно, что RS-триггер устанавливается в состояние 1 при воздействии входного уровня S=1 либо остается в состоянии 1, если R=0 и триггер был в состоянии Q=1.

Асинхронный.RS-триггер с инверсными входами. Триггеры такого типа строятся на логических элементах И-НЕ. В этом случае уровень 0 является активным входным сигналом, а уровень 1 — пассивным. Информационные входы и соответствующие сигналы таких триггеров

принято обозначать как инверсные (S, R). В этом случае триггер с инверсными входами будет описываться той же таблицей, что и триггер с прямыми входами. Входные сигналы S=1, R=1 будут активными, как в триггере с прямыми входами. Схема RS-триггера с инверсными входами приведена на рис. 33,а, условное графическое обозначение такого триггера дано на рис. 33,б.

а) б) Рис. 33.

Закон функционирования RS-триггера на элементах И-НЕ описывается табл. 8, из которой следует, что комбинация S = R = 0 является запрещенной, а набор S = R = 0 — нейтральным. Следовательно, если нулевые сигналы на обоих входах триггера на элементах ИЛИ-НЕ составляют нейтральную комбинацию, то для триггера на элементах И-НЕ они запрещены. Эти особенности следует учитывать при использовании в ПЦУ триггеров на логических элементах разных типов. Таблица 8.

Быстродействие асинхронного RS-триггера определяется задержкой установки его состояния tТ, равной сумме задержек передачи сигнала через цепочку логических элементов с задержкой tЭ в каждом. В данном случае TT = 2 * tЭ.

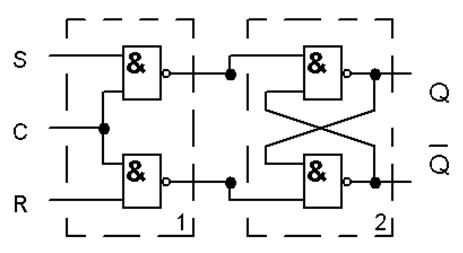

СИНХРОННЫЙ RS-ТРИГГЕР СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ Синхронный RS-триггер отличается от асинхронного наличием С-входа, на который поступают синхронизирующие (тактовые) сигналы. Синхронный триггер состоит из асинхронного RS-триггера и комбинационного цифрового устройства (рис. 34). Как видно из этого рисунка, синхронный триггер построен из элементов И-НЕ. Схема 1 представляет собой КЦУ с тремя входами S, С, R и двумя выходами. Схема 1 состоит из двух логических схем И-НЕ. Схема 2 представляет собой асинхронный RS-триггер на элементах И-НЕ. При С=0 входные логические элементы схемы КЦУ блокированы. Их выходы принимают значения 1 и не зависят от входных сигналов S и R.

Рис. 34.

Для асинхронного RS-триггера на элементах И-НЕ набор из единичных сигналов является нейтральным. Триггер будет сохранять свое состояние. При С=1 входные логические элементы схемы КЦУ открыты для передачи информационных сигналов R и S на входы асинхронного RS-триггера. Следовательно, синхронный триггер при наличии разрешающего сигнала будет работать по правилам для асинхронного триггера. Закон функционирования синхронного RS-триггера на элементах И-НЕ может быть задан табл. 9. Из нее можно получить аналитическое выражение, описывающее работу синхронного RS-триггера:

Qt+1 = Qt * (Rt + Ct) + Ct * St. Легко увидеть, что синхронный RS-триггер принимает состояние 1, если на входы С и S поступают уровни 1, или сохраняет единичное состояние при отсутствии единичных сигналов на входе С или R. Таблица 9.

Условное графическое обозначение синхронного RS - триггера на элементах И-НЕ приведено на рис. 35, Синхронные RS-триггеры строятся и на логических элементах ИЛИ-НЕ, И-ИЛИ-НЕ, а также на их сочетаниях. Общее время установления состояния триггера tт равно сумме задержек передачи сигнала через цепочку из трех логических элементов с задержкой tэ в каждом: tт = 3 * tэ.

Рис. 35.

При этом длительность сигнала tс на входе С должна превышать время переключения tт: Tс ≥ tт = 3 * tэ. Длительность паузы tп между двумя сигналами на входе С должна быть достаточной для переключения входных элементов в КЦУ. Следовательно, минимальный период повторения синхронизирующих сигналов на входе С равен 4 * tэ, а наибольшая частота F = 1/ (4*tэ).

УНИВЕРСАЛЬНЫЙ JK-ТРИГГЕР Универсальный JK-тригггер, схема которого приведена на рис. 36, а, представляет собой двухступенчатый синхронный триггер. Как видно из рисунка, JK-триггер состоит из двух асинхронных RS-триггеров с инверсными входами и двух КЦУ, каждое из которых содержит две схемы И-НЕ с тремя входами каждая.

Рис. 36.

Закон функционирования JK-триггера задается табл. 10. JK-триггер отличается от синхронного RS-триггера тем, что не имеет запрещенных комбинаций сигналов на входах J и К. Кроме того, при J=1 и K=1 триггер изменяет свое состояние на противоположное, т. е. работает как триггер со счетным входом (T-триггер). Таблица 10.

При С=0 входы J и К заблокированы и, следовательно, оказываются заблокированными входы S и R ведущего триггера 1. При С=1 в соответствии с информационными сигналами на входах J и К. устанавливается состояние ведущего триггера. При этом на входы S и R ведомого триггера 2 поступают сигналы, при которых его предыдущее состояние сохраняется. При С=0, когда входы триггера 1 закрыты для входной информации, входы триггера 2 открываются и состояние ведущего триггера воспринимается ведомым триггером. Графическое обозначение JK-триггера представлено на рис. 36, б. Одним из широко используемых вариантов построения является схема JK-триггера с входной логикой (рис. 37, а). Условное обозначение триггера дано на рис. 37, б. При С=1 вторая ступень блокирована, а информационные сигналы устанавливают состояние первой ступени. При сигнале С=0 вторая ступень воспринимает состояние первой. Требуемое начальное состояние триггера устанавливается с помощью сигналов, подаваемых на входы RS-триггеров первой и второй ступени. В схеме триггера имеется по три конъюнктивно связанных входа J и K. Другими словами, в структурную схему триггера встроены логические элементы. Их можно использовать для построения сложных схем.

Рис. 37. Т-ТРИГГЕР Т-триггеры, или триггеры со счетным входом, могут быть получены из JK-триггера при соединении обоих информационных входов J и К и подаче на них уровня 1 (рис. 38, а). Функционирование T-триггера описывается табл. 11. В качестве счетного входа T используется вход С. При подаче сигнала на вход T-триггер будет переключаться в состояние, противоположное предыдущему. JK-триггер в таком режиме выполняет функцию T-триггера. Следует заметить, что уровень 1 для входов J и К (входов элементов И-НЕ) является пассивным сигналом. Поэтому для получения T-триггера из JK-триггера можно не предусматривать входы J и К в схеме (рис. 38, б). Разновидностью Т-триггера является V-триггер, в котором вход V является управляющим. При V=1 V-триггер превращается в T-триггер. При V=0 V-триггер сохраняет свое состояние неизменным (рис. 38, в).

а) б) в) Рис. 38.

Таблица 11.

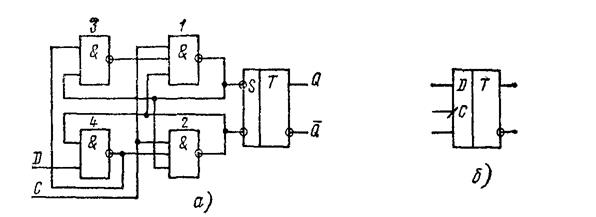

D-ТРИГГЕР D-триггер, или триггер задержки, имеет один информационный вход (D-вход) и вход для синхронизации С. Основное назначение D-триггера — задержка сигнала, поданного на вход D. D-триггер может быть получен из JK-триггера соединением входа J с входом К через инвертор НЕ. Полученный таким образом вход будет называться D-входом. Схема D-триггера представлена на рис. 39, а. Условное обозначение D-триггера приведено на рис. 39, б. Функционирование D-триггера описывается табл. 12. Под действием синхросигнала С информация, поступающая на вход D, принимается в триггер, но на выходе Q появляется с задержкой на один такт.

а) б) Рис. 39. Таблица 12.

СИНХРОННЫЙ ТРИГГЕР С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ Синхронный триггер с динамическим управлением по входу С воспринимает информацию для изменения состояния лишь тогда, когда на С-входе совершается переход с уровня 0 на уровень 1 либо наоборот. Для получения RS-триггера с динамическим входом достаточно построить схему, показанную на рис. 40.

Рис. 40. Если при С=0 на информационные входы поступили какие-либо уровни S и R, то при смене уровня на входе С с 0 на 1 на выходе элемента 1 образуется 0, который поступает на вход элемента 3 и обеспечивает на его выходе уровень 1 независимо от последующих значений уровня на входе S. Вход S логически отключается и никакие изменения уровней на входах S и R триггер не воспринимает, пока не произойдет на входе С переход с уровня 0 на уровень 1. Аналогично можно построить схему RS-триггера с динамическим входом на элементах ИЛИ-НЕ (рис. 41, а). Здесь информация воспринимается триггером со входов S и R при смене уровней С=1 на С=0. Условное изображение такого триггера представлено на рис. 41, б.

Рис. 41.

Схема D-триггера с динамическим входом приведена на рис. 42, а, его условное обозначение дано на рис. 42, б. Прием в триггер информации со входа D происходит в момент смены на входе С уровня 0 на уровень 1.

Рис. 42.

Схема JK-триггера с динамическим входом приведена на рис. 43, а, а его условное обозначение — на рис. 43, б. Переключение триггера из состояния Qt=1 в состояние Qt+1= 0 происходит при K=1 и Qt=1, т. е. при K * Qt = 1. В остальных случаях сохраняется ранее установленное состояние Qt+1 = Qt. Для получения схемы JK-триггера из схемы RS-триггера необходимо на входах S и R асинхронного RS-триггера обеспечивать уровни S = J * Qt и R = K * Qt. Заменяя обозначения входов S на J, R на К и вводя обратные связи с выходов RS-триггера на входы элементов 1 и 2, получаем схему JK-триггера с динамическим входом.

Рис. 43.

РЕГИСТРЫ

Определение. Регистром называется последовательностное цифровое устройство, используемое для хранения и выполнения логических преобразований над n-разрядным двоичным словом. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано некоторое КЦУ, с помощью которого обеспечивается выполнение логических операций или микроопераций над n-разрядными словами в ПЦУ. В регистре могут выполняться следующие микрооперации: прием слова из другого ПЦУ, передача слова из регистра в другое ПЦУ, поразрядные логические операции, сдвиг слова влево или вправо на заданное число разрядов, преобразование последовательного кода слова в параллельный и обратно, установка регистра в начальное состояние («сброс»). Схемы выполнения микроопераций реализуется с помощью КЦУ. Схема регистра для хранения n-разрядного двоичного слова приведена на рис. 44, а. Регистр S состоит из n триггеров. Состояние регистра определяется состояниями триггеров. Оно представляется набором выходных сигналов в парафазном или однофазном коде. На регистр S может быть подано для хранения двоичное n-разрядное слово X= xn, xn-1,…, x1 с помощью совокупности входных сигналов в парафазном или однофазном коде. Если на входы поступают сигналы xi, равные 0 или 1, то триггеры регистра S устанавливаются в состояния в соответствии со значениями переменных xi. Триггеры регистра сохраняют значение S=X до прихода новых входных сигналов. В регистре S(n) каждый i-й элемент (триггер) соответствует двоичной переменной Si и является i-м разрядом регистра S. Число разрядов в регистре определяет его длину.

Рис. 44.

Используемое для регистров условное обозначение дано на рис. 44, б: указываются наименование регистра (S), старший (n) и младший (1) разряды. Входные цепи регистра принято называть входной шиной Х(n), а выходные—выходной шиной S(n). Состояние n-разрядного регистра отображается n-разрядным двоичным словом. Число состояний n-разрядного регистра S равно 2n. Если регистр используется для хранения чисел, то каждому состоянию регистра может быть поставлено в соответствие одно из целых чисел в диапазоне 0... (2n -1). Состояние регистра представляется целым числом в двоичной системе счисления. Для сокращения записи состояния регистра можно использовать восьмеричную и шестнадцатеричную формы представления двоичных чисел. Состояние регистра можно представить не только в двоичном алфавите, но и в любом другом. В частности, широко используется символьное представление с помощью задания символа в виде набора восьми двоичных разрядов, получившего название байт. Регистр в этом случае разбивается на 8-разрядные подрегистры. Вместо двоичного алфавита, состоящего из двух символов 0 и 1, можно использовать алфавит из 256 символов, в который могут входить буквы русского и латинского алфавитов, цифры, различные символы. Регистры играют важную роль при построении сложных цифровых устройств. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом с помощью соответствующих схем КЦУ. Анализ схемы регистра позволяет отметить характерную ее особенность— однородность (регулярность) структуры. Регистр состоит из однотипных элементов (триггеров), которые регулярно размещены друг относительно друга. Однородность элементов с регулярным размещением их в регистре позволяет существенно упростить процессы изготовления, контроля, эксплуатации. Упрощаются также описание и изучение регистра, Регистр можно описать совокупностью однотипных автоматов. Достаточно задать автоматное описание для одного элемента регистра и указать число элементов. Регулярность схемы регистра позволяет прийти к выводу о возможности построения регулярных схем КЦУ для выполнения микроопераций на множестве однотипных элементов. Это дает возможность довольно просто осуществлять синтез схемы КЦУ, сводя его к синтезу многократно повторяющейся схемы КЦУ для одного разряда регистра и схемы, обеспечивающей взаимодействие (при необходимости) двух соседних разрядов. Такой подход позволяет свести сложное описание КЦУ в виде совокупности булевых функций от n переменных к простому описанию КЦУ. При этом КЦУ можно представить в виде повторяющегося n раз набора булевых функций от конечного числа m переменных, где m≤n. В зависимости от типа выполняемых в регистре микроопераций различаются следующие типы регистров: с параллельным приемом и выдачей информации; с последовательным приемом и выдачей информации; с последовательным приемом и параллельной выдачей; с параллельным приемом и последовательной выдачей информации. В зависимости от числа входных и выходных каналов регистры делятся на однофазные (сигналы передаются по одному каналу) и парафазные (передача сигналов по двум каналам). Парафазные регистры реализуются на RS-триггерах, а однофазные—на D-триггерах. Регистры характеризуются числом разрядов и быстродействием, определяемым максимальной тактовой частотой приема, передачи и сдвига информации.

РЕГИСТР ПАМЯТИ Регистр с параллельным приемом и выдачей информации называется регистром памяти. В качестве элементов регистра памяти используются синхронные RS-триггеры при парафазных входных сигналах (рис. 45) или D-триггеры при однофазных входных сигналах (рис. 46). Предварительная установка регистра в нулевое состояние осуществляется посылкой сигнала «Установить О» на асинхронные входы сброса триггеров. Изменение информации в регистре происходит после изменения сигналов на входах Х при поступлении сигнала на вход синхронизации С.

РЕГИСТРЫ СДВИГА Регистры с последовательным приемом или выдачей информации получили название регистров сдвига. В регистре сдвига вправо первый разряд вводимого числа x1 подается на вход одного, крайнего слева, разряда регистра Sn и вводится в него при поступлении первого сигнала синхронизации С. С приходом следующего сигнала синхронизации значение хi с выхода разряда Sn вводится в разряд Sn-1 а в разряд Sn поступает х2. В каждом такте производится сдвиг поступающей информации на один разряд вправо. После n сигналов синхронизации весь регистр оказывается заполненным разрядами числа X, и первый разряд числа x1 появится на выходе S1 Если подать последовательность из n сигналов синхронизации и на вход разряда Sn податьх=0, то из регистра будет выводиться число Х через выход S1 и в конце вывода регистр будет освобожден от хранения числа X. Регистры сдвига реализуются на D-триггерах (рис. 47) или RS-триггерах (рис. 48). В последней схеме для ввода информации в первый разряд включается схема инвертора. Для параллельного вывода информации из регистра сдвига необходимо все выходы разрядов регистра сдвига подключить к различным полюсам Sn, Sn-1,..., S1. Для реализации регистров сдвига применяются также триггеры с динамическим управлением по входу С. Применение таких триггеров гарантирует нормальную работу регистра сдвига. Схема регистра сдвига влево на D - триггерах с динамическим управлением представлена на рис. 49.

Рис. 47.

Рис. 48.

Рис. 49.

Комбинируя схемы сдвига вправо и влево и используя управляющие сигналы, можно построить регистр сдвига в обоих направлениях. Такой регистр называется реверсивным (рис. 50). При подаче разрешающего сигнала на управляющий вход V1 включается схема сдвига вправо. Реверсивный регистр при этом превращается в регистр сдвига вправо. При подаче разрешающего сигнала на управляющий вход V2 включается схема сдвига влево. Реверсивный регистр превращается в регистр сдвига влево.

Рис. 50. В регистрах сдвига влево и вправо разряды двоичного кода выходят за пределы разрядности регистра. Если соединить выход крайнего правого разряда регистра со входом крайнего левого разряда, то получится схему кольцевого (циклического) регистра сдвига. Реверсивные регистры можно использовать для построения стековых регистров, имеющих единственный общий вход и выход. Такие регистры работают по принципу «первый вошел — последний вышел». Стековые регистры называются также регистрами магазинного типа. Возможно также совмещение в одной схеме регистра памяти и регистра сдвига.

СЧЕТЧИКИ

Общие сведения. Последовательностное цифровое устройство, обеспечивающее хранение слова информации и выполнение над ним микрооперации счета, называется счетчиком. Микрооперация счета заключается в изменении значения числа С в счетчике на ±1. Счетчик, в котором выполняется микрооперация счета С=С+1, называется суммирующим, а счетчик, реализующий микрооперацию С=С - 1— вычитающим. Счетчик называется реверсивным, если реализуются обе микрооперации. Основным параметром счетчика является модуль счета Кс, определяемый максимальным числом единичных сигналов, которое может быть сосчитано счетчиком. Счетчик, содержащий n двоичных разрядов, может находиться в состояниях 0,1,2,..,, 2n—1. При поступлении на вход суммирующего счетчика 2n-й единицы он переходит из состояния 2n-1 в состояние 0. Таким образом, n-разрядный суммирующий двоичный счетчик имеет модуль счета Кс=2n . Счетчики характеризуются также быстродействием, которое определяется допустимой частотой входных сигналов и временем установки состояния счетчика. Счетчики обычно реализуются на T-триггерах. Однако для их построения могут применяться не только триггеры со счетным входом, но и D-триггеры, JK-триггеры. Счетчики можно классифицировать по нескольким признакам. В зависимости от направления счета различаются суммирующие (с прямым счетом), вычитающие (с обратным счетом) и реверсивные (с прямым и обратным счетом). По способу организации схемы переноса различаются счетчики с последовательным, параллельным, параллельно-последовательным переносом. В зависимости от наличия синхронизации различаются синхронные и асинхронные счетчики. При маркировке для обозначения счетчика используются буквы ИЕ. Конструктивно счетчики выполняются в виде совокупности интегральных схем — триггеров, соединенных соответствующим образом, или в виде одной интегральной схемы, содержащей многоразрядный счетчик.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-09-20; просмотров: 717; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.96 (0.015 с.) |

St

St

Rt

Rt

Qt

Qt

Qt

Qt