Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Состав электронно-вычислительных машин. Структурная схема. Назначение узлов и блоков эвм. Характеристики эвм.Содержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Архитектура ЭВМ Теоретические вопросы: Вопрос № 1 Состав электронно-вычислительных машин. Структурная схема. Назначение узлов и блоков ЭВМ. Характеристики ЭВМ.

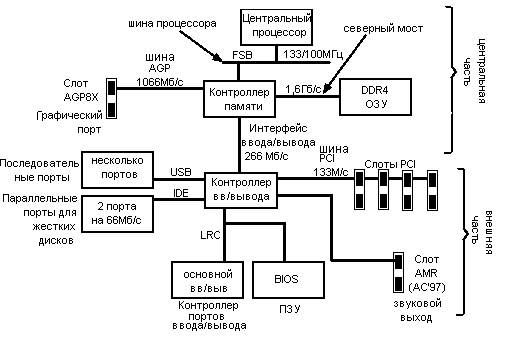

Электронно-вычислительная машина состоит из многих частей. Самые важные (без них компьютер не получится) это: процессор, оперативная память, ПЗУ (BIOS), ВЗУ (жёсткий диск). Также не маловажны устройства ввода/вывода (клавиатура, монитор, принтер и др.). Все эти выше упомянутые устройства (элементы) крепятся или подключаются к материнской плате, на которой имеются специальные (PS\2,COM,LPT, слоты для процессора и ОЗУ) или универсальные выводы (USB, слоты PCI). Информация передаётся на выводы через контроллер ввода/вывода, который контролирует потоки информации. С ним же соединён BIOS, который хранит все настройки машины. На этот контроллер информация приходит по шине (интерфейсу) ввода/вывода, которая подключена к контроллеру памяти. Интерфейс вв/выв соединяет центральную часть машины с внешней. К контроллеру памяти подключены основные части машины: ОЗУ, графический порт и через шину процессора подключен центральный процессор.

Рисунок 1. Структурная схема современной ЭВМ.

ЭВМ характеризуется различными параметрами, такие как: · объём внутренней памяти (байты, регистры) – влияет на производительность и быстродействие машины · объём оперативной памяти (байты, Кбайты…) – влияет на производительность и быстродействие машины, на разрядность шины адреса. · количество способов адресации · количество выполняемых операций – влияет на способность выполнять больше операций · пропускная способность (разрядность) различных шин – влияет на производительность и быстродействие машины · тактовая частота процессора – влияет на производительность и быстродействие машины

Вопрос № 2 Интерфейсы ПЭВМ IBM классификация интерфейсов. Дать определение шин. Охарактеризовать шины в зависимости от их назначения, разрядности и направленности. Шина – канал связи, по которому внутри ПК передаётся информация. В ЭВМ различают несколько основных типов шин: · Шина процессора · Шина памяти · Шина ввода/вывода – основная системная шина · Локальная шина Шина процессора используется для передачи информации между микропроцессором и Кэш-памятью. Шина работает на той же тактовой частоте, что и микропроцессор. Для определения скорости передачи данных по шине процессора надо умножить ширину (разрядность) на тактовую частоту шины (она равна тактовой частоте микропроцессора). Например: 64 МГц * 64 бит = 4224 Мбит/с, 4224Мбит/с: 8 = 528 Мбайт/с. Эта скорость также называется полосой пропускаемости шины. Примеры шин процессора в различных типах ЭВМ: В ЭВМ с 486-ым микропроцессором шина процессора содержит 32 линии адреса, 32 линии данных и несколько линий управления. В ПК с микропроцессором Pentium – 64 линии данных, 32 линии адреса и соответствующее количество линий управления. Шина памяти предназначена для передачи информации между оперативной памятью и микропроцессором. Для её построения используют специализированные микросхемы, осуществляющие передачу информации между микросхемами МП и ОП. Информация по этой шине передаётся с меньшей скоростью, чем по шине процессора, так как микросхемы памяти не могут записывать и воспроизводить информацию с такой скоростью как МП. Шина ввода/вывода предназначена для передачи информации между центральной частью (МП, ОЗУ…) и внешней частью ЭВМ (внешние уст-ва). Эта шина «медленней», чем предыдущие две. Это объясняется тем, что внешние устройства содержат механические узлы, значительно снижающие их быстродействие. Управление процессом обмена данными по шине ввода-вывода осуществляет периферийный процессор (контроллер) ввода-вывода. Примеры типов шин вв/выв: ISA, EISA…PCI. Локальная шина предназначена для передачи информации между ЭВМ и каким-то одним типом периферийного устройства. Например: под видеокарту на материнской плате используют только один тип интерфейса и слот, в который кроме видеокарты больше ничего нельзя вставить. Этот интерфейс локальный и имеет своё название AGP 8х. Вопрос № 3 Классификация и характеристики запоминающих устройств ЭВМ. Внутренняя, внешняя и постоянная память. Иерархическая структура запоминающих устройств. Пояснить принцип работы запоминающих устройств в зависимости от назначения. В ЭВМ представлены несколько видов ЗУ: внутренняя, оперативная, внешняя и постоянная память. Внутренняя память самая быстродействующая, объём гораздо меньше, чем объёмы других ЗУ. В современных ПК внутренняя память является частью микропроцессора и называется Кэш-памятью. Внутренняя память энергозависима, т.е. после отключения питания память очищается. Данный вид ЗУ в процессе работы ЭВМ хранит наиболее используемые части программы. Оперативная память менее быстродействующая, чем КЭШ. Объёмы данного вида ЗУ в несколько раз больше, чем объёмы КЭШа. ОП способна хранить целиком всю программу (если размер программы «умещается» в размер ОП). Также как и КЭШ энергозависима. Является отдельной микросхемой, которая вставляется специальный слот на материнской плате. Внешняя память ещё менее быстродействующая, чем остальные. В отличие от других типов ЗУ энергонезависима, т.е. хранит информацию после отключения питания. Внешними называются запоминающие устройства не входящие в состав центральной части ЭВМ (информационной системы). К ним относятся накопители информации и некоторые устройства чтения с машинных носителей (CD-ROM).В большинстве случаев носитель информации является сменным, что позволяет накапливать информацию в неограниченном объеме. Во всех случаях запись и чтение осуществляются на движущийся носитель (кроме Флэш-памяти). Постоянная память также энергонезависима. Память только для чтения! В современных ЭВМ постоянной памятью является BIOS, которая хранит программу загрузчика ОС, а также все настройки системы.

Вопрос № 4 Рисунок 2. Структурная схема. ШДЦП

Назначение узлов и блоков Узел ЦП включает МП, который управляет работой всех узлов ПЭВМ, обеспечивает чтение информации из ОП, обработку записи информации и записи результата в память. В него входит схема синхронизации, постоянная память и схема управления режимами работы ПЭВМ. Узел ОП объединяет схему управления доступом к памяти и ОЗУ ёмкостью 128кБ. Узел дисплейный контроллер (ДК) обеспечивает считывание информации из ОП, преобразует её в соответствии с требуемым режимом отображения и формирует изображение на экране. Узел интерфейс: 1) Внутренний – реализует обмен информацией между ЦП, ОП и встроенным интерфейсом ввода-вывода. 2) Встроенный интерфейс обеспечивает подключение к ПЭВМ внешних устройств. Функционально сигналы внутреннего интерфейса разделяются на три типа: шина данных (8 линий), шина адреса (16 линий) и шина управления и синхронизации (16 линий).

Принцип работы Оперативная память связана с ДК также как и ЦП. Шина Адреса ДК и Шина Данных ДК по Шине Адреса от ДК к ОП передается 16-ти разрядный код адреса, сформированный в ДК, а по Шине Данных ДК из ОП в ДК поступают 16-разрядные коды данных, которые после соответствующей обработки выводятся на экран монитора. ДК только считывает информацию из ОП, таким образом, к информации, хранящейся в ОП, имеют доступ два пользователя: ЦП и ДК. Существует несколько способов организации работы ОП на двух пользователей. В ПЭВМ «Агат» применён способ разделения фазы основной тактовой частоты. В основе способа лежат отличительная особенность. МП производит обмен информацией по шине данных только в течение действий высокого уровня тактовых импульсов (1,021 МГц) синхронизирующих работу ЦП. При низком уровне тактовых импульсов МП осуществляет внутреннее переключение (действии операции) и не пользуется шиной данных, а, следовательно, и ОП. ЦП получает доступ к ОП в течение действия высокого уровня тактовых импульсов (фаза процессора), а на время действия низкого уровня импульсов к ОП получает доступ ДК.

Технические характеристики ü Адресное пространство 64 КБ ü Информационная шина 8 бит (параллельная, двунаправленная) ü Адресная шина 16 бит (параллельная однонаправленная) ü Количество выполняемых команд 56 ü Количество способов адресации 13 ü Напряжение питания +5 В ü Тактовая частота 1,021 МГц ü Прерывания – 2 типа (маскируемое и немаскируемое) ü Быстродействие – более 500000 коротких операций в секунду и более 340000 длинных операций в секунду Вопрос № 5 Вопрос № 6 Вопрос № 7 Вопрос № 8 Вопрос № 9 Вопрос № 10 Дать определение операций логического умножения, логического сложения, операции Пирса, операции Шеффера. Привести условное обозначение логических элементов и примеры их использования при построении узлов ЭВМ. Дизъюнкция (логическое сложение), (ИЛИ). Функция истинна, если истинна хотя бы одна из переменных. Данная функция реализуется логическим элементом, называемым дизъюнктором. Дизъюнктор может иметь два и более (до восьми) входов.

Отрицание конъюнкции, (И-НЕ). Функция ложна тогда, когда все переменные истинны. Эта функция называется И-НЕ и реализуется элементом Шеффера (элементом И-НЕ). Элемент Шеффера может иметь два и более входов. Количество входов указывается в обозначении логического элемента, например, 2И-НЕ; 4И-НЕ; 8И-НЕ.

Отрицание дизъюнкции. Функция ложна тогда, когда хотя бы одна из переменных истинна. Такая функция реализуется логическим элементом, который называется элементом Пирса (элементом ИЛИ-НЕ). Элемент Пирса может иметь два и более входов.

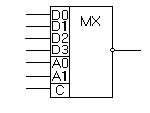

Логические элементы, как простые, так и сложные, используются для построения более сложных функциональных узлов и логических схем. При этом выделяются три основных базиса (набора логических элементов), позволяющих построить любую сколь угодно сложную схему, реализующую любую сколь угодно сложную логическую или арифметическую функцию. Первый (основной) базис логических элементов – И, ИЛИ, НЕ, т.е. содержащий элементы: конъюнктор, дизъюнктор и инвертор. Второй базис – И-НЕ, в который входят элементы Шеффера. Третий базис – ИЛИ-НЕ, содержащий элементы Пирса. Дешифраторы строятся на элементах И, имеющих такое количество входов сколько и информационных входов дешифратора. (Рисунок 8) Однотактные асинхронные триггеры строятся на логических элементах, имеющих не менее двух входов и инвертирующих выходной сигнал. Следовательно, для построения триггера пригодны элементы Шеффера (элементы И-НЕ) и элементы Пирса (элементы ИЛИ-НЕ). (Рисунок 7) Вопрос №12. Дать определение мультиплексора в зависимости от его назначения. Составить схему мультиплексора на логических элементах и пояснить принцип её действия. Привести условное обозначение мультиплексора на электрических схемах. Мультиплексоры—это узлы, преобразующие параллельные цифровые коды в последовательные. Они имеют несколько информационных и адресных входов, вход для подачи синхронизирующего сигнала и один выход. Каждому из информационных входов мультиплексора присваивается номер, называемый адресом. При подаче синхронизирующего сигнала мультиплексор подключает один из входов, адрес которого задаётся двоичным кодом на адресных входах, к выходу. Таким образом, подавая на адресные входы адреса информационных входов, можно передавать параллельные коды с этих входов на выход в последовательном коде.

Мультиплексор является логическим переключателем. Он имеет один выход и несколько (2 n) входов. Выбор входа, который соединяется с выходом, осуществляется специальными сигналами, называемыми адресными. Количество адресных входов - n. Мультиплексор, как правило, синхронный, т.е. входной сигнал передается на выход только при активном уровне сигнала синхронизации (управления).

Сигнал С—синхронизирующий, если он равен 0, на выходе мультиплексора будет также 0, т.к. если на элемент И поступает хотя бы один 0, то на выходе элемента получается 0. сигналы D0, D1, D2, D3—информационные. Сигналы А и В—адресные, нужны для выбора входа, который необходимо соединить с выходом. Если оба сигнала равны 0, то проходя через инверторы эти сигналы становятся равны 1, затем сигналы поступают на элемент И1, т.к. оба сигнала имеют высокий уровень напряжения,=>, сигнал с выхода И1 будет зависеть от сигнала D0, на все остальные элементы И будет поступать хотя бы один 0. Затем все сигналы с выходов И поступают на элемент ИЛИ. Если сигнал D0 равен 1, то на выходе формируется 1, если нет, то 0. Сигнал С—синхронизирующий, если он равен 0, на выходе мультиплексора будет также 0, т.к. если на элемент И поступает хотя бы один 0, то на выходе элемента получается 0. сигналы D0, D1, D2, D3—информационные. Сигналы А и В—адресные, нужны для выбора входа, который необходимо соединить с выходом. Если оба сигнала равны 0, то проходя через инверторы эти сигналы становятся равны 1, затем сигналы поступают на элемент И1, т.к. оба сигнала имеют высокий уровень напряжения,=>, сигнал с выхода И1 будет зависеть от сигнала D0, на все остальные элементы И будет поступать хотя бы один 0. Затем все сигналы с выходов И поступают на элемент ИЛИ. Если сигнал D0 равен 1, то на выходе формируется 1, если нет, то 0.

Вопрос №14. Дать определение счётчика импульсов. Нарисовать схему трёхразрядного двоичного счётчика импульсов и пояснить принцип её действия. Привести условное обозначение счётчика импульсов на электрических схемах. Счетчик – это функциональный узел, осуществляющий счет импульсов и хранение кода числа подсчитанных импульсов. Свойства счетчика характеризуется коэффициентом пересчета (Ксч) – величиной указывающей количество его устойчивых состояний. Другими параметрами счетчика являются: разрешающая способность, максимальное быстродействие и информационная емкость.

Перед началом счёта сигналом Уст. 0 счётчик устанавливается в состояние 000. На временной диаграмме счётчика видно, что после прихода 7-го входного сигнала на вход Т0 показание счётчика будет 111. при поступлении 8-го входного сигнала Т0 счётчик переходит в исходное состояние 000. При этом на выходе счётчика Q2 в результате перехода триггера ТТ2 в состояние 0 возникает сигнал переноса, который называют сигналом переполнения счётчика.

Условное обозначение счётчика импульсов на электрических схемах.

Вопрос №15. Устройство управления ЭВМ. Структурная схема. Назначение узлов. Принцип работы.

Выполнение команды центральным устройством управления (ЦУУ) процессора проводится обычно в такой последовательности: -выборка команды из ОП; -формирование исполнительных адресов операндов по информации, содержащейся в коде команды; -выборка операндов из ОП; -выполнение действий в арифметическо-логических блоках; -отсылка результата выполнения операции в ОП. Все действия, связанные с преобразованием кодов команд в наборы управляющих сигналов (УС) и исполнительные адреса, выполняются непосредственно в ЦУУ. В ЦУУ входят: 1. Блок выборки команд и данных(БВКиД). Он предназначен для приёма команды, хранения ёё до окончания операции, расшифровки кода операции, модификации адресов, формирования адреса следующей команды, выдачи адресов операндов и следующий команды в ОЗУ, для хранения кодов операндов, принимаемых из ОЗУ и выдача в ОЗУ адреса, по которому производится запись результата выполнения операции. 2. Блок центрального управления(БЦУ). Вырабатывает необходимую последовательность УС при выполнении каждой команды программы для АЛУ и других устройств ЭВМ. 3. Пульт управления(ПУ). Обеспечивает управление работой ЭВМ со стороны оператора, визуальный контроль состояния отдельных устройств и проведение профилактических мероприятий. 4. Блок прерываний(БП). Служит ля реализации запросов на прерывание в соответствии с их приоритетами. 5. Блок управления ОП(БУОП). Обеспечивает обмен информации с ОП не только процессором, но и всеми каналами ввода-вывода(КВВ). 6. Блок защиты памяти(БЗП). Предназначен для предотвращения искажения любой информации, хранящейся в ОП, по записи и её возможного искажения вследствие возможных ошибочных обращений к ОП при считывании. 7. Блок внешних связей(БВС). Обеспечивает обмен управляющей информацией с другим процессором при построении и работе мультипроцессорной системы. 8. Блок таймеров(БТ). Служит для подсчёта временных интервалов и управления работой процессора в системе по принимаемым временным соотношениям. 9.

Вопрос №16. Дать определение регистра. Нарисовать схему запоминающего регистра и пояснить принцип её действия. Привести условное графическое обозначение запоминающего регистра на электрических схемах.

Регистром называется функциональный узел, предназначенный для записи, хранения и выдачи многоразрядного кода двоичного числа. Регистр хранения информации принимает и выводит код только в параллельном формате и не преобразует код. В большинстве случаев регистры хранения строятся на D-триггерах.

На вход регистра подаётся код числа в двоичном формате. Приём кода происходит при поступлении синхроимпульса С на вход регистра. При поступлении сигнала С триггеры в регистре переключатся в нулевое или единичное состояние, в зависимости от сигналов D0, D1, D2, D3, и будут находится в этом состоянии до прихода очередного синхроимпульса и изменения информационных сигналов.

Условное графическое обозначение регистра на электрических схемах.

Вопрос №18. Дать определение дешифратора в зависимости от его назначения. Составить схему дешифратора на логических элементах. Пояснить принцип действия дешифратора и привести его графическое изображение на электрических схемах.

Дешифратор – функциональный узел, преобразующий код двоичного числа в управляющий сигнал логического уровня, который возникает на одном из его выходов. Номер выхода соответствует значению кода поданному на входы. Если количество выходов N=2m, где m – количество информационных входов, то дешифратор называется полным. Входы и выходы дешифраторы могут быть как прямыми так и инверсными. Активным уровнем сигнала для прямого входа является высокий, а для инверсного – низкий. Если выход прямой, то при его активизации на нем действует высокий уровень напряжения, на остальных выходах – низкий. На активизированном инверсном выходе действует низкий уровень напряжения, а на остальных – высокий. Дешифраторы строятся на элементах И, имеющих такое количество входов сколько и информационных входов дешифратора. Часто дешифраторы делаются синхронными. Это значит, что выходные сигналы появляются только при наличии дополнительного управляющего сигнала. Такой сигнал называется синхронизирующим, он может быть как высокого, так и низкого уровня.

Вопрос №36, Дать определение сумматора в зависимости от его назначения. Нарисовать схему полного четырехразрядного сумматора и пояснить принцип ее действий. Построить схему сумматора на логических элементах.

Сумматором называется функциональный узел, выполняющий операцию арифметического сложения двух двоичных чисел. Простейшим является одноразрядный неполный сумматор, который называется полусумматором. Он имеет два входа, на которые подаются электрические сигналы (уровни напряжения), соответствующие значениям данных разрядов (ai, bi) суммируемых чисел. Выходов у полусумматора тоже два. На одном выдается результат суммы (Si), а на другом – результат переноса из данного разряда в следующий (Pi+1) (Рис. 28).

Рис. 28. Электрическая схема полусумматора и его условное графическое обозначение.

Поскольку у полусумматора только два входа, то его нельзя применять в случае, когда возникает перенос из младшего разряда в данный, т.к. нет входа, на который можно подать сигнал переноса. В большинстве случаев применяется полный одноразрядный сумматор, имеющий три входа (ai, bi, pi) и два выхода (Si и Pi+1). Полный сумматор строится на полусумматорах с применением логических элементов. (Рис. 29). Следует обратить внимание на то, что все три входа сумматора равнозначны, т.е. не имеет значение на какой вход подавать сигнал переноса, а на какие – разряды чисел.

Рис. 29. Электрическая схема полного одноразрядного сумматора и его условное графическое обозначение

Для сложения многоразрядных двоичных чисел применяются многоразрядные сумматоры, которые строятся на одноразрядных, причем выход переноса сумматора младшего разряда соединяется со входом сумматора старшего разряда. Многоразрядные сумматоры применяются для построения арифметико-логических устройств процессоров и сопроцессоров.

Рис. 30. Электрическая схема многоразрядного (четырехразрядного) сумматора и его условное графическое обозначение.

Архитектура ЭВМ Теоретические вопросы: Вопрос № 1 Состав электронно-вычислительных машин. Структурная схема. Назначение узлов и блоков ЭВМ. Характеристики ЭВМ.

Электронно-вычислительная машина состоит из многих частей. Самые важные (без них компьютер не получится) это: процессор, оперативная память, ПЗУ (BIOS), ВЗУ (жёсткий диск). Также не маловажны устройства ввода/вывода (клавиатура, монитор, принтер и др.). Все эти выше упомянутые устройства (элементы) крепятся или подключаются к материнской плате, на которой имеются специальные (PS\2,COM,LPT, слоты для процессора и ОЗУ) или универсальные выводы (USB, слоты PCI). Информация передаётся на выводы через контроллер ввода/вывода, который контролирует потоки информации. С ним же соединён BIOS, который хранит все настройки машины. На этот контроллер информация приходит по шине (интерфейсу) ввода/вывода, которая подключена к контроллеру памяти. Интерфейс вв/выв соединяет центральную часть машины с внешней. К контроллеру памяти подключены основные части машины: ОЗУ, графический порт и через шину процессора подключен центральный процессор.

Рисунок 1. Структурная схема современной ЭВМ.

ЭВМ характеризуется различными параметрами, такие как: · объём внутренней памяти (байты, регистры) – влияет на производительность и быстродействие машины · объём оперативной памяти (байты, Кбайты…) – влияет на производительность и быстродействие машины, на разрядность шины адреса. · количество способов адресации · количество выполняемых операций – влияет на способность выполнять больше операций · пропускная способность (разрядность) различных шин – влияет на производительность и быстродействие машины · тактовая частота процессора – влияет на производительность и быстродействие машины

Вопрос № 2

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 4354; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.116.28.79 (0.01 с.) |

ШАДК

ШАДК

ШАЦП

ШАЦП

Конъюнкция (логическое умножение), (И). Функция истинна только в том случае, когда все переменные истинны. Эта функция реализуется логическим элементом, который называется конъюнктором. Конъюнктор имеет два и более входов.

Конъюнкция (логическое умножение), (И). Функция истинна только в том случае, когда все переменные истинны. Эта функция реализуется логическим элементом, который называется конъюнктором. Конъюнктор имеет два и более входов.

Условное обозначение мультиплексора, где: D0, D1, D2, D3—информационные входы, A0, A1—адресные входы, С—вход синхронизации.

Условное обозначение мультиплексора, где: D0, D1, D2, D3—информационные входы, A0, A1—адресные входы, С—вход синхронизации.

Блок синхронизации(БС). Обеспечивает жёсткую синхронизацию работы всех блоков и устройств процессора.

Блок синхронизации(БС). Обеспечивает жёсткую синхронизацию работы всех блоков и устройств процессора.