Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

П5. Анализ и синтез последовательностных цифровыхСодержание книги

Поиск на нашем сайте устройств (см. задание КР7-3) П5.1 Основные определения Последовательностными устройствами или автоматами с памятью называют логические устройства, выходной сигнал которых определяется не только действующей в настоящий момент на входе комбинацией переменных, но и всей последовательностью входных и выходных переменных, действовавших в предыдущие моменты времени. Реализация такого алгоритма работы предполагает, что на входе некоторого логического устройства действует не только комбинация внешних входных сигналов, но и некоторые сигналы, отображающие предысторию работы устройства. Такие сигналы могут вырабатываться в самом комбинационном устройстве и совместно с внешними подаваться на его вход. Очевидно, что, по сути, в последовательностном устройстве существует канал передачи информации с его выхода на вход, причем эта информация суммируется с внешней. Следовательно, такой канал передачи является цепью положительной обратной связи (ПОС), охватывающей исходное комбинационное устройство. На рис. П5.1 приведена обобщенная структурная схема, реализующая описанный алгоритм работы устройства.

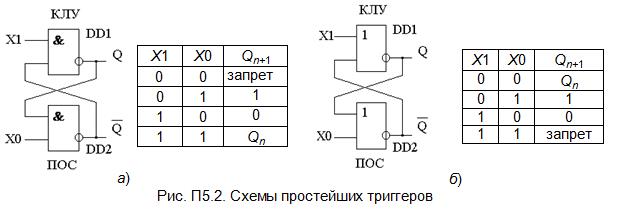

Представленная на рис.П5.1 структура является конечным автоматом, известным как автомат Мили. Если в схеме отсутствует входной сигнал X [ n -1…0], то получим структуру, известную как автомат Мура. В зависимости от выполнения блока ПОС данная структура порождает два класса устройств. Если в качестве блока обратной связи используется комбинационное устройство, получаем класс устройств называемых триггерами. Эти устройства являются элементарными ячейками памяти, способными хранить один бит информации. Если блок обратной связи сам выполнен как последовательностное устройство, например триггер, то получаем более сложное устройство, которое и является конечным автоматом. Рассмотрим особенности работы обоих классов последовательностных устройств. П5.2 Триггеры Триггером называется устройство, способное формировать два устойчивых значения выходного сигнала и скачкообразно изменять эти значения под действием внешнего управляющего сигнала. Простейший триггер может быть построен, если в качестве комбинационного логического устройства использовать простейший элемент 2И-НЕ или 2ИЛИ-НЕ. Так как эти элементы содержат инвертор, то для формирования сигнала ПОС выходной сигнал элемента необходимо дополнительно инвертировать. С этой целью можно использовать второй такой же элемент. На рис.П5.2 приведены два варианта построения простейшего триггера. Он снабжен двумя информационными входами

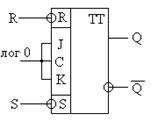

Реальные схемы триггеров содержат одну или несколько из приведенных ячеек памяти и некоторую комбинационную схему, предназначенную для формирования информационных сигналов Х 1 и Х 0. При описании поведения триггера пользуются понятиями: триггер установлен или триггер находится в состоянии установки – выходной сигнал Q = 1; триггер сброшен или триггер находится в сброшенном состоянии – выходной сигнал Q = 0, а так же понятием активного входного сигнала под которым понимают такое его значение, которое однозначно определяет входной сигнал устройства. Существующие типы триггеров можно квалифицировать по различным признакам. Наиболее часто в качестве такого признака используют тип информационных входов, управляющих работой устройства. Различают следующие типы управляющих входов триггеров: R – раздельный вход сброса триггера (Q = 0); S – раздельный вход установки триггера (Q = 1); K – вход сброса универсального триггера (Q = 0); J – вход установки универсального триггера (Q = 1); T – счетный вход триггера; D – информационный вход, сигнал которого переписывается на выход (Q = D); С – вход синхронизации. По этим признакам различают синхронные (переключаются только при наличии сигнала на входе синхронизации С) и асинхронные (переключаются сразу после изменения информационных сигналов) R S -триггера, T- триггера, JK -триггера и D -триггера, которые могут быть только синхронными. Простейшими триггерами (см. рис. П5.2) являются асинхронные RS -триггеры. Для триггера (рис. П5.2 а) активным входным сигналом является сигнал «лог.0». Вход Х 1 = S, вход X 0 = R. Для триггера (рис. П5.2 б) активным является сигнал «лог.1»: вход Х 1 = R, X 0 = S. Условное изображение асинхронного RS-триггера показано на рис. П5.3. В левом выделенном поле указываются все информационные входы триггера. При этом если активным логическим сигналом является сигнал «лог.0» то соответствующий вход снабжается кружком (как выход На практике, работу триггера удобно описывать не таблицами истинности а таблицами переходов, указывающими какая комбинация информационных сигналов приводит к заданному изменению выходного сигнала (состояния) триггера.

П р и м е ч а н и я. 1. Таблицы переходов приведены для случая асинхронных триггеров. Работу синхронного триггера можно описать следующей ФАЛ:

на его входе синхронизации С. 2. Прочерк в таблице переходов означает, что на данный информационный вход может быть подан произвольный логический сигнал (либо «0», либо «1»). Таблица П5.1. Основные типы триггеров.

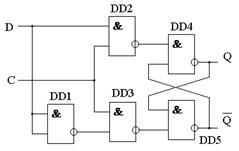

Обычно все типы триггеров дополнительно снабжаются асинхронными входами R и S, которые воздействуют непосредственно на элемент памяти. Эти входы позволяют устанавливать или сбрасывать триггер вне зависимости от остальных информационных сигналов. На рис. П5.4 приведены логическая схема и обозначение синхронного RS -триггера с асинхронными установочными входами.

Таблица П5.2. Варианты использования JK -триггера

Из приведенной таблицы следует, что кроме D -триггера, для получения остальных типов триггеров на входы JK -триггер просто необходимо подать соответствующие комбинации сигналов. Следует отметить, что при подаче одновременно активных сигналов на входы J и K, JK- триггер начинает работать как счетный. Это следствие наличие в его внутренней структуре дополнительных цепей обратной связи. П5.3. Конечные автоматы Ранее отмечалось, что если блок обратной связи обобщенной структурной схемы (см. рис. П5.1) последовательностного устройства содержит элементы памяти, например триггеры, то полученная структура является конечным автоматом. Термин «конечный» означает, что число выходных сигналов, и, следовательно, состояний автомата, является ограниченным. Введем понятие состояния автомата. Это понятие уже вводилось ранее для одиночного триггера и под ним понимался выходной сигнал триггера. В общем случае, блок обратной связи автомата может содержать несколько триггеров. Поэтому под состоянием понимается сигнал, формируемый на выходе блока обратной связи. С учетом сказанного обобщенную структурную схему конечного автомата можно представить в виде двух подсистем: комбинационной и триггерной или подсистемы памяти (рис. П5.5]. В отличие от ранее рассмотренной, приведенная структура предполагает наличие еще одного сигнала. Это сигнал синхронизации С, используемый для инициализации переключения элементов памяти (триггеров) подсистемы памяти. Таким образом, изменение выходного сигнала автомата Z [ m -1…0] возможно в двух случаях. При изменении входного сигнала

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-10; просмотров: 216; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.96 (0.007 с.) |

и

и  и двумя выходами

и двумя выходами  и

и  , сигналы которых связанны операцией инверсии. Рядом со схемами приведены таблицы истинности, поясняющие работу этих устройств. В таблицах под Qn понимается исходное значение выходного сигнала триггера, а под Qn +1 - значение выходного сигнала после воздействия входных переменных. Из таблиц следует, что существует три разновидности комбинаций входных сигналов Х 1 и Х 0. Первая - это комбинация при которой значение выходного сигнала остается неизменным. Вторая – комбинация которая однозначно определяет выходной сигнал устройства. И третья - это запрещенная комбинация при которой не выполняется определение триггера (сигнал

, сигналы которых связанны операцией инверсии. Рядом со схемами приведены таблицы истинности, поясняющие работу этих устройств. В таблицах под Qn понимается исходное значение выходного сигнала триггера, а под Qn +1 - значение выходного сигнала после воздействия входных переменных. Из таблиц следует, что существует три разновидности комбинаций входных сигналов Х 1 и Х 0. Первая - это комбинация при которой значение выходного сигнала остается неизменным. Вторая – комбинация которая однозначно определяет выходной сигнал устройства. И третья - это запрещенная комбинация при которой не выполняется определение триггера (сигнал  ), т.е. устройство теряет способность хранить информацию, так как после снятия этой комбинации значение выходного сигнала невозможно прогнозировать.

), т.е. устройство теряет способность хранить информацию, так как после снятия этой комбинации значение выходного сигнала невозможно прогнозировать.

В табл. П5.1 приведены возможные схемы и таблицы переходов различных типов триггеров при условии, что активным логическим сигналом является сигнал «лог. 1».

В табл. П5.1 приведены возможные схемы и таблицы переходов различных типов триггеров при условии, что активным логическим сигналом является сигнал «лог. 1». т.е. синхронный триггер переключается только в момент активного уровня сигнала

т.е. синхронный триггер переключается только в момент активного уровня сигнала

и при изменении состояния автомата S [ p -1…0], происходящего в момент переключения триггеров его подсистемы памяти. Последнее определяется сигналом синхронизации С.

и при изменении состояния автомата S [ p -1…0], происходящего в момент переключения триггеров его подсистемы памяти. Последнее определяется сигналом синхронизации С.