Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Память с последовательным доступомСодержание книги Похожие статьи вашей тематики

Поиск на нашем сайте VT1 MPSH2S Z1 CSS455EB п C1pC2lQ0n 10 Ом и

к 6-ЗВ VT2 2SBG62(C) VD1 LN66S

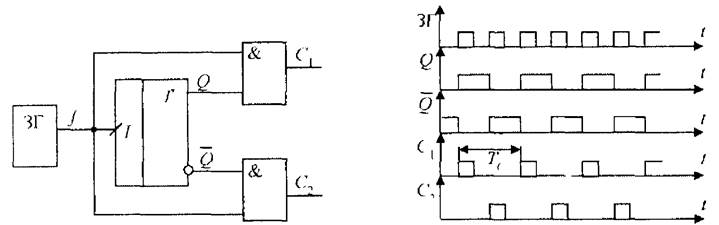

7 8 Частота ГТИ измеряется десятками, сотнями мегагерц и гигагерцами. В литературе ГТИ часто называют генераторами синхронизирующих импульсов, а сами импульсы называют синхронизирующими или синхроимпульсами. Амплитуда и полярность импульса С зависит от физических принципов построения машины. Принцип подачи информации на входы элементов и узлов в тактовые моменты называется дискретизацией сигналов во времени.

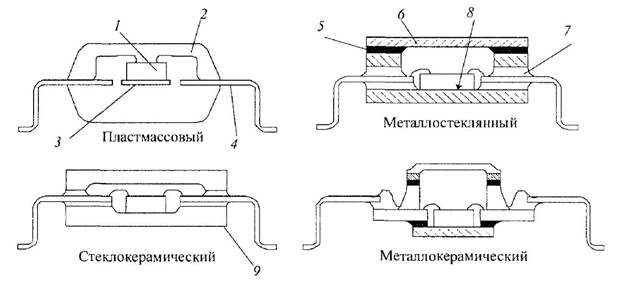

Набор цифровых микросхем с общими конструктивно-технологическими и схемотехническими признаками образует серию ИМС. В компьютерной схемотехнике широко применяются цифровые полупроводниковые корпусные ИМС на основе кремния и арсенида галлия. В полупроводниковых ИМС все компоненты и соединения между ними выполнены в объеме и на поверхности кристалла площадью от 4 до 100 мм2. В гибридных ИМС навесные компоненты крепятся на поверхности диэлектрической подложки. В пленочных ИМС все компоненты и соединения между ними выполнены в виде тонких пленок на диэлектрической подложке. Коэффициент объединения по входу характеризует число логических входов логического элемента — обычно 1, 2, 3, 4 или 8 N= 3 iV=8 N = 2И-2И-ЗИ-ЗИЛИ-НЕ Коэффициент объединения по выходу N0 характеризует допустимое количесг во соединенных между собою выходов логических элементов Коэффициент разветвления по выходу Np характеризует нагрузочную способность логического элемента, то есть максимальное число входов идентичных схем, которое может быть одновременно подключено к выходу данного элемента без нарушения его работоспособнрсти

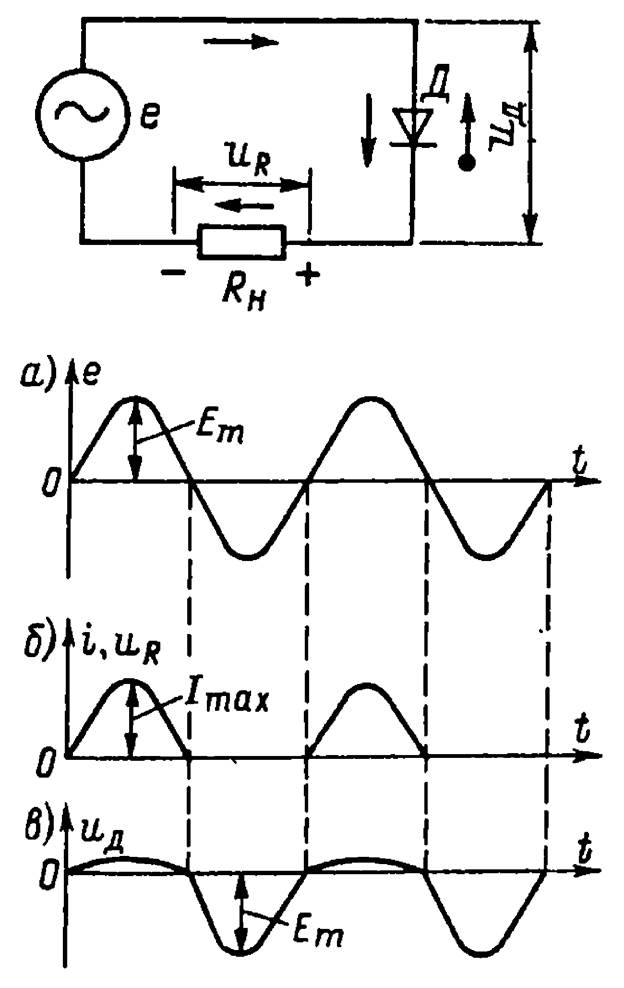

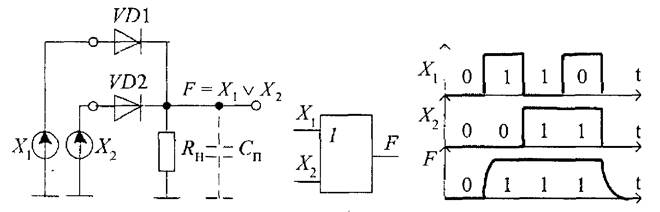

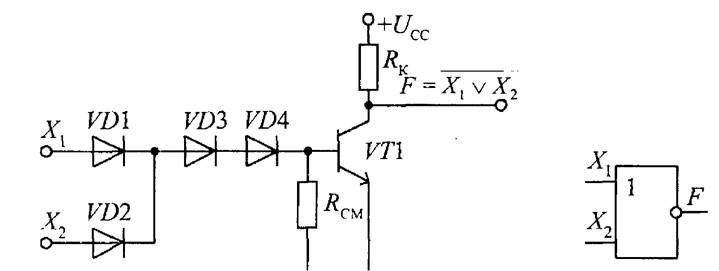

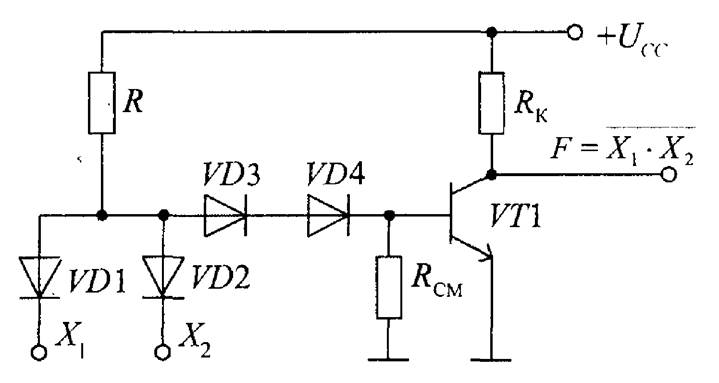

Различают следующие виды логики потенциальных элементов: • диодную (ДЛ) и диодно-транзисторную логику (ДТЛ); • транзисторную логику (ТЛ), в которой выделяют схемы с непосредственными связями (ТЛНС), с резисторными связями (ТЛРС) и резисторно- конденсаторными связями (ТЛРКС); • интегральную инжекционную логику (ИИЛ или И2Л); • транзисторно-транзисторную логику (ТТЛ) и ее модификации с диодами Шотки (ТТЛШ); • эмиттерно-связанную логику (ЭСЛ); • МОП-транзисторную логику (р-МОП, л-МОП, КМОП); • логику на основе арсенида галлия (AsGa).

Диодные логические элементы Элемент ИЛИ

Элемент И

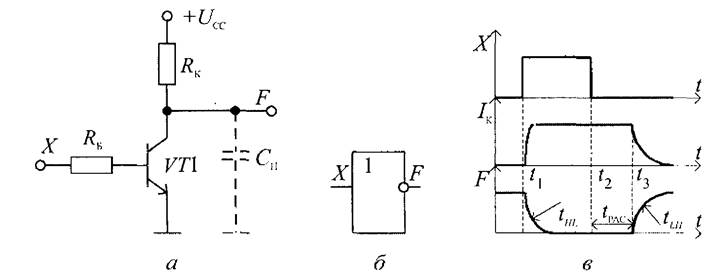

Элемент НЕ

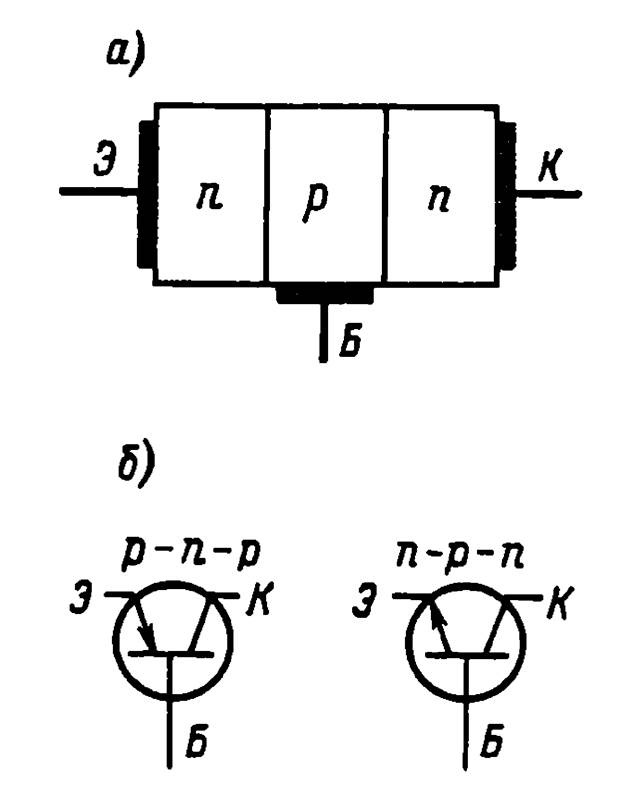

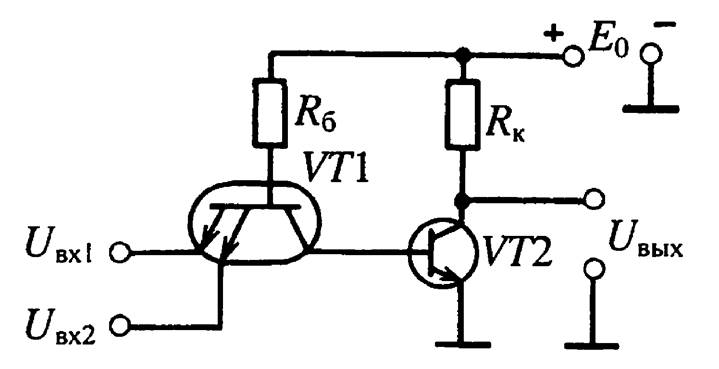

Транзисторная логика Элементы ТЛ строят путем параллельной подключения коллекторов транзисторов к общему резистору коллекторной нагрузки RK. Выходное напряжение снимается с объединенных коллекторов. Если на один из входов поступает высокий уровень напряжения UIH, то соответствующий транзистор открывается и на выходе устанавливается низкий уровень сигнала UOL. Высокий уровень напряжения формируется на выходе только в случае подачи на все входы низких уровней U/L.

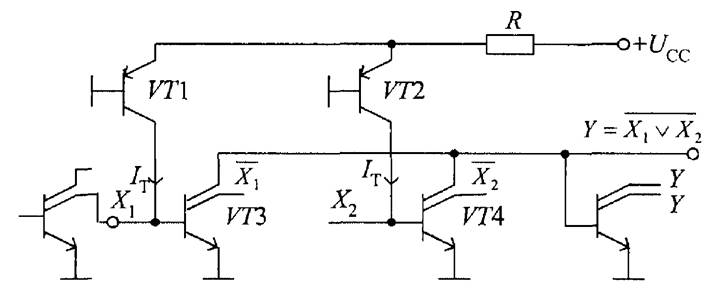

Интегральная инжекционная логика Схема включает инжекционные р-п-р транзисторы VT\, VT2, включенные по схеме с общей базой, и входные многоколлекторные п-р-п транзисторы F73, VT4, включенные по схеме с общим эмиттером. Эмиттеры транзисторов VT1, VT2 называются инжекторами, а протекающий через них дырочный ток — инжекционным. Каждый из транзисторов VT\, VT2 образует вместе с источником питания и внешним резистором R источник тока, который питает индивидуальным током /т входы транзисторов Щ VT4.

Особенностями элементов И Л являются: • "безрезисторность", характерная для МОП-структур, которая впервые была реализована в схемотехнике И2Л; • соединение областей базы и коллектора инжекционных р-п-р транзисторов соответственно с областями эмиттера и коллектора входных п-р-п транзисторов, а также малое число схемных компонентов и соединений между ними (количество операций маскирования и диффузии в два раза меньше сравнительно с элементами ТТЛ); • низкий уровень напряжения UL = 0,01 В снимается с коллектора насыщенного транзистора, а высокий уровень напряжения UH= 0,8 В — с коллектора закрытого транзистора, причем этот уровень ограничивается напряжением базы насыщенного транзистора нагрузки; используется режим микротоков, в котором токи коллектора изменяются от десятков до сотен микроампер; работоспособность элементов сохраняется при изменении значения тока в них на несколько порядков; • на коллекторах входного транзистора реализуется инверсия переменной, а на соединенных коллекторах транзисторов VT3, VT4 выполняются операции НЕ-ИЛИ. Транзисторно-транзисторные логические элементы

Многоэмиттерный транзистор выполняет операцию И, транзистор VT2 — операцию НЕ. Поэтому элемент в целом реализует функциюF = ХхХ2

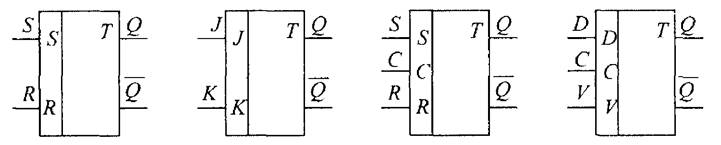

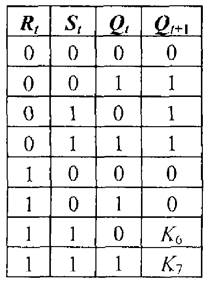

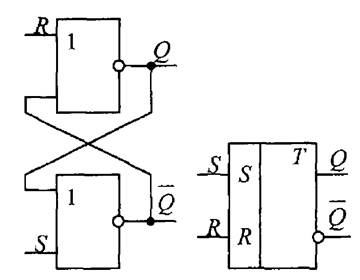

ТРИГГЕРЫ Триггер - это элементарный запоминающий элемент с двумя устойчивыми состояниями. Триггеры классифицируют по следующим признакам: • логике функционирования (RS, JK, D, Т и др.); • способу записи информации (асинхронные и синхронные); • моменту реакции на тактовый сигнал (статические, динамические); • количеству тактов синхронизации (одно-, двух- и трехтактные); • количеству ступеней (одно- или двухступенчатые триггеры); • составу логических элементов (триггеры на элементах НЕ И, НЕ ИЛИ, НЕ И ИЛИ и др.). В соответствии с логикой функционирования различают следующие триггеры: • с раздельной установкой состояний "О" и "1" (RS-триггеры); • с одним информационным входом (0-триггеры); • со счетным входом (Г-триггеры); • универсальные с раздельной установкой состояний "О" и "1" (JK-триггеры); • комбинированные (RST-, RSJK-триггеры); • со сложной входной логикой. Входы триггеров: - информационные R, S, T, и др. - управляющие C, V и др. С - синхронизирующий (тактовый) сигнал, V - разрешающий Выходы: Q и Q Асинхронные триггеры - нетактируемые, не имеют С-входа. Запись информации происходит в любой момент времени.

В зависимости от количества тактовых сигналов, необходимых для формирования нового состояния, различают однотактные, двухтактные и многотактные триггеры. По способу управления записью (моменту реакции на тактовый сигнал) выделяют синхронные триггеры со статическим (по уровню), динамическим (по фронтам) и двухступенчатым управлением. В асинхронных триггерах запись нуля и единицы возможна в любой момент времени, при этом входной информационный сигнал одновременно является и управляющим. В синхронных триггерах с управлением по уровню запись информации возможна только в течение длительности тактового сигнала.

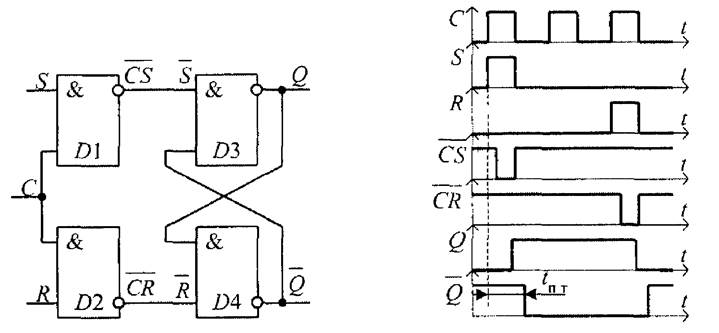

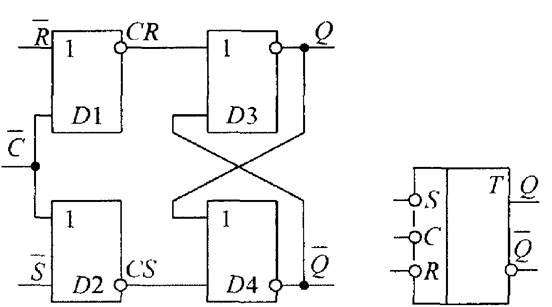

RS-триггер RS-триггером называют запоминающий элемент с раздельными информационными входами для установки его в состояние "О" (R-вход) и в состояние "1" (5-вход). Название "ftS-триггер" образовано от первых букв слов RESET (сброс) и SET (установка).

Асинхронный RS-триггер

Обратная логика (Инверсные входы), ИЛИ-НЕ

Синхронный Я5-триггер

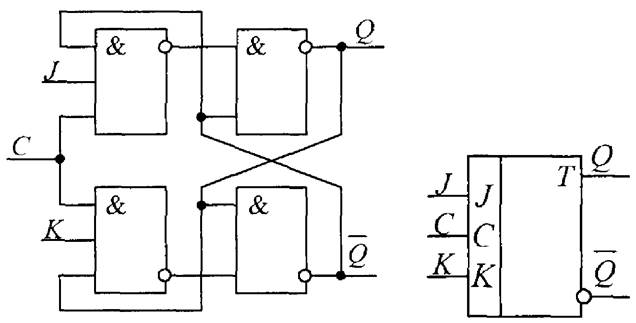

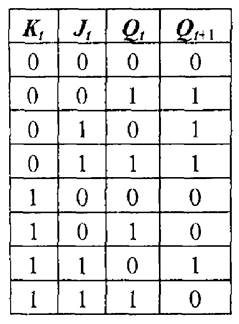

Триггеры типа JK Триггером типа JK называется запоминающий элемент с двумя устойчивыми состояниями и информационными входами J (аналог S) и К (аналог R), которые обеспечивают соответственно раздельную установку состояний "1" и "О". Он функционирует подобно /^-триггеру, однако при совпадении сигналов JK ~ 1 переключается в противоположное состояние, то есть реализует сложение сигналов по модулю два. Таким образом, Ж-триггер не имеет запрещенных комбинаций входных сигналов.

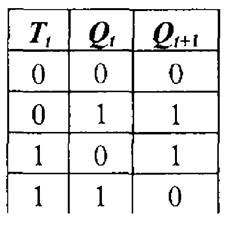

Т-триггер Триггером типа Т называется запоминающий элемент с двумя устойчивыми состояниями и одним информационным 7-входом. Состояние Г-триггера изменяется на противоположное после каждого поступления счетного сигнала на Г-вход.

D-триггер Триггером типа D называется синхронный запоминающий элемент с двумя ус тойчивыми состояниями и одним информационным D-входом. Закон функциониро' вания D-триггера описывается логическим уравнением: 0,-н = CtD, Это уравнение показывает, что после переключения состояние D-триггера по вторяет значение сигнала на.D-входе в тактовые моменты времени. Поэтому в ли тературе D-триггеры часто называют триггерами задержки (от Delay — задержка).

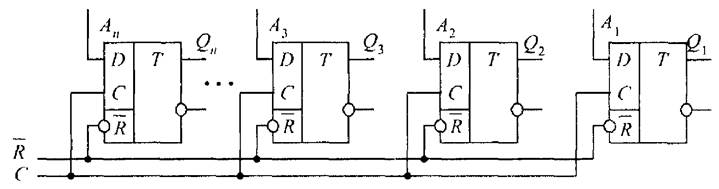

Регистром называется типовой функциональный узел компьютера, предназначенный для приема, временного хранения, преобразования и выдачи «-разрядного двоичного слова. Регистр содержит регулярный набор однотипных триггеров, в каждом из которых хранится значение одного двоичного разряда машинного слова.

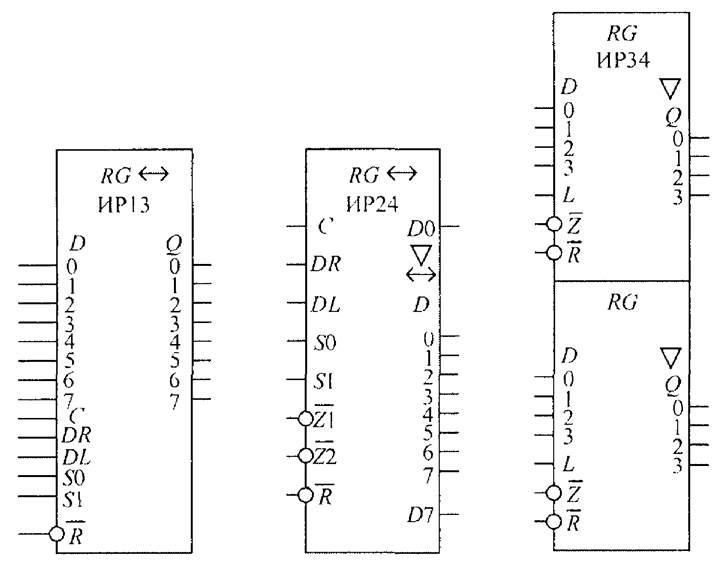

Регистры, предназначенные только для приема (записи), хранения и передачи информации, называются элементарными или фиксаторами. Регистры, в которых хранение данных совмещается с микрооперациями сдвига, называются сдвиговыми. Виды регистров •способу управления записью — асинхронные и синхронные; •способу записи и выдачи двоичных слов — параллельные, последовательные и универсальные; в параллельных регистрах запись и выдача слов производится одновременно всеми разрядами, а в последовательных — разряд за разрядом в направлении от младших разрядов к старшим или наоборот; универсальные регистры обеспечивают как параллельный, так и последовательный обмен информацией; •числу линий для представления значения одного разряда слова (бита информации) — однофазные и парафазные; при однофазном представлении значение каждого разряда слова передается по одной линии связи, а при парафазном — по двум линиям (одновременно отображается прямое и инверсное значение разряда); •числу тактов для записи слова — одно-, двух- и многотактные; •составу выполняемых микроопераций — установочные, записи, считывания, поразрядные логические и сдвига, а также преобразования последовательного кода в параллельный и наоборот; •направлению сдвига — односторонние (левый или правый сдвиг) и двухсторонние (реверсивные); •типу используемых триггеров; •элементной структуре — потенциальные, импульсные и потенциально- импульсные.

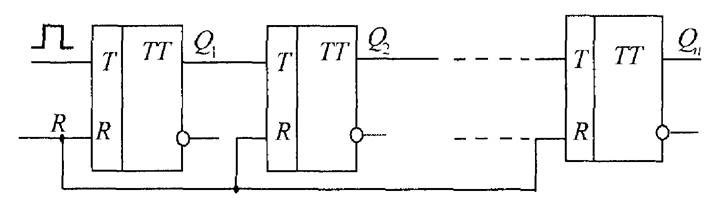

данных D0-D1, синхронизации С, последовательного приема DR и DL, задания режимов работы 51, SO и вход сброса R. Информация считывается с параллельных выходов Q0-Q7. Разряды нумеруются слева направо: Q0 — старший разряд, Q1 — младший. Счетчики Счетчиком называется типовой функциональный узел компьютера, предназначенный для счета входных импульсов. Счетчик представляет собой связанную цепочку Г-триггеров, образующих память с заданным числом устойчивых состояний

Разрядность счетчика п равна числу Т-триггеров. Каждый входной импульс изменяет состояние счетчика, которое сохраняется до поступления следующего сигнала. Значения выходов триггеров счетчика Q,„ £)„_,,..., Q} отображают результат счета в принятой системе счисления. Логическая функция счетчика обозначается буквами СТ (counter). Список микроопераций счетчика включает предварительную установку в начальное состояние, инкремент или декремент хранимого слова, вы-

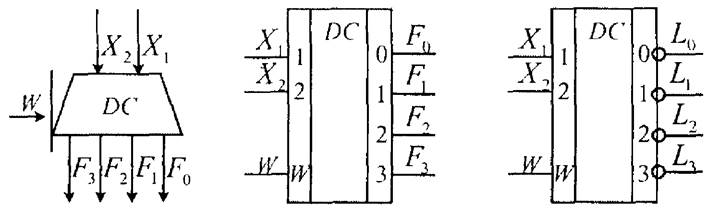

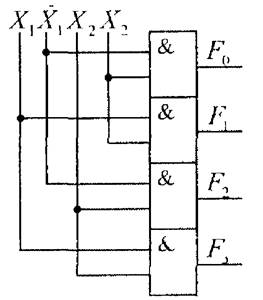

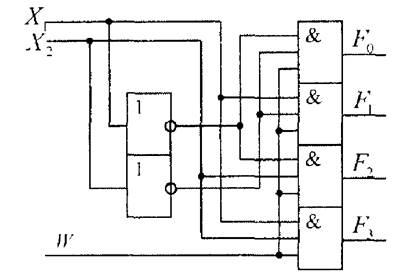

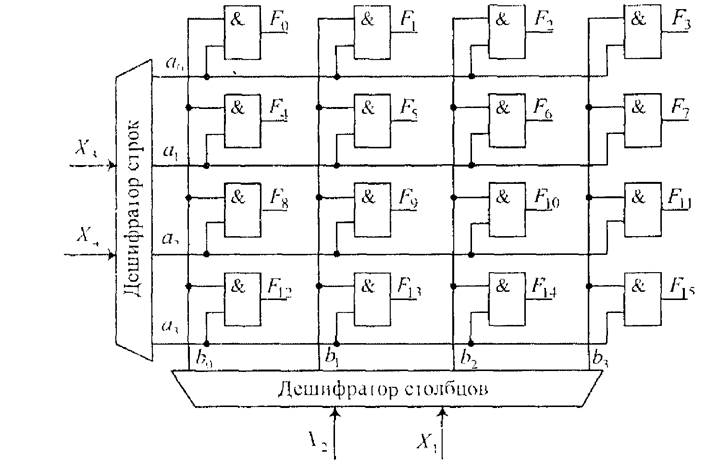

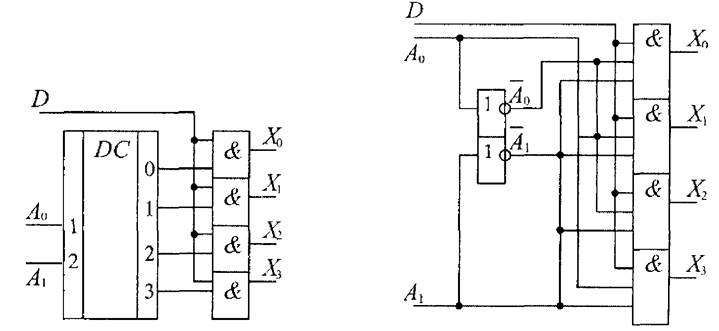

После подсчета семи импульсов на выходе трехразрядного счетчика устанавливается двоичный код QiQiQi = 111 (то есть максимальное значение или емкость счета), После прихода восьмого входного импульса U* трехразрядный суммирующий счетчик переключается в исходное нулевое состояние последовательно (асинхронно) во времени: вначале спадает напряжение на выходе Qu затем — на выходе Qi и т.д. С помощью импульса по входу сброса R счетчик возвращается в нулевое состояние в любой момент времени. Входные импульсы могут поступать на счетчик как периодически, так и произвольно распределенными во времени. Амплитуда и длительность счетных импульсов должны удовлетворять техническим требованиям для используемых серий микросхем. Счетчик является одним из основных функциональных узлов компьютера, а также различных цифровых управляющих и информационно-измерительных систем. Основное применение счетчиков: • образование последовательности адресов команд программы (счетчик команд или программный счетчик); • подсчет числа циклов при выполнении операций деления, умножения, сдвига (счетчик циклов); • получение сигналов микроопераций и синхронизации; аналого-цифровые преобразования и построение электронных таймеров (часов реального времени). Счётчики различаются по: • способу кодирования — позиционные и непозиционные; • модулю счета — двоичные, десятичные, с произвольным постоянным или переменным (программируемым) модулем; • направлению счета — простые (суммирующие, вычитающие) и реверсивные; • способу организации межразрядных связей — с последовательным, сквозным, параллельным и комбинированным переносами (заемом); • типу используемых триггеров — Т, JK, D в счетном режиме; Дешифратором называется функциональный узел компьютера, предназначенный для преобразования каждой комбинации входного двоичного кода в управляющий сигнал только на одном из своих выходов. В общем случае дешифратор имеет п однофазных входов (иногда 2п парафазных) и т ~ 2" выходов, где п — разрядность (длина) дешифрируемого кода. Дешифратор с максимально возможным числом выходов т ~ 2" называется полным. Функционирование полного дешифратора описывается системой логических выражений вида: Fo - Х„Хп-\ ■■■ Х2Х{; F \ = XпХ - х 2 X j F,„-1 = Х„... Х2Х], где X),..., Х„ — входные двоичные переменные; F0, F\,..., Fm_| — выходные логические функции, представляющие собой минтермы (конституенты 1) п переменных. Индекс функции Ft определяет номер выбранного выхода и соответствует десятичному эквиваленту входного кода. Выход, на котором появляется управляющий сигнал, называется активным. Если значение сигнала на активном выходе отображается лог. 1, то на остальных пассивных выходах устанавливается лог. 0. Двоичный код, включающий всегда только одну единицу, а остальные — нули, называется унитарным. Поэтому дешифратор является преобразователем входного позиционного кода в унитарный выходной код.

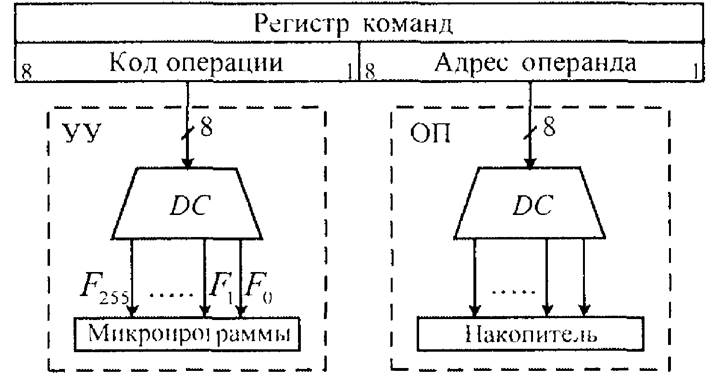

Виды дешифраторов, по: • способу структурной организации — одноступенчатые (линейные) и многоступенчатые, в том числе пирамидальные и прямоугольные (матричные); • формату входного кода — двоичные, двоично-десятичные; • разрядности дешифрируемого кода — 2, 3, п\ • форме подачи входного кода —с однофазными и парафазными входами; • количеству выходов — полные и неполные дешифраторы; • виду входных стробирующих сигналов — в прямом или инверсном значениях; • типу используемых логических элементов — И, НЕ, ИЛИ, НЕ И, НЕ ИЛИ и т. д. В компьютерах дешифраторы используют для выполнения следующих операций: • дешифрации кода операции, записанного в регистр команд процессора, что обеспечивает выбор требуемой микропрограммы; • преобразования кода адреса операнда в команде в управляющие сигналы выбора заданной ячейки памяти в процессе записи или чтения информации; • обеспечения визуализации на внешних устройствах; • реализации логических операций и построения мультиплексоров и демуль- типлексоров.

F0 - Х2 Х]; F] - Jfj; F2 Jf,; F3 -XJf,

F0 X, IV; F, = X,IV; F2=X2X, W\ F0 =X2Xl W

Прямоугольные дешифраторы

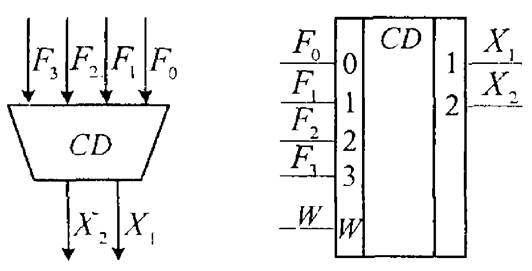

Шифратором называется функциональный узел компьютера, предназначенный для преобразования входного /77-разрядного унитарного кода в выходной n-разрядный двоичный позиционный код. Двоичные шифраторы выполняют функцию, обратную функции дешифратора. При активизации одной из входных линий дешифратора на его выходах формируется код, отображающий номер активного входа. Полный двоичный шифратор имеет т = 2" входов и п выходов.

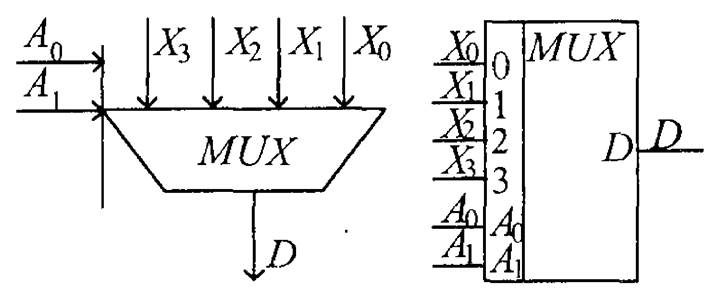

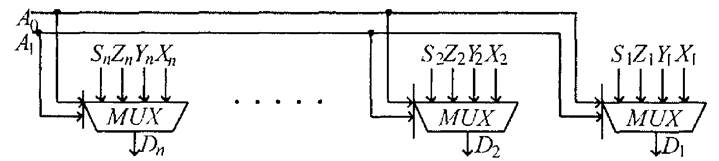

Приоритетный шифратор Одно из основных применений шифратора — ввод данных с клавиатуры, например, десятичных цифр. Нажатия клавиши с десятичной цифрой 0, 1,..., 9 должны приводить к передаче в цифровое устройство двоично-десятичного кода этой цифры. Для этого используется неполный шифратор "из 10 в 4". Шифраторы, которые при одновременном нажатии нескольких клавиш вырабатывают код только старшей цифры, называются приоритетными. Приоритетные шифраторы, предназначенные для поиска старшей (левой) единицы в слове и формирования на выходе двоичного номера искомого разряда, называются указателями старшей единицы. Их применяют в устройствах нормализации чисел с плавающей запятой, в системах с приоритетным обслуживанием запросов на прерывание работы компьютера. Мультиплексоры и демультиплексоры Мультиплексором называется функциональный узел компьютера, предназначенный для поочередной коммутации (переключения) информации от одного из п входов на общий выход. Номер конкретной входной линии, подключаемой к выходу в каждый такт машинного времени, определяется адресным кодом А0, Аи..., А,ч,. Связь между числом информационных п и адресных т входов определяется соотношением п = 2т. Таким образом, мультиплексор реализует управляемую передачу данных от нескольких входных линий в одну выходную.

Демультиплексором называется функциональный узел компьютера, предназначенный для коммутации (переключения) сигнала с одного информационного входа D на один из п информационных выходов. Номер выхода, на который в каждый такт машинного времени передается значение входного сигнала, определяется адресным кодом AQ,AbA2,...,Am-i- Адресные входы т и информационные выходы п

Хо =F0D = А, AqD\ X, = F\D = A, A0D\ Х2 = F2D = А, 4,D; Х3 = F3 D = А, А0 А

Мультиплексирование шин Мультиплексирование шин — это поочередное переключение шин (групп линий) от нескольких источников информации к одному приемнику.

Демультиплексирование шин Под демультиплексированием шин понимается поочередное переключение

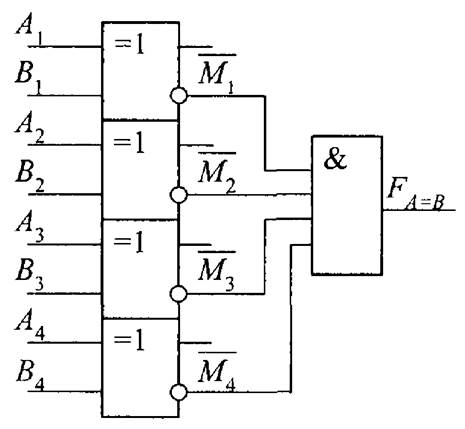

Схемы сравнения. Компараторы. Схемой сравнения (компаратором) называется функциональный узел компьютера, предназначенный для выработки признаков отношений между двоичными словами (числами). Признаки отношения используются как логические условия (осведомительные сигналы) в микропрограммах, командах передачи управления, а также в устройствах контроля и диагностики. После выполнения каждой команды в машине автоматически формируются признаки результатов операции. Эти признаки, называемые флагами (флажками), помещаются в специальный регистр флагов. К флагам обычно относят признаки нулевого результата, переполнения разрядной сетки, знак результата, наличие переносов из старшего разряда сумматора, четное или нечетное число единиц в результате и др. Многоразрядные двоичные слова равны, когда одновременно попарно равны все их разряды, то есть А(п) = В{п), если Al = В„ i = 1, 2,..., п.

Проверка результатов сложения

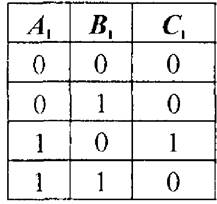

Контроль дешифрации методом повторного шифрования контроль четности

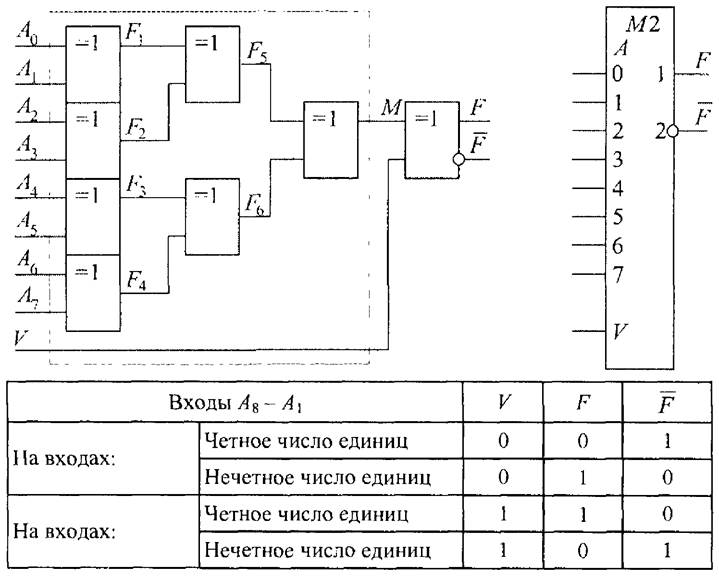

Преобразователи кодов Преобразователь прямого кода в обратный Хън i зи

Yi - Xm^i v ХгнХ( " ^зн ®

Преобразователь двоичных чисел в код Грея Изменяется только 1 разряд:

обратное преобразование кода Грея в прямой код: Ху —/] ©/2 ©/3 ©/4; Х,=/2©/3©/4; Х3=/3©/4; Х4-/4 Схемы для выполнения логических микроопераций Все компьютеры могут выполнять определенный список поразрядных логических операций. Для их реализации используют отдельный блок логических операций

Ei - код операции

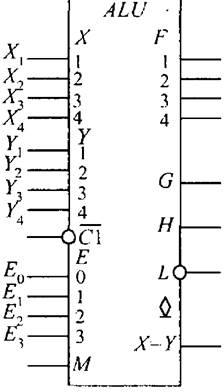

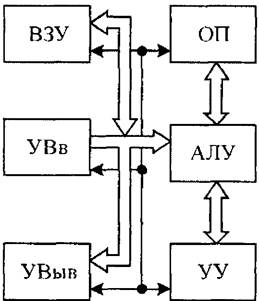

Микросхемы ALU • информационные входы для представления двух четырехразрядных операндов Xи У; • входы настройки Е3-Е0 для задания номера • вход М для задания типа микрооперации: М = 0 — арифметические, М = 1 — логиче- • вход переноса С1, необходимый только при исполнении арифметических микроопе- Архитектуры ЭВМ. ЭВМ архитектуры фон-Неймана Свойства и признаки: 1. Двоичная система счисления. 2. Единая память для программ и данных. Код команды ничем не отличается от кода данных. Фиксированная длина команд и данных. 3. Память последовательно-адресуемая. 4. Последовательное исполнение команд. Один вычислитель. Имеется счётчик команд. 5. Жесткая архитектура - неизменна аппаратная часть и система команд. Низкий уровень машинного языка. Гарвардские архитектуры: - Имеет раздельную память для программ и для данных. По количеству шин: - Трёхшинные ША, ШД, ШУ - Двухшинные ШАД, ШУ - Пятишинные Совокупность всех шин называют ОШ или ОМШ (общая магистральная шина). Классическая гарвардская архитектура: - Пять шин: ШАПП, ШАПД, ШДПП, ШДПД, ШР Модифицированная гарвардская архитектура: - Внешние шины ВШД, ВША, Внутренние шины: две ША, ШД, ШК (команд). Расширенная гарвардская архитектура: - раздельные шины и использование дополнительной кеш-памяти для хранения очередных команд. Гибридные модификации архитектуры фон Неймана: - имеется раздельная кэш-память для команд и данных, как в Гарвардской, но программная реализация по типу фон Неймана. По типу регистров: - Аккумуляторные - Безаккумуляторные ЭВМ включает в себя: • арифметико-логическое устройство • оперативную память (ОП); • средства хранения и ввода-вывода информации: внешние запоминающие устройства (ВЗУ); устройства ввода информации (УВв); устройства вывода информации (УВыв); все эти устройства называют внешними или периферий- • устройство управление (УУ). Вместе с АЛУ оно образует процессор. При наличии в машине нескольких процессоров выделяют центральный (ЦП). Арифметико-логическое устройство предназначено для выполнения арифметических и логических операций, предусмотренных системой команд данного компьютера. В состав АЛУ входят регистры и комбинационные схемы. Данные для обработки в АЛУ поступают из ОП и называются операндами. Результаты операций пересылаются в ОП или временно сохраняются в регистрах АЛУ.

Устройство управления (УУ) считывает и дешифрирует в соответствующей последовательности команды, формирует и подает управляющие сигналы для дру-

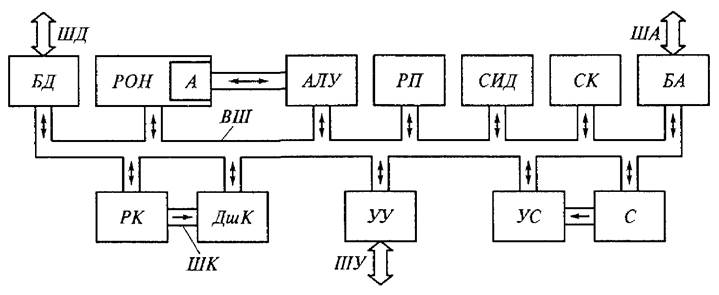

ША, ШД, ШУ - шины; ШК - шина команд БА, БД - буферные регистры адреса и данных РОН - регистры общего назначения; А -аккумулятор РК - регистр команд ДшК - дешифратор команд ВШ - внутренняя шина

РП - регистр признаков (или РФ - регистр флагов) СИД - схема инкремента и декремента СК - счётчик команд; УС - указатель стека; С - стек УУ - устройство управления

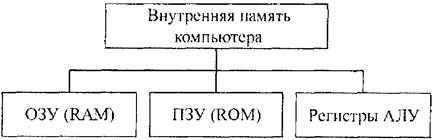

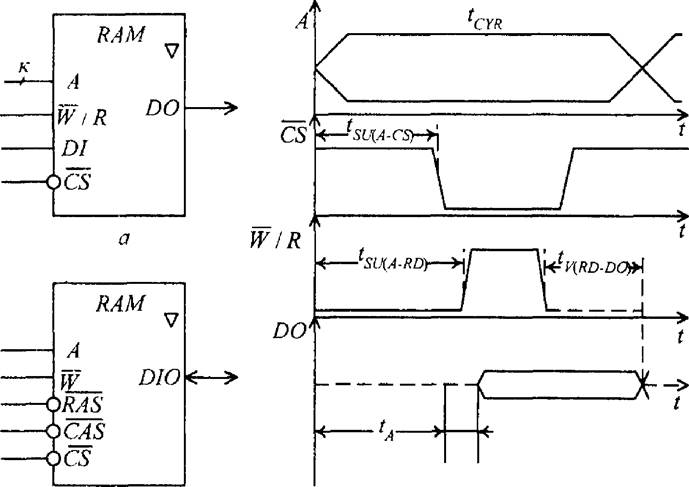

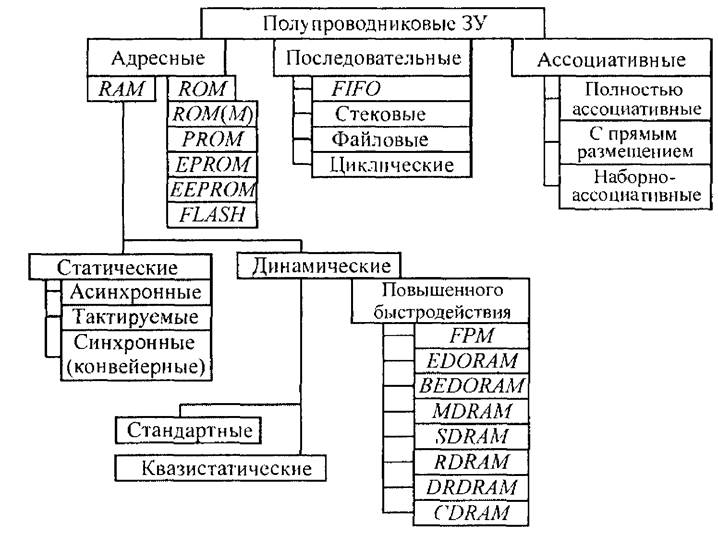

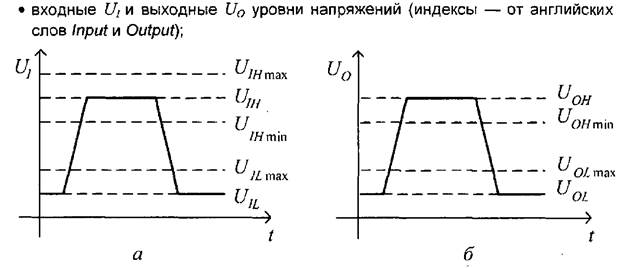

Внешняя память: - КНМЛ - НГМД - НЖМД - НОД - НМОД - ФСУ - ВПЗУ, «твёрдотельные диски». ВНУТРЕННИЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА - СОЗУ - сверхоперативное ОЗУ - в виде регистров внутри МП - кэш - для хранения быстрой копии текущей информации, внутри МП - ОЗУ - большие объёмы - ПЗУ - ППЗУ: ЭППЗУ, ПЗУ-УФС По физическому принципу: - полупроводниковая - магнитная (на сердечниках, магнитных доменах) - ёмкостная - лазерно-голографическая, и др. По способу хранения информации: - статическая - динамическая По структурной организации: - одномерная, двумерная, трёхмерная По способу доступа: - параллельный - последовательный По энергонезависимости: - энергонезависимая - энергозависимая Основные параметры памяти: Информационная ёмкость - макс. объём Удельная ёмкость - отношение информационной ёмкости к физическому объёму Удельная стоимость - денежная стоимость одной ячейки, Организация Ширина (величина) выборки Потребляемая мощность Быстродействие - время обращения, время выборки, записи, чтения Микросхемы памяти Сигналы: • А (Address) — входы адреса, разрядность которого к определяется соотношением к = logiM где N = Т — максимально возможное число данных (бит, байт, слов), которые хранятся в памяти и адресуются как единое целое; • DI (Data Input) — шина входных данных; • DO (Data Out) — шина выходных данных; __ • W / R (Write/Read) — сигнал записи данных при W / R - 0 или считывания п£И W / R = 1; • CS (Chip Select) или СЕ {Chip Enable) — сигнал разрешения при CS {СЕ) =0 или запрета, если CS {СЕ) = 1, работы данной микросхемы. В м/с динамической памяти для уменьшения количества выводов микросхем используется мультиплексирование ША: Адрес, например, A=Ai5i Ам, А0 делится на старший полуадрес АХ=Аis, А14,..., As и младший АУ=А7,А6, А0. Полуадреса подаются на одни и те же входы адреса микросхемы памяти. Подача полуадреса А, сопровождается сигналом RAS {Row Address Strobe), а полуадреса Ах — сигналом CAS {Column Address Strobe). Такой способ адресации уменьшает число выводов корпуса ИМС. Часто выводы DI и DO объединяются в общий вывод DIO.

Требования ко взаимному временному положению двух сигналов (А-В) задают следующими параметрами: • временем предварительной установки tsu сигнала А относительно сигнала В, то есть интервалом между начальными моментами обоих сигналов; • временем удержания (щл-в) — интервалом времени между началом сигнала А и окончанием сигнала В; • временем хранения tV{A_B) — интервалом между окончанием сигналов Л и В. Длительность сигналов обозначается как tw (Width — ширина). Для ЗУ характерна следующая последовательность сигналов во времени вначале адрес, затем выбор микросхемы CS, затем строб записи- чтения W / R. Индексом A (Access) обозначают интервалы времени от появления управляющего сигнала до появления данных на выходе СПОСОБЫ ДОСТУПА к ячейкам памяти: - адресные - последовательные - ассоциативные

Запоминающие устройства RAM подразделяются на статические SRAM (Static RAM) и динамические DRAM (Dynamic RAM). В статических RAM элементами памяти являются триггеры. Они хранят свое состояние, пока схема имеет напряжение питания и новые данные не записываются. В динамических RAM данные хранятся в виде зарядов конденсаторов, создаваемых компонентами МОП-транзисторов. Саморазряд конденсаторов приводит к разрушению данных, поэтому они периодически (каждые 2-30 мс) должны регенерироваться. Однако плотность упаковки динамических ЭП превышает в 4-5 раз этот же показатель для статических RAM. Регенерация данных осуществляется с помощью специальных контролле

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-06; просмотров: 752; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.214 (0.018 с.) |

(Исключающее ИЛИ)

(Исключающее ИЛИ)