Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Команды суперскалярных CISC-микропроцессоровСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

• Команды пересылки данных (всего около 40) позволяют передавать константы или переменные между регистрами и памятью, а также портами ввода-вывода. • Команды двоичной арифметики (около 15) выполняют все арифметические действия с байтами, словами и двойными словами. • Команды десятичной арифметики (около 10) позволяют оперировать с неупакованными и упакованными двоично-десятичными данными. Операции с этими числами требуют применения команд коррекции форматов. • Команды логических операций (4) реализуют все функции булевой алгебры с байтами, словами и двойными словами. • Логические и циклические сдвиги (всего 10) выполняют над содержимым регистров или операндов в памяти. Число позиций, на которое осуществляется сдвиг, можно задавать операндом и другими способами. • Команды обработки битов и байтов (26) позволяют проверять и устанавливать значение указанного операнда или бита. • Команды передачи управления (около 30) осуществляются с помощью команд безусловных и условных переходов. Команда вызова процедур CALL передает управление в точку перехода, при этом адрес следующей за ней команды хранится в стеке. • Строковые операции (24) выполняются с операндами в памяти. • Операции с флажками (всего 13) позволяют изменять значения отдельных флажков, а также сохранять их значения в стеке и восстанавливать эти значения. • Команды загрузки указателей (5) обеспечивают загрузку указателей из памяти в регистр общего назначения и соответствующий сегментный регистр. • Команды математического сопроцессора FPU (92) выполняют операции с действительными, целыми и двоично-десятичными числами, представленными в формате с плавающей запятой. • Системные команды (32) — это операции управления защитой, загрузкой и хранением регистров дескрипторов, проверки привилегий, тестирования, управления кэшированием памяти, останова процессора и др. Характеристики CISC-процессоров Поколение суперскалярных C/SC-микропроцессоров началось с процессора Pentium и характеризуется: • большим количеством сложных машинных команд различной разрядности и преимущественно двухоперандного формата (у команд RISC — трехопе- рандный формат); • наличием предвыборки, конвейера команд и динамического прогнозирования условных переходов; • большим числом способов адресации; • использованием всего восьми регистров общего назначения (в RISC — как минимум 32); • широким использованием микрокоманд; • раздельными кэшами команд и данных и их заполнением в пакетном режиме; • встроенным сопроцессором FPU, Архитектура Pentium является оптимизированной, поскольку имеет свойства современных R/SC-микропроцессоров: • аппаратную реализацию простых команд, выполняемых за один машинный такт; • суперскалярность и 64-разрядную внешнюю шину данных; • приблизительно одинаковую производительность конвейерного FPU для операций с одинарной, двойной и расширенной точностью; • прогнозирование переходов, наличие 64- и 256-разрядных шин на кристалле; • эффективные средства обеспечения многопроцессорности и др. Таким образом, Pentium относится к C/SC-архитектуре, однако имеет много свойств R/SC-микропроцессоров. Развитие процессоров Pentium • возможность выполнения команд не в порядке их размещения в программе; • встроенный вторичный кэш объемом до 2 Мбайт; • появление двух независимых внутренних шин: одну — для связи с памятью, вторую — для обмена с вторичным кэшем; • управление энергопотреблением; • наличие встроенных средств контроля операций по модулю два; • расширение возможностей построения многопроцессорных МПС с симметричной архитектурой. Развитие современных микропроцессоров определяется конкуренцией между фирмами, развивающими направления CISC- и RISC-архитектур. Суперскалярные микропроцессоры с R/SC- архитектурой R/SC-архитектура является основой современных рабочих станций и серверов. Е? общем R/SC-архитектура имеет следующие черты: • Сравнительно небольшой (сокращенный) набор команд, которые больше всего применяются в прикладных программах; • трехоперандный формат команд с длиной операндов 32 или 64 разряда, • мало способов адресации; • большой регистровый файл (16, 32, 64 и более регистров); • аппаратная реализация простых команд за один машинный такт; • обращение к памяти с помощью специальных команд загрузки- запоминания, обрабатывающих группу регистров; • широкое использование регистровых окон при переключениях задач; • суперскалярность — за один машинный такт выполняются две и более команд; • предвидение переходов; • наличие средств поддержки многопроцессорности. В целом структура RISC-процессоров содержит: • два и более исполнительных устройств, в том числе с плавающей запятой; • раздельные кэши команд и данных; • блок прогнозирования переходов; • интерфейс с 64-разрядной внешней шиной данных. Разработкой и промышленным выпуском RISC-процессоров занимается ряд известных фирм. Они присваивают своим изделиям собственные названия архитектур, например: • POWER— фирма IBM, PowerPC — фирмы Motorola, Apple и IBM; • Alpha — фирма DEC; • MIPS — фирма MIPS Technology и др. Два направления построения ЭВМ: • с полным набором сложных и многоформатных команд CISC (Complex • с ограниченным набором команд RISC (Reduced Instruction Set Computer); все команды работают с операндами, расположенными в регистрах АЛУ, CISC - универсальные, RISC - узкоспециализированные, зато намного быстрее Организация аппаратных средств ЭВМ Современные МПС имеют магистрально-модульную организацию, основанную на принципах агрегирования и унификации. Модульность (агрегирование) — это разделение МПС на простые функционально и конструктивно законченные блоки, называемые модулями, например: модуль микропроцессора, модуль памяти и т.д. Унификация состоит в оптимизации состава модулей, связей между ними и в их конструктивных оформлениях. Связь устройств МПС одного с другим осуществляют с помощью сопряжений, называемых интерфейсами. Интерфейс — это совокупность информационно- логических и конструктивных средств и требований (правил), которые обеспечивают оптимальный алгоритм взаимодействия всех модулей МПС. Интерфейсы классифицируют по следующим основным признакам. По функциональному назначению интерфейсы подразделяются на такие типы: • внутренние — внутриплатные, межплатные и системные; • внешние — для периферийных устройств, для локальных сетей

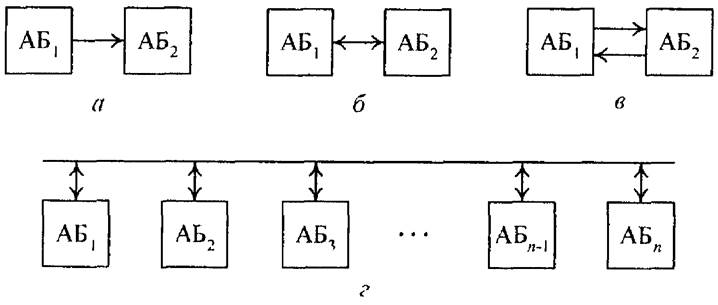

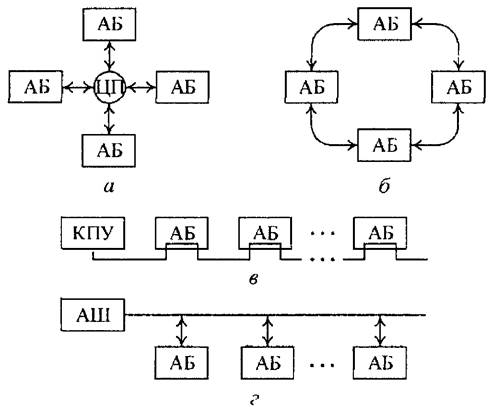

Все модули, подключаемые к интерфейсу, называются абонентами. По структуре связей между абонентами, интерфейсы могут быть: радиальные, кольцевые, каскадные, магистральные:

По способу передачи информации во времени различают следующие интерфейсы: • синхронные — с фиксированной длительностью операций обмена; • асинхронные — с переменной длительностью операций обмена; • синхронно-асинхронные — с комбинированным соединением двух способов. По разрядности передаваемых данных различают интерфейсы с параллельным (словами), последовательным (битами) и параллельно-последовательным обменами. Интерфейсы реализуются контроллерами интерфейсов. Программируемый последовательный интерфейс содержит передатчик (transmitter) и приемник (receiver). Передатчик получает от микропроцессора по ШД данные (data) в параллельном коде и передает их последовательно по линии TXD в терминал. Приемник получает от терминала по линии RXD данные в последовательном коде, преобразовывает их в параллельные слова и пересылает по ШД в микропроцессор. Система обмена может быть асинхронной или синхронной, симплексной, полудуплексной или дуплексной.

Примеры: RS-232, «Токовая петля»

СТБ - старт-бит (=0), К - контроль чётности, СБ - стоп-бит (=1), СБ может быть 1, 1,5 или 2.

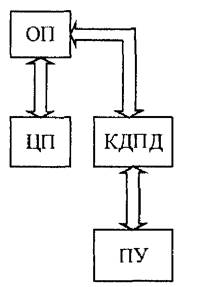

Синхросимвол 1 Синхросимвол 2 Данные Стартовых и стоповых битов - нет. Применяются синхросигналы в виде части посылки или по отдельной линии. Виды управляемого обмена информацией: - синхронный, асинхронный - последовательный код, параллельный код - со стробированием, без стробирования - с контролем чётности, без контроля - с сигналами синхронизации/квитирования ПДП Прямой доступ к памяти (ПДП) используют для быстрого обмена массивами информации между основной памятью и периферией. При этом процессор (микропроцессор) освобождается от непосредственного управления операциями ввода- вывода. Управление ПДП осуществляет контроллер ПДП (КПДП). Перед началом обмена процессор пересылает в КПДП следующую информацию: • начальный адрес области памяти, которая принимает участие в обмене; • направление операции обмена — ввода или вывода; • количество байтов, подлежащих передаче.

Режим прямого доступа к памяти обеспечивает непосредственный обмен информацией между ОП МПС и внешними быстродействующими устройствами, например, НГМД. Реализация такого обмена достигается с помощью БИС программируемых КПДП. Подключение внешнего оборудования. Периферийные устройства подключаются к компьютеру с помощью специализированных адаптеров или контроллеров. Адаптер — это средство сопряжения некоторого внешнего устройства с определенной шиной МПС. Контроллер также выполняет подобные функции, однако он способен на самостоятельные действия после получения команд от машины. Сложный контроллер может иметь и собственный процессор. Сегодня часто термины "адаптер" и "контроллер" считают почти синонимами. Все внешние интерфейсы имеют в своем составе адаптер или контроллер. Прерывания Во время выполнения текущей (фоновой) программы в компьютере возникают заранее неизвестные события, которые требуют мгновенной реакции на них (авария в системе, готовность ПУ к передаче данных, деление на нуль и др.). Реакция состоит в прерывании фоновой программы, переходе к подпрограмме обслуживания данного события и возврате программы в предыдущее состояние. Каждое событие, требующее прерывания, сопровождается сигналом — запросом прерывания. Прерывания — важная архитектурная особенность машины, позволяющая эффективно организовать работу процессора при наличии нескольких параллельных процессов. Система прерываний: - аппаратные, программные - приоритет прерываний, - глубина уровней прерывания - работа стека при прерываниях Для технической реализации прерываний используют программируемые кон троллеры прерываний (ПКП). Состав ПКП:

РУС <8>

Блок управления Ж

CAS0<r

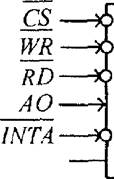

• двунаправленный восьмиразрядный буфер данных БД; • блок управления (входы CS, WR, RD, AD, INTA, INT)\ • регистры запросов прерываний IRR (входы IR1-IRQ), управляющих слов РУС, состояния ISR, маскирования IMR\ • блок каскадирования (вход SP, двунаправленные выходы CAS3-CAS0); • блок обработки приоритетов (БОП). Программируемый контроллер прерываний воспринимает запросы на прерывания от восьми ПУ; за счет каскадирования с помощью выходов CAS3-CAS0 число входов для запросов может увеличиваться до 64. Запросы, поступающие на входы IR7-IR0, фиксируются в регистре запросов прерывания IRR. Блок обработки приоритетов определяет наиболее приоритетный запрос Блок управления формирует сигнал запроса прерывания INT, который поступает на такой же вход микропроцессора. Если в микропроцессоре прерывание разрешено, то он отвечает контроллеру сигналом INTA, поступающим на такой же вход ПКП. В результате на ШД от КПК видается сначала первый байт — код команды CALL (переход на подпрограмму обработки прерывания), а затем второй и третий байты, определяющие адрес подпрограммы. После этого разряд регистра запросов IRR, на который поступил запрос с высшим приоритетом, обнуляется и устанавливается единица в соответствующем разряде регистра состояний ISR. С помощью загрузки управляющих слов инициализации ICW в режиме настройки и операционных слов OCW при обслуживании запросов ПКП может программироваться на такие режимы обслуживания прерываний: Запросы, поступающие на входы IR1-IRQ, фиксируются в регистре запросов прерывания IRR. Блок обработки приоритетов определяет наиболее приоритетный запрос Блок управления формирует сигнал запроса прерывания INT, который поступает на такой же вход микропроцессора. Если в микропроцессоре прерывание разрешено, то он отвечает контроллеру сигналом INTA, поступающим на такой же вход ПКП. В результате на ШД от КПК видается сначала первый байт — код команды CALL (переход на подпрограмму обработки прерывания), а затем второй и третий байты, определяющие адрес подпрограммы. После этого разряд регистра запросов IRR, на который поступил запрос с высшим приоритетом, обнуляется и устанавливается единица в соответствующем разряде регистра состояний JSR. С помощью загрузки управляющих слов инициализации ICW в режиме настройки и операционных слов OCW при обслуживании запросов ПКП может программироваться на такие режимы обслуживания прерываний: • приоритеты внешних устройств фиксированы; • циклический сдвиг приоритетов; • специального маскирования; • последовательного опроса ПКП. В режиме с фиксированными (неизменными) приоритетами вход IRO имеет наивысший приоритет, а вход IR7 — самый низкий. Программируемый контроллер прерываний всегда обслуживает запросы с высшим приоритетом. Если во время обслуживания одного из запросов приходит запрос высшего приоритета, то ПКП переключается на его обслуживание. При циклическом сдвиге приоритеты могут динамически изменяться: входу после обслуживания присваивается низший приоритет В режиме специального маскирования разрешаются прерывания на входах с меньшими приоритетами, чем запрос, обслуживаемый в данное время. В режиме последовательного опроса микропроцессор с помощью ПКП последовательно опрашивает источники запросов. Программируемый таймер Программируемый таймер (ПТ) предназначен для организации работы МПС в режиме реального времени и позволяет формировать сигналы с разными временными интервалами и частотными характеристиками. Монтаж элементов ЭВМ Печатные платы — это составные части конструкции компьютеров и радиоэлектронной аппаратуры. Платы состоят из плоских проводников в виде участков металлизированного покрытия, размещенных на диэлектрической основе. Проводники на плате соединяют печатные или навесные электрорадиоэлементы (резисторы, конденсаторы, индуктивность) и транзисторы, реле, микросхемы и др. Печатные платы обеспечивают: • увеличение плотности монтажных соединений и возможность микроминиатюризации изделий; • получение печатных проводников, элементов и экранирующих поверхностей в одном технологическом цикле; • гарантированную стабильность и повторение электрических характеристик; • повышенную устойчивость к механическим и климатическим воздействиям; • унификацию и стандартизацию конструктивных и технологических решений; • увеличение надежности изделий; • возможность комплексной автоматизации проектирования и монтажно- сборочных и контрольно-регулирующих работ; • снижение трудоемкости, материалоемкости и себестоимости. К недостаткам печатных плат относят сложность внесения изменений в схему и ограниченную ремонтопригодность. По количеству слоёв: - односторонние - двухсторонние - многослойные - гибкие Материалы: текстолит, стеклотекстолит, гетинакс. Для изготовления основы печатной платы используют фольгированные и не- фольгированные диэлектрики — гетинакс, стеклоткань, фторопласт, полистирол, керамические и металлические (с поверхностным изоляционным слоем) материалы. Фольгированные материалы — это многослойные прессованные пластики из электроизоляционной бумаги или стеклоткани, пропитанные искусственной смолой. Они покрыты с одной или двух сторон электролитической фольгой толщиной 18; 35 и 50 мкм. Фольгу изготовляют из меди высокой чистоты (содержание примесей не превышает 0,05%). Медь имеет высокую электропроводность, она относительно устойчива к коррозии, хотя и требует защитного покрытия. Для печатного монтажа допустимое значение тока выбирают: дпя фольги 100...250 А/мм2, для гальванической меди 60...100 А/мм2. Для производства печатных кабелей используют армированные фольгирован- ные пленки из фторопласта. Керамические платы могут работать в диапазоне температур 20...700°С. Их изготовляют из минерального сырья (например, кварцевого песка) прессовкой, литьем под давлением или отливанием пленок. Металлические платы используют в изделиях с большой токовой нагрузкой. В качестве основы используют алюминий или сплавы железа с никелем. Изоляционный слой на поверхности алюминия получают анодным оксидированием с толщиной от десятков до сотен микрон и сопротивлением изоляции Ю9...Ю10 Ом. Толщину проводника берут 18; 35 и 50 мкм. По плотности проводящего рисунка печатные платы подразделяют на пять классов: • первый класс характеризуется наименьшей плотностью проводящего рисунка и шириной проводника и пробелов более 0,75 мм; • пятый класс имеет наибольшую плотность рисунка и ширину проводника и пробелов в пределах 0,1 мм. Поскольку печатный проводник имеет малую массу, то сила его сцепления с основой достаточна, чтобы выдержать действующие на проводнике знакопеременные механические перегрузки до A0q в диапазоне частот 4...200 Гц. Режимы работы Вычислительных машин:

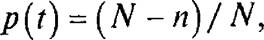

В режимах: • однопрограммном — каждая программа отдельно загружается в ОП и выполняется до получения результата; • многопрограммном — в память загружается несколько программ; когда выполнение одной из программ останавливается из-за необходимости обратиться к ПУ, то машина переключается на выполнение другой программы; • пакетном — в ВЗУ формируется пакет задач, которые затем считываются в ОП группами и выполняются в многопрограммном режиме; • распределения времени (коллективного пользования) — доступ к компьютеру пользователей с помощью собственного терминала; • реального времени — обеспечивается взаимодействие компьютера с внешними объектами в темпе, который требует быстродействие объекта. Основные характеристики ЭВМ: Пиковая производительность - количество операций типа «регистр-регистр» в секунду, MIPS - million instruction per second Типичная (характерная) производительность - количество операций с плавающей точкой в секунду, FLOPS - floating point operation per second. MFLOPS - миллионы FLOPS Системная производительность - в условных сравнительных единицах, в зависимости от тестовой программы («Бенчмарки») Надёжность - определяется вероятностью отказа устройства за определённый промежуток времени. Pit) к

t

N - общее количество испытанных устройств, n - количество вышедших из строя за определённое время.

I - приработка, выход из строя из-за брака;

II - нормальная эксплуатация III - старение, износ. УВВ: - УВв: - клавиатура - сканеры (ручные, протяжные, планшетные, проекционные) - дигитайзер - манипуляторы (мышь, джойстик, трекбол, сенсорная панель, световое перо) - микрофон, устройства ввода и преобразования аналоговых сигналов - внешние накопители - фото/видеокамеры - УВыв: - принтеры (матричные, термические, пьезо-струйные, термоструйные, сублимационные (термокопировальные), твёрдочернильные, лазерные, светодиодные) - мониторы (дисплеи): ЭЛТ, ЖК, люминесцентные, плазменные, электромеханические, мозаичные - проекторы - графопостроители (плоттеры) - звуковые устройства, устройства преобразования и вывода аналоговых сигналов Связь между функциональными частями машины осуществляют с помощью интерфейса — совокупности шин, сигналов, вспомогательных микросхем и алгоритмов, предназначенных для обмена информацией между устройствами компьютера

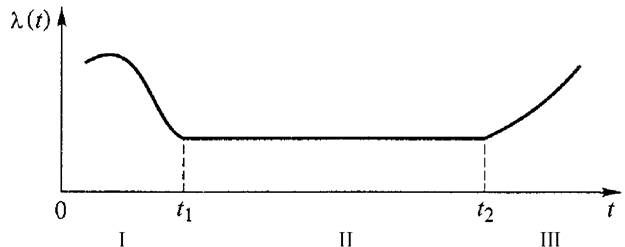

76 дорожек - на 8-дюйм. дисках, из них 75-я и 76-я - резервные 40 или 80 дорожек - на 5 и 3,5-дюйм. дисках. Резервных нет. 0 дорожка - служебная Запись с одинарной плотностью осуществляется методом частотной модуляции (ЧМ-метод), а заЛись с двойной плотностью— методом модифицированной частотной модуляции (МЧМ-метод).

[1] выходы: результата микрооперации FA-FX, последовательного переноса Z., генерации G, транзита Я, а также выход с открытым коллектором от внутреннего компаратора для выработки признака равенства операн-

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-06; просмотров: 494; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.147.42.207 (0.013 с.) |