Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Выборочное присваивание сигналуСодержание книги Поиск на нашем сайте

Последним типом параллельного присваивания сигналу является выборочное присваивание, которое имеет следующий синтаксис:

with choice_expression select target <= { expression when choices, } expression when choices;

choice { | choice }

Каждый выбор может быть либо статическим выражением (таким, как 3), либо статическим диапазоном (таким, как 1 to 3). Тип choice_expression определяет тип каждого выбора. Каждое значение из диапазона choice_expression должно покрываться одним выбором choice. Последний choice может быть others, при этом согласовываются все оставшиеся (невыбранные) значения из диапазона выражения choice_expression. Выбор others, если таковой присутствует, согласовывает choice_expression только в том случае, если ни один из других выборов не совпадает. Оператор with..select вычисляет выражение choice_expression и сравнивает это значение со значением каждого выбора choice. Предложение when совпавшего значения choice присваивает значение своего выражения expression сигналу target. На выборы накладываются следующие ограничения: Никакие два выбора не могут перекрываться. Если выбор others не присутствует, то все возможные значения choice_expression должны быть перекрыты соответствующим набором выборов. В примере 28 показан сигнал Z, присваиваемый из A, B, C или D. Назначение зависит от текущего значения CONTROL.

Пример 28. Выборочное присваивание сигналу ... signal A, B, C, D, Z: BIT; signal CONTROL: bit_vector(1 down to 0); ... with CONTROL select Z <= A when "00", B when "01", C when "10", D when "11"; ...

В примере 29 показан процесс, эквивалентный выборочному присваиванию сигналу из примера 28.

Пример 29. Процесс, эквивалентный выборочному присваиванию сигналу ... process(CONTROL, A, B, C, D) begin case CONTROL is when 0 => Z <= A; when 1 => Z <= B; when 2 => Z <= C; when 3 => Z <= D; end case; end process; ...

4. Ход работы

4.1. С помощью любого текстового редактора и на основе объекта, архитектуры и параллельных свойств конструкций языка VHDL создать простейшее описание вашего цифрового устройства в соответствии с вариантом и использовать его свойства как часть функциональных свойств более сложного дискретного устройства. Для предупреждения ошибок необходимо, чтобы файл имел расширение *.vhd.

4.2. Создать проект в отладчике FPGA Express и подключить к нему набранный файл. 4.3. После корректного подключения файла описания создать с помощью FPGA Express отчет по вашему проекту. 4.4. Синтезировать модель вашего цифрового устройства.

4.6. Вывести список цепей оптимального варианта вашего устройства. 4.7. Создать проект в системе моделирования ModelSim и подключить к нему набранный и отлаженный в FPGA Express файл. 4.8. После корректного подключения файла описания сделать полный анализ вашего устройства в соответствии с вашим вариантом.

5. Указания по оформлению отчета и Контрольные вопросы

5.1. Отчет по лабораторной работе должен содержать: - наименование; - цель работы; - используемое оборудование; - теоретическую часть; - описание последовательности действий при отладке и моделировании вашего варианта; - распечатку временных диаграмм и таблиц истинности по проекту; - распечатку вашего исходного файла; - выводы по проделанной работе.

5.2. Контрольные вопросы к лабораторной работе

1. Какова необходимость использования параллельных процессов? 2. Что такое оператор block и каковы его функции? 3. Возможно ли параллельное присваивание сигналов и выполнения процедур?

Cписок литературы

1. Бибило П.Н. Основы языка VHDL. – М.: Солон-Р, 2000. – 200 с. 2. Армстронг Дж.Р. Моделирование цифровых систем на языке VHDL /Пер с англ. – М.: Мир, 1992. – 175 с. 3. Цифровые устройства на программируемых БИС с матричной структурой. С.И. Баранов, В.А. Скляров – М.: Радио и связь, 1986. – 279 с. 4. Бибило П.Н. Кремниевая компиляция заказных СБИС. –Минск: Ин-т техн. кибернетики АН Беларуси, 1996. – 268 с. 5. Закревский А.Д. Параллельные алгоритмы логического управления. – Минск: Ин-т техн. кибернетики НАН Беларуси, 1999. – 202 с. 6. Программируемые логические интегральные схемы и их применение. В.В. Соловьев, А.Г. Васильев; – Минск: Беларуская наука, 1998. – 270 с.

ПРИЛОЖЕНИЕ 1

Варианты заданий на лабораторную работу

Вариант 1. Двухразрядный умножитель

Рассмотрим двухразрядный умножитель mult_2. На вход данной схемы поступают сигналы r1, r0, sl, s0. Сигналы rl, r0 интерпретируются как двухразрядное целое число r=(rl,r0), сигналы s 1, s0 - как двухразрядное целое число s=(s I,s0).

Выходные сигналы в t3, t2, tl, t0 представляют собой разряды числа t=(t3, t2, tl, t0) - произведения чисел s, г: (t3, t2, tl, t0) = (rl,r0)x(sl,s0). В схему входят элементы двух типов " add1 и and2. Элемент and2 представляет собой логический элемент И -двухвходовый конъюнктор. Заметим, что на языке VHDL знак & употребляется не для обозначения логической операции "И" (конъюнкции), а для операции конкатенации векторов. Оператором логической конъюнкции служит оператор and, поэтому описание функции элемента and2 на языке VHDL выглядит следующим образом: y<=xl and х2; где х1, х2 - имена входных сигналов, у - имя выходного сигнала, <=" оператор назначения сигнала. Элемент addl представляет собой одноразрядный полусумматор, функционирование которого описывается таблицей истинности (табл. 1)

Таблица 1

В данном случае b1, b2 интерпретируютсякак одноразрядные числа, sl - сумма, с - перенос в следующий разряд. В привычной математической записи булевы функции с, s1 могут быть представлены следующим образом: s1 = b1 Å b2 =

В языке VHDL функционирование элемента addl записывается следующим образом: sl <= ((bl and (not b2)) or (not b1) and b2)); c<=bl and b2; где or - оператор логической дизъюнкции; and - оператор логической конъюнкции; uot - оператор отрицания. Итак, в дерево проекта схема умножителя, которую назовем mult_2, входят элемент and2 и подсхема addl. Если использовать логические элементы ог2 (двухвходовый дизъюнктор), inv (инвертор) и and2 (двухвходовый конъюнктор) для реализации подсхемы addl, то дерево проекта будет трехуровневым. Элементы and2, ог2, inv являются частями проекта. Части проекта не имеют составных частей и называются примитивам проекта. Примитив описывается только на поведенческом уровне. Объектами проекта для двухразрядного умножителя являются mult_2, addl, and2. Обозначение корня дерева (mult__2) является именем проекта. Каждый объект проекта имеет два различных типа описаний: -описание объекта "в целом" (entity); -описание архитектуры объекта (architecture). Упрощенно можно сказать, что описание объекта "в целом" состоит из имени объекта и описания портов (входов, выходов объекта. Описание объекта "в целом" в языке VHDL носит названии "интерфейс" объекта. Чтобы отличать один объект проекта от другого, термин entity будет пониматься иногда и как объект проекта. Для сигналов, подаваемых, снимаемых с портов, указывается вид (режим, направление) сигнала: входной (in), выходной (out) и его тип. Например, простейшее описание объекта проекта and2 имеет вид

entity and2 is -- декларация имени объекта проекта port (x1,x2: in BIT; — декларация входных портов у; out BIT); - декларация выходного порта end and2; architecture functional of and2 is - декларация архитектуры Begin у <= xl and x2; -описание функции объекта. end functional;

В тексте данной программы имеются комментарии. Комментарий начинается двумя смежными дефисами и продолжается до конца строки. В данном примере, ВIT - это тип сигнала. Архитектурное тело может определять поведение объекта проекта непосредственно (быть примитивом), либо представлять собой структурную декомпозицию на более простые компоненты. Описание объекта проекта add1 выглядит следующим образом:

entity add1 is port (b1,b2: in BIT; cl,sl: out BIT); end add1;

architecture struct_1 of add1 is Begin sl <= ((b1 and (not b2)) or ((not b1) and b2)); cl<=b1 and b2; end struct_l;

Таким образом, описание объекта проекта mult_2 можно представить следующим образом:

library IEEE; library synopsys; use IEEE.std_logic_1164.all; use synopsys.attributes.all; entity add1 is port (b1,b2: in BIT; cl,sl: out BIT); end add1;

architecture struct_1 of add1 is begin sl <= ((b1 and (not b2)) or ((not b1) and b2)); cl<=b1 and b2; end struct_1;

entity mult_2 is port(s1,s0,r1,r0:in BIT; t3,t2,t1,t0: out BIT); end mult_2;

architecture structure of mult_2 is

component add1 port(b1,b2: in BIT; cl,sl: out BIT); end component;

signal p1,p2,p3,p4: BIT;

begin t0 <= r0 and s0; -- элемент е1_1 p2 <= r0 and s1; -- элемент е1_3 p1 <= r1 and s0; -- элемент е1_2 p4 <= r1 and s1; -- элемент el_4 circl: add1 port map(p1,p2,p3,t1); circ2: add1 port map(p3,p4,t3,t2); end structure;

В описании архитектуры объявляются (декларируются) две подсхемы (компоненты). После ключевого слова begin приводятся экземпляры описаний. Каждый экземпляр имеет уникальную метку (circl, circ2 - метки).Каждый экземпляр имеет карту портов (port map). Карта портов отражает связь между входами, выходами описаний компонента и экземплярами компонента. Заметим, что в данном описании мы использовали понятие компоненты (подсхемы) для addl, в то время как логические элементы "И" схемы мы описали на функциональном уровне, не используя понятие компоненты. Возможность проведения таких смешанных описаний является важной полезной особенностью языка VHDL. Данная гибкость весьма удобна при проектировании на начальных этапах, когда важно получить точное алгоритмическое описание, не вдаваясь в детали структурной организации некоторых частей проекта.

Вариант 2. Двухразрядный сумматор

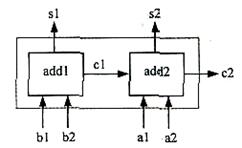

a) б)

(al,bl)+(a2,b2)=(c2,s2,sl): а) - условное обозначение; б) - схема в виде каскадного соединения одноразрядного полусумматора addl и одноразрядного сумматора add2

Таблица 2

В дерево проекта для подсхемы adder_2 входят подсхемы addl, add2, a VHDL описание имеет вид library IEEE; library synopsys; use IEEE.std_logic_1164.all;

use synopsys.attributes.all;

entity add1 is port (b1,b2: in BIT; cl,sl: out BIT); end add1;

architecture struct_1 of add1 is begin sl <= ((b1 and (not b2)) or ((not b1) and b2)); cl<=b1 and b2; end struct_1;

entity add2 is port (a1,a2, cr1: in BIT; cr,s2: out BIT); end add2;

architecture struct_1 of add2 is begin s2 <=((not a1) and (not a2) and cr1) or ((not a1) and a2 and (not cr1)) or (a1 and (not a2) and (not cr1)) or (a1 and a2 and cr1); cr <=((not a1) and a2 and (not cr1)) or (a1 and (not a2) and cr1) or (a1 and a2 and (not cr1)) or (a1 and a2 and cr1); end struct_1;

entity adder_2 is port (a1, b1, a2, b2: in BIT; c2,s2,sl: out BIT); end adder_2;

architecture structure of adder_2 is component addl port (bl, b2: in BIT; cl, sl: out BIT); end component;

component add2 port (a1,a2, c1: in BIT; c2,s2: out BIT); end component;

signal c: BIT; begin circl: addl port map (b1, b2, sl, c); circ2:add2 port map (c, a1, a2, c2, s2); end structure;

Вариант 3. Цифровая система S

Цифровая система S реализует следующий алгоритм. На входные полюсы системы S подаются два двухразрядных числа а=(а2,а1), b==(b2,b1), где а2, b2 - старшие разряды чисел,а b соответственно их- управляющий сигнал. Если х=1, система S должна перемножить числа а, Ь и выдать четырехразрядное число d==(d4,d3,d2,dl), где d= axb. Если х=0, то числа а, Ь должны быть сложены, при этом в разряде d4 всегда должен быть нуль, в разряде d3 - перенос с2, в разряде d2 - старший разряд суммы s2, в разряде dl - младший разряд суммы sl. Предполагается, что (a2,a1)+(b2,b1)=(c2,s2,s1).

Если же рассматривать структурный уровень описания системы S, то можно легко увидеть, что в систему S входит двухразрядный сумматор и двухразрядный умножитель. Двухразрядный сумматор - это устройство для сложения двухразрядных чисел, двухразрядный умножитель - устройство для перемножения двух чисел, каждое из которых имеет только два разряда. В систему S должно входить также простейшее устройство управления и схема дизъюнктивного объединения выходных сигналов. Устройство управления является весьма простым и функционирует следующим образом: если х=0, то (a2,al)=(f4,f3), (b2,b1)=(f6,f5) (f2,fl)=(0,0), т.е. числа а, Ь подаются на вход сумматора adder_2. Если же х=1, то (f4,f3)=(0,0), (f6,f5)=(0,0), (a2,al)=(f2,fl), т.е. числа a, b подаются на вход умножителя mult_2. Итак, VHDL-код для структурного описания системы S выглядит следующим образом: entity vlsi_l is port (a2, al, b2, bl, x: in BIT; d4, d3, d2, dl: out BIT); end vlsi_l; architecture structure ofvlsi_l is component -- декларация компонента adder_2 port (al, bl, a2, b2: in BIT; c2, s2, sl: out BIT); end component; component mult_2 port (sl, s0,rl, r0: in BIT; t3, t2, tl, t0: out BIT);

component dd port (xl, x2, x3, x4, x5, x6: in BIT; yl, y2, y3: out BIT); end component; component yy port( a2, al, b2, bl, x: in ВIT; f6, f5, f4, f3, f2, fl: out bit); end component; signal rl, f2, f3, f4, r5, f6, t4, t3, t2, tl, c2, s2, sl: BIT; — декларация внутренних сигналов begin circl: yy port map (a2, al, b2, bl, x, f6, f5, f4, f3, f2, fl); circ2: mult_2 port map (f2, fl, b2, bl, d4, t3, t2, tl); circ3: adder_2 port map (f4, f3, f6, f5, c2, s2, sl); circ4: dd port map (sl, tl, s2, t2, c2, t3, dl, d2, d3); end structure;

Функциональное же описание может быть более компактным, но недостатком является действие уже над десятичными числами, на практике внутренним форматом цифровых устройств является битовое представление. entity vlsi„l is port (a, b: in integer range 0 to 3; x: in ВIT. D: out integer range 0 to 15); end vlsi_l;

architecture functional ofvlsi_l is signal e: integer range 0 to 15; Begin p0: process (a, b, x) Begin if (x=’0’) then e<=a+b; elseif (x=’1’) then e<=a*b; end if; end process; D <= e; end functional;

Один из вариантов описания системы S в целом

Library IEEE; library synopsys; use IEEE.std_logic_1164.all; use synopsys.attributes.all;

entity vlsi_1 is port (a, b: in integer range 0 to 3; x: in BIT; D: out integer range 0 to 15); end vlsi_1;

architecture functional of vlsi_1 is signal e: integer range 0 to 15;

begin

p0:process (a,b,x) begin if (x='0') then e<=a+b; else if (x='1') then e<=a*b; end if; end if; end process; D <= e; end functional;

Вариант 4. 8-разрядный сдвиговый регистр

С состав 8-разрядного сдвигового регистра входит восемь подсхем - D-триггеров (элементов памяти). D-триггер имеет имя DFF. Library IEEE; library synopsys; use IEEE.std_logic_1164.all; use synopsys.attributes.all;

entity DFF is -- D - trigger port( RSTn, CLK, D: in bit; Q: out bit); end DFF;

architecture RTL of DFF is -- Functional D-trigger begin process (RSTn, CLK) begin if (RSTn = '0') then Q <= '0'; elsif (CLK'event and CLK = '1') then Q <= D; end if; end process; end RTL;

entity SHIFT is -- SHIFT 8-bit trigger port( RSTn, CLK, SI: in bit; SO: out bit); end SHIFT;

architecture RTL1 of SHIFT is

component DFF port(RSTn, CLK, D: in bit; Q: out bit); end component; signal T: bit_vector(6 downto 0); begin bit7: DFF port map (RSTn =>RSTn, CLK =>CLK, D =>SI, Q =>T(6)); bit6: DFF port map (RSTn, CLK, T(6), T(5)); bit5: DFF port map (RSTn, CLK, T(5), T(4)); bit4: DFF port map (CLK=>CLK, RSTn=>RSTn, D=>T(4), Q=>T(3)); bit3: DFF port map (RSTn, CLK, T(3), T(2)); bit2:DFF port map (RSTn, CLK, T(2), T(1)); bit1: DFF port map (RSTn, CLK, T(1), T(0)); bit0: DFF port map (RSTn, CLK, T(0), SO); end RTL1;

Схема SHIFT задает сдвиговый регистр - каскадное соединение D-триггеров (элементов памяти). Компонент DFF конкретизирован (упомянут) восемь раз, чтобы получить сдвиговый регистр. Каждый оператор создания экземпляра компонента должен иметь метку. Метки играют роль имен элементов схемы. Карта портов дается в скобках после ключевых слов port map.

Для выходных неиспользуемых портов компонентов нужно употребить ключевое слово open. Следующий фрагмент VHDL-кода показывает, что при создании экземпляра компонента addl на вход b1 можно подать константу 0 и выход с1 не использовать. P1: addl port map (bl => '0', b2 => x, sl => sl, с1 => open);

Вариант 5. 7-разрядный сумматор

7-разрядный сумматор: 1 - в виде каскадного соединения одноразрядного полусумматора addl и одноразрядных сумматоров add2; 2 - в виде каскадного соединения одноразрядного полусумматора addl и двухразрядных сумматоров adder_2p 7-разрядный сумматор является каскадным соединением одного полусумматора addl и шести одноразрядных сумматоров add2. Library IEEE; library synopsys; use IEEE.std_logic_1164.all; use synopsys.attributes.all;

entity add1 is port (b1,b2: in BIT; cl,sl: out BIT); end add1;

architecture struct_1 of add1 is begin sl <= ((b1 and (not b2)) or ((not b1) and b2)); cl<=b1 and b2; end struct_1;

entity add2 is port (c1,a1, a2: in BIT; c2,s2: out BIT); end add2;

architecture struct_1 of add2 is begin s2 <=((not a1) and (not a2) and c1) or ((not a1) and a2 and (not c1)) or (a1 and (not a2) and (not c1)) or (a1 and a2 and c1); c2 <=((not a1) and a2 and (not c1)) or (a1 and (not a2) and c1) or (a1 and a2 and (not c1)) or (a1 and a2 and c1); end struct_1;

entity adder_N_comp is port (a, b: in bit_vector (0 to 6); s: out bit_vector (0 to 6); с: out bit); end adder_N_comp;

architecture structural of adder_N_comp is

component addl port (b1, b2: in BIT; cl, sl: out BIT); end component;

component add2 port (c1, a1, a2: in BIT; c2, s2: out BIT); end component;

signal c_in: bit_vector (0 to 6);

begin p0: addl port map (b1 => a(0), b2 => b(0), cl => c_in(0), sl => s(0)); pi: add2 port map (c1 => c_in(0), a1 => a(1), a2 => b(1), c2 =>c_in(1), s2=> s(1)); p2: add2 port map (c1 => c_in(1), a1 => a(2), a2 => b(2), c2 => c_in(2), s2=>s(2)); p3: add2 port map (c1 => c_in(2), a1 => a(3), a2 => b(3), c2=> c_in(3), s2=>s(3)); p4: add2 port map (c1 => c_in(3), a1 => a(4), a2 => b(4), c2 => c_in(4), s2=>s(4)); p5: add2 port map (c1 => c_in(4), a1 => a(5), a2 => b(5), c2 => c_in(5), s2=>s(5)); p6: add2 port map (c1 => c_in(5), a1 =>a(6), a2=> b(6), c2=>c_in(6), s2 => s(6)); end structural;

Вариант 6. N-разрядный сумматор

N-разрядный сумматор adder_N может быть реализован при помощи оператора generate. Library IEEE; library synopsys; use IEEE.std_logic_1164.all; use synopsys.attributes.all;

entity add1 is port (b1,b2: in BIT; cl,sl: out BIT); end add1;

architecture struct_1 of add1 is begin sl <= ((b1 and (not b2)) or ((not b1) and b2)); cl<=b1 and b2; end struct_1;

entity add2 is port (c1,a1, a2: in BIT; c2,s2: out BIT); end add2;

architecture struct_1 of add2 is begin

c2 <=((not a1) and a2 and (not c1)) or (a1 and (not a2) and c1) or (a1 and a2 and (not c1)) or (a1 and a2 and c1); end struct_1;

entity adder_N is generic (N: natural:= 4); port (a, b: in bit_vector (0 to N-1); s: out bit_vector (0 to N-1); c: out bit); end adder_N;

architecture functional of adder_N is component add1 port (b1, b2: in BIT; cl, sl: out BIT); end component;

component add2 port (c1, a1, a2: in BIT; c2, s2: out BIT); end component;

signal c_in: bit_vector (0 to N-1);

begin

adder: for i in 0 to N-1 generate first_bit: if(i=0) generate first_cell: add1 port map (b1 => a(0), b2 => b(0), cl => c_in(0), sl => s(0)); end generate first_bit;

middle_bit: if (i>0) and (i <N-1) generate middle_cell: add2 port map (c1 => c_in(i-1), a1 => a(i), a2 => b(i), c2 => c_in(i), s2 => s(i)); end generate middle_bit; end_bit: if (i = N-1) generate end_cell: add2 port map (c1 => c_in(i-1), a1 => a(i), a2 => b(i), c2 => c, s2 => s(i)); end generate end_bit; end generate adder;

end functional;

Вариант 7. 3-х битовый счетчик

Library IEEE; library synopsys; use IEEE.std_logic_1164.all; use synopsys.attributes.all;

entity COUNTER3 is port (CLK: in bit; RESET: in bit; COUNT: out integer range 0 to 7); end COUNTER3;

signal COUNT_tmp: integer range 0 to 7; begin p0: process begin wait until (CLK'event and CLK = '1'); if RESET = '1' or COUNT_tmp = 7 then COUNT_tmp <= 0; else COUNT_tmp <= COUNT_tmp + 1; end if; end process; COUNT <= COUNT_tmp; end MY_ARCH;

Вариант 8. Синхронный конечный автомат с асинхронным сбросом

Library IEEE; library synopsys; use IEEE.std_logic_1164.all; use synopsys.attributes.all;

package MY_TYPES is type STATE_TYPE is (S0, S1, S2, S3); end MY_TYPES;

use WORK.MY_TYPES.ALL;

entity STATE_MACHINE is port(CLK, INC, A, B: in BIT; RESET: in Boolean; t: out BIT); end STATE_MACHINE;

architecture EXAMPLE of STATE_MACHINE is signal CURRENT_STATE, NEXT_STATE: STATE_TYPE; begin SYNC: process(CLK, RESET) begin if (RESET) then CURRENT_STATE <= S0; elsif (CLK'event and CLK = '1') then CURRENT_STATE <= NEXT_STATE; end if; end process SYNC;

FSM: process(CURRENT_STATE, A, B) begin t <= A; NEXT_STATE <= S0; if (INC = '1') then case CURRENT_STATE is when S0 => NEXT_STATE <= S1; when S1 => NEXT_STATE <= S2; t <= B; when S2 => NEXT_STATE <= S3; when S3 => null; end case; end if; end process FSM;

ПРИЛОЖЕНИЕ 2

Варианты заданий на лабораторные работы № 5-8

ОГЛАВЛЕНИЕ

Учебное издание

Воробьёв Эдуард Игоревич Кострова Вера Николаевна Яковлев Николай Викторович Яцура Евгений Николаевич

ЯЗЫК VHDL И СОПРОВОЖДАЮЩИЕ ЕГО ПАКЕТЫ

Редактор Е.П. Колтакова

Компьютерный набор Н.В. Яковлева, Е.Н. Яцуры ЛР № 066815 от 25.08.99 Подписано в печать 31,01,2001 Формат 60х84/16. Бумага для множительных аппаратов. Усл. печ. л. 6,5, Уч-изд. л.6,1. Тираж 120 экз. «С» Зак. №_____

Издательство Воронежского государственного технического университета 394026 Воронеж, Московский просп., 14

Э.И. Воробьёв, В.Н. Кострова

ЯЗЫК VHDL И СОПРОВОЖДАЮЩИЕ ЕГО ПАКЕТЫ Учебное пособие

Воронеж 2001

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-26; просмотров: 503; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 13.58.77.244 (0.011 с.) |

,

,