Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Процедура проектирования FPGA ExpressСодержание книги Поиск на нашем сайте Введение ЯзыкVHDL является фактически международным стандартом в области автоматизации проектирования цифровых систем, это входной язык многих современных систем автоматизированного проектирования (САПР) как заказных, так и программируемых логических интегральных схем (ПЛИС) и программируемых пользователями вентильных матриц. VHDL предназначен, в первую очередь, для спецификации - точного описания проектируемых систем и их моделирования на начальных этапах проектирования - алгоритмическом и логическом. С помощью VHDL можно моделировать электронные схемы с учетом реальных временных задержек. В последнее время весьма успешно разрабатываются и системы синтеза схем по спецификациям на этом языке. Например, используя САПР Xilinx Foundation Series 2.1i, можно провести моделирование исходного описания схемы на языке VHDL, а затем синтезировать схему и получить файл настройки (конфигурации) микросхемы типа FPGA фирмы Xilinx. Использование САПР MAX+PLUSII позволяет решать аналогичные задачи для программируемых микросхем, выпускаемых фирмой Altera. VHDL - это мощный язык, он позволяет описывать поведение, т.е. алгоритмы функционирования цифровых систем, а также проводить иерархическое функционально-структурное описание систем, имеет средства для описания параллельных асинхронных процессов, регулярных (систолических) структур и в то же время имеет все признаки языка программирования высокого уровня - позволяет создавать свои типы данных, имеет широкий набор арифметических и логических операций и т.д.

Лабораторная работа № 1

ОТЛАДЧИК FPGA EXPRESS

1. Общее описание работы

1.1. Цель работы – получение навыков для работы с отладчиком FPGA EXPRESS.

1.2. Содержание работы

Лабораторная работа состоит из домашнего и лабораторного заданий. Домашнее задание заключается в самостоятельном освоении наиболее простых возможностей отладчика и ознакомлении с его назначением. Лабораторное задание включает ввод вашего варианта примера программы, написанной на VHDL, и освоение на ее примере принципов работы с отладчиком FPGA EXPRESS.

1.3. Используемое оборудование

Для выполнения лабораторной работы используется ПЭВМ типа IBM PC, цветной монитор с графическим адаптером VGA и выше, принтер.

2. Домашнее задание и методические указания по его выполнению

По методическому руководству ознакомиться с назначением и возможностями отладчика моделей цифровых устройств на языке VHDL.

3. Теоретическая часть

FPGA Express транслирует и оптимизирует описания VHDL во внутренний формат, эквивалентный уровню примитивных логических элементов. Этот формат затем компилируется в технологию FPGA. Для работы с VHDL необходимо ознакомиться со следующими понятиями: Языки аппаратного описания. VHDL. FPGA Express. Использование FPGA Express. Модель процесса проектирования. Министерство обороны США в 1982 году разработало VHSIC HDL (VHDL) как часть программы развития сверхвысокоскоростных ИС (VHSIC). VHDL описывает поведение, функции, входы и выходы цифровой схемы. VHDL по стилю и синтаксису аналогичен современным языкам программирования, однако, он включает много специфических аппаратных конструкций. FPGA Express читает и анализирует поддерживаемый синтаксис VHDL..

Языки аппаратного описания Языки аппаратного описания (HDL) используются для описания архитектуры и поведения дискретных электронных систем. Эти языки разработаны для построения сложных проектов. Часто проводят историческую аналогию на предмет того, как могут называться программные языки описания, от машинных кодов (транзисторы и пайка) к ассемблерным языкам (списки цепей) и далее к языкам высокого уровня (HDL). HDL-ориентированные системы полезны при разработке больших проектов, когда несколько разработчиков или даже несколько команд работают совместно. HDL обеспечивают структурное программирование. После того, как приняты основные архитектурные решения, а основные компоненты и связи между ними идентифицированы, работа над подпроектами может происходить совершенно независимо. Типичные применения HDL

Преимущества HDL Методология проекта, использующего HDL, имеет несколько фундаментальных преимуществ перед традиционной компонентно-уровневой методологией проектирования. Среди этих преимуществ необходимо отметить следующие: Вы можете очень рано проверить функциональные возможности проекта и немедленно промоделировать его. Моделирование проекта на таком высшем уровне до трансляции в элементарное исполнение позволяет протестировать многие архитектурные и проектные решения. FPGA Express обеспечивает логический синтез и оптимизацию, так что возможно автоматически преобразовать описание VHDL в исполнение элементарного уровня для выбранной технологии. Такая методология устраняет узкие места компонентного уровня и уменьшает время проектирования, а также количество ошибок, вносимых при ручной трансляции программы VHDL в конкретные элементы. С помощью логической оптимизации FPGA Express возможно автоматически преобразовать синтезированный проект в наименьшую и наискорейшую схему. Кроме того, допускается назначить информацию, полученную при синтезе и оптимизации схем, вновь к существующему описанию VHDL, что приводит к более точной подстройке архитектурных решений. Описания HDL обеспечивают технологически независимую документацию проекта и его функциональных возможностей. Эти программы читаются и понимаются гораздо легче, чем списки цепей или схемы. Вследствие того, что начальное HDL описание проекта является технологически независимым, допускается использовать его для генерации проектов с различной технологией, не затрагивая при этом оригинальную. VHDL, как и большинство языков высокого уровня, производит жесткую проверку типов. Компоненты, тип которых объявлен четырехбитовым сигналом, не могут соединяться с трех- или пятибитовым сигналом; такое несогласование приведет к ошибке при компиляции. Если диапазон переменных определен от 1 до 15, то ошибка возникнет при назначении им значения 0. Некорректное использование типов является основным источником ошибок при составлении описаний. Проверка типов обнаруживает такие ошибки даже перед генерацией проекта. Отладка в FPGA Express Для отладки необходимо осуществить следующие действия:

2. Подключить созданный файл к проекту в FPGA Express. Для подключения файла к проекту необходимо создать сам проект: Выбрать меню File / New. Ввести название проекта. При запросе файлов проекта необходимо найти файл(ы), созданный в 1 пункте с уже готовым описанием устройства (компонента). При корректном подключении файла(ов) проекта появляется окно, разделенное на две части: Design Sources и Chips (рис. 1). Где Design Sources - окно для работы с файлами проекта, Chips - окно для работы с синтезированными устройствами.

Рис.1. Окно проекта

Для удобства работы с файлом(ами) проекта в окне Design Sources выводятся название(ия), расположение(ия) файла(ов), а также наличие синтаксических и лексических ошибок или неточностей. При наведении курсор и одновременном нажатии правой кнопки мыши на любое из названий в данном окне появляется следующее контекстное меню (рис. 2): Update Project - анализ проекта на наличие неточностей или ошибок. Force Update Project - полный анализ всех фалов проекта на наличие ошибок или неточностей. Create Implementation - создание модели устройства. Edit File - редактирование файла. Identify Sources - подключение файла к проекту. New library - подключение собственной библиотеки к проекту. Project Report - отчет проекта (краткое описание в виде внешнего текстового файла). Remove - удаление файла или библиотеки из проекта.

Рис.2. Контекстное меню

Данное контекстное меню является универсальным и единственным, для окна Design Sources. Другими словами, в зависимости от того, применимо или нет данное действие из меню к элементу проекта (исходный файл, библиотека, синтезированная модель), пункты меню будут соответственно активными или нет. Например, пункт меню Edit File применим только к исходным файлам, следовательно, при активизации меню он будет активен в отличие от пункта Create Implementation, который работает только при выборе синтезированной модели устройства.

Как и во всех приложениях с дружественным интерфейсом, каждый пункт контекстного меню дублируется простым меню и кнопками на панели.

Рис.3. Часть файла с ошибкой

Редактирование файла происходит аналогично текстовым редакторам, а единственным отличием является то, что удаление символов или строк можно производить только с помощью клавиши Back Space. После исправления для поиска других существующих ошибок в данном окне необходимо нажать правую клавишу мыши и в активном контекстном меню выбрать пункт Analyze File (поиск неточностей или ошибок). Далее после успешного редактирования желательным является сохранение текущих изменений. Если ошибки отсутствуют, то соответствующий файл будет иметь свой синтезированный вариант (т.е. модель устройства, описанную во внутреннем формате FPGA Express, как показано на рис. 4).

Рис.4. Знак синтезированного варианта устройства CODER

Синтезированный вариант является промежуточным звеном для успешного создания модели цифрового устройства.

4. Ход работы

4.1 С помощью любого текстового редактора набрать описание цифрового устройства в соответствии с вашим вариантом. Для предупреждения ошибок необходимо, чтобы файл имел расширение *.vhd. 4.2 Создать проект в отладчике FPGA Express и подключить к нему набранный файл. 4.3 После корректного подключения файла описания, создать с помощью FPGA Express отчет по вашему проекту.

5. Указания по оформлению отчета и Контрольные вопросы

5.1. Отчет по лабораторной работе должен содержать: - наименование; - цель работы; - используемое оборудование; - теоретическую часть; - описание последовательности действий при отладке вашего варианта; - распечатку отчета по проекту; - распечатку вашего исходного файла; - выводы по проделанной работе.

5.2. Контрольные вопросы к лабораторной работе. 1. Что собой представляет приложение FPGA Express и каковы его основные функции? 2. Каковы на ваш взгляд достоинства и недостатки языка HDL как языка аппаратного описания? 3. Какова последовательность действий при отладке VHDL описания вашего устройства?

Лабораторная работа № 2

ОСНОВНЫЕ ВОЗМОЖНОСТИ ОТЛАДЧИКА FPGA EXPRESS

1. Общее описание работы

1.1. Цель работы – изучение возможностей синтеза и оптимизации отладчика FPGA EXPRESS.

1.2. Содержание работы

Лабораторная работа состоит из домашнего и лабораторного заданий. Домашнее задание заключается в повторении принципов отладки VHDL описаний. Лабораторное задание включает ввод вашего варианта примера программы, написанной на VHDL, и изучение принципов синтеза и оптимизации проектируемого устройства с помощью отладчика FPGA EXPRESS.

1.3. Используемое оборудование

Для выполнения лабораторной работы используется ПЭВМ типа IBM PC, цветной монитор с графическим адаптером VGA и выше, принтер.

2. Домашнее задание и методические указания по его выполнению

По методическому руководству ознакомиться и повторить назначения и возможности отладчика моделей цифровых устройств на языке VHDL.

3. Теоретическая часть Методология проектирования На рис. 5 приведена типичная процедура проектирования, которая использует FPGA Express и симулятор VHDL. Каждый шаг такой модели проектирования описан подробно.

Рис. 5. Структурная -схема этапов проектирования

2. Обеспечение языковых тестовых драйверов VHDL для симулятора. Драйвера обеспечивают тестовые вектора для моделирования и собирают выходные данные. 3. Моделирование проекта с помощью симулятора VHDL. Проверка правильности описания проекта. 4. Использование FPGA Express для синтеза и оптимизации описания проекта VHDL в элементарный список цепей. FPGA Express генерирует оптимизированные списки цепей, удовлетворяющие временным ограничениям выбранной архитектуры FPGA. 5. Использование системы проектирования FPGA (Design Manager) для связи определенной технологической версии FPGA с симулятором VHDL. Система проектирования включает в себя модели симуляции и интерфейсы, необходимые для сквозного проектирования. 6. Моделирование определенной технологической версии проекта с помощью симулятора VHDL. Допускается использовать оригинальные драйверы моделирования VHDL из пункта 2, поскольку определения модулей и портов сохраняются в процессе трансляции и оптимизации. 7. Сравнение выхода моделирования на элементном уровне (п. 6) с выходом моделирования оригинального описания VHDL (п. 3) для проверки того, что исполнение является корректным.

Иерархия проекта FPGA Express поддерживает иерархические границы, определяемые при использовании структурных конструкций VHDL. Эти границы приводят к двум основным результатам: 1. Каждый проектный объект, определяемый в описании VHDL, синтезируется отдельно и поддерживается в виде независимого проекта. При этом учитываются проектные ограничения, и каждый объект может быть оптимизирован отдельно в FPGA Express. 2. Компонентные реализации внутри описаний VHDL поддерживаются в течение ввода. Имя реализации, которое присваивается каждому пользовательскому объекту, сохраняется вплоть до выполнения на элементном уровне. Примечание. FPGA Express не поддерживает и не создает автоматически иерархию других неструктурных конструкций VHDL, таких, как блоки, процессы, циклы, функции и процедуры. Эти элементы описания VHDL транслируются в контексте своих проектов. После чтения проекта VHDL вы можете сгруппировать вместе логику процесса, функции или процедуры внутри окна выполнения FPGA Express (Implementation Window). Выбор иерархических границ оказывает значительное воздействие на качество синтезируемого проекта. С помощью FPGA Express вы можете оптимизировать проект, сохраняя его иерархические границы. FPGA Express только частично оптимизирует логику поперек иерархических модулей. Полная оптимизация возможна в тех частях иерархии проекта, которые сжаты в FPGA Express. Пример иерархической структуры сложного устройства показан на рис. 6

Рис. 6. Иерархическая структура

Типы данных В VHDL необходимо назначать тип всем портам, сигналам и переменным. Тип данных объекта определяется операцией, которая может быть ему назначена. Например, оператор AND определяется для объектов типа BIT, но не для объектов типа INTEGER. Типы данных важны и при синтезе проекта. Тип данных объекта определяет его размер (ширину в битах) и битовую организацию. Правильный выбор типов данных значительно улучшает качество проекта и помогает минимизировать количество ошибок.

Проектные ограничения Необходимо описать качественные ограничения модуля проекта внутри FPGA Express Implementation Window. Выбор регистра Размещение регистров и тактирующих схем является очень важным архитектурным решение. Существует два способа определения регистров в вашем описании VHDL. У каждого из этих методов существуют определенные преимущества: 1. Реализовать регистры непосредственно в описании VHDL, выбрав любой нужный элемент из библиотеки FPGA. Тактирующие схемы могут быть произвольной сложности. Выбирается архитектура, базирующаяся на триггерах или защелках. Основными недостатками такого подхода являются: Описание VHDL теперь привязано к определенной технологии, поскольку вы выбрали структурные элементы из технологической библиотеки. Однако возможно изолировать этот раздел проекта в виде отдельного объекта, который затем будет связан с остальной частью проекта. Программа пишется более сложно.

Асинхронные проекты Возможно использовать FPGA Express для конструирования асинхронных проектов с кратными и управляемыми синхроимпульсами. Однако, хотя эти проекты являются логически (статистически) корректными, они могут неправильно моделироваться или работать в связи с условиями состязания.

Языковые конструкции Другим компонентом политики синтеза VHDL является набор конструкций, которые описывают проект, они определяют его архитектуру и дают последовательно хорошие результаты. Регистры реализуются с помощью компонентных конструкций.

Лабораторная работа № 3

СИМУЛЯТОР VHDL МОДЕЛЕЙ MODELSIM

1. Общее описание работы

1.1. Цель работы – знакомство с симулятором VHDL моделей ModelSim.

1.2. Содержание работы

Лабораторная работа состоит из домашнего и лабораторного заданий. Домашнее задание заключается в повторении принципов отладки, синтеза и оптимизации VHDL описаний с помощью отладчика FPGA Express. Лабораторное задание включает ввод варианта примера программы написанной на VHDL и осуществить моделирование и анализ вашего устройства с помощью симулятора ModelSim.

1.3. Используемое оборудование

Для выполнения лабораторной работы используется ПЭВМ типа IBM PC, цветной монитор с графическим адаптером VGA и выше, принтер.

2. Домашнее задание и методические указания по его выполнению

По методическому руководству ознакомиться и повторить назначения и все основные возможности отладчика моделей цифровых устройств на языке VHDL.

3. Теоретическая часть

Рис. 10. Схема активного цифрового устройства

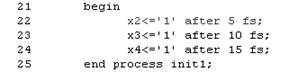

То здесь кроме описания структуры и функции самого элемента необходимо создать дополнительно устройство, генерирующее определенную последовательность логических состояний входов (возможно входную часть таблицы истинности) элемента Шеффера.

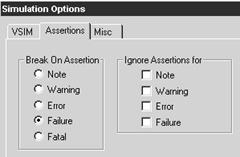

Моделирования в ModelSim При отсутствии ошибок на этапах подключения файла с исходным активным устройством для моделирования можно начать сам процесс моделирования. В зависимости от целей моделирования в системе ModelSim предусмотрены: коноль за временной дискретизацией моделирования, а также возможность непосредственного наблюдения практически за всеми ключевыми процессами, происходящими устройстве (последнее будет рассмотрено в следующей лабораторной работе). Рассмотрим средства контроля за моделированием. В этом смысле для полноценного контроля за процессом моделирования необходимы: главное меню Run и Options. В меню Run для контроля предназначены все пункты, а в меню Options - пункт Simulate Options (установка частных параметров моделирования). При активизации пункта Simulate Options появляется панель ввода параметров моделирования(рисунок 14). В данной панели содержится три вкладки: VSIM - непосредственно параметры моделирования. Здесь устанавливаются следующие параметры: Default Run length - установка минимальной временной дискретизации процесса моделирования.

Suppress Warnings - отключение/включение реакции системы на предупреждения, связанные с различного рода неточностями. Default Force Kind - установка возможности управления процесса моделирования (Freeze (отсутствие контроля)/ Drive (управление)/ Deposit (полностью под контролем)). Default Radix - вид сигнала по умолчанию (Symbolic (символьный) /binary (двоичный) / octal (восьмеричный) /decimal(десятичный)/hex(шестнадцатеричный)).

Рисунок 14 - панель Simulate Options

Ase ащитный действия системы на различного рода ошибки (рис. 15): rtion - Break On моделирования. (Note (комментарий) /warning (ошибка)). Ignore Assertions for - установка границ пренебрежения системой защиты. (Note (комментарий)/ warning (неточность)/ error(- установки параметров вывода исходного файла в окне Source ошибка)/ failure ("провал")). действий системы Misс.

4. Ход работы

4.1. С помощью любого текстового редактора набрать описание цифрового устройства в соответствии с вашим вариантом. Для предупреждения ошибок необходимо, чтобы файл имел расширение *.vhd. 4.2. Создать проект в системе моделирования ModelSim и подключить к нему набранный и отлаженный в FPGA Express файл. 4.3. После корректного подключения файла описания осуществить установку системы для тестирования вашего устройства.

- 5. Указания - теоретическую часть; - описание последовательности действий при установкие описания устройства для моделирования; - выводы по проделанной работе.

5.2. Контрольные вопросы к лабораторной работе

1. В чём заключается необходимость использования систем моделирования подобных ModelSim. 2. Каковы недостатки системы, если таковые присутствуют? 3. Какова на ваш взгляд область применения системы ModelSim?

Лабораторная работа № 4

СИМУЛЯТОР MODELSIM

1. Общее описание работы

1.1. Цель работы – получение навыков для моделирования проектируемых устройств в системе ModelSim.

1.2. Содержание работы

Лабораторная работа состоит из домашнего и лабораторного заданий. Домашнее задание заключается в повторении принципов работы с симулятором ModelSim, освоенных в предыдущей лабораторной работе. Лабораторное задание состоит в подключении вашего варианта примера программы, написанной на VHDL, и в проведении полноценного моделирования и анализа проектируемого устройства с помощью ModelSim.

1.3. Используемое оборудование

Для выполнения лабораторной работы используется ПЭВМ типа IBM PC, цветной монитор с графическим адаптером VGA и выше, принтер.

2. Домашнее задание и методические указания по его выполнению

Повторить материал, освоенный на предыдущих занятиях.

3. Теоретическая часть

и вывода) / Internal Signals (внутренние сигналы)). Для этого в ModelSim была создана система информационных и функционально-информационных окон (главное меню View). Главным условием работы всех окон является корректно подключенный исходный файл с VHDL описанием моделируемого устройства. Рассмотрим принципы работы с ним: 1. Source - окно с содержанием исходного VHDL - файла (рис. 16). Позволяет устанавливать точки останова (для этого необходимо двойное нажатие левой кнопкой мыши на номере строки). Для изменения содержимого окна нужно активизировать пункт Select Source File... главного меню File (поменять исходный файл можно только на файл, подключенный к проекту), либо двойное нажатие левой кнопкой мыши в окне по оформлению отчета и Контрольные вопросы

5.1. Отчет по лабораторной работе должен содержать: - наименование; - цель работы; используемое оборудование;Structure на названии необходимого файла. Замечание: окно не позволяет редактировать исходные файлы.

Рис.16. Окно Source

2. Structure - окно содержащее структуру и подчиненность файлов проекта (рис. 17). Несет вспомогательную функцию для окна Source. Рис. 17. Окно Structure

4. Signals – окно, содержащее список и значения всех портов ввода/вывода и сигналов (рис. 19). Окно фиксирует любые изменения содержимого всех портов ввода/вывода и сигналов. Существует возможность удаления, добавления или установки ограниченного числа сигналов или портов в данном окне в зависимости

Кроме этого важным свойством окна Signals в совокупности с пунктом Force Signal главного

Рис. 20. Окно View Signals.

К параметрам изменений относятся следующие: Signal - название сигнала (обычно указывается в виде подчиненности. Например: устройство CODER содержит порт ввода/вывода X4, тогда соответственно полное имя сигнала CODER.X4).

Рис. 21. Окно Force Signal

Delay - время задержки текущего значения сигнала (масштаб значения указывается справа от поля ввода). Second Value значение - следующего состояния данного сигнала или порта ввода/вывода. : для вводить именно тот тип задержки перед изменением текущкомендуется значения, который Примечание предупреждения ошибок, связанных с моделированием устройства, ре Delay for second Value - значение предусмотрен для проектируемого устройства. его состояния на последующее (Second Value). Примечание: значение данного поля должно быть обязательно обоех задержек сигналов.

Примечание: значение данного поля должно быть обязательно больше значения в поле Delay for second Value, поскольку начальная точка временного отсчета процесса моделирования является общей для всех задержек сигналов. Kind - установка степени автономности производимых изменений. (Freeze (система автономно управляет изменениями) / Drive (возможность управления) / Deposit (бесконтрольное управление проектировщиком)). Для подтверждения введенных параметров изменений сигнала или порта ввода/вывода следует нажать кнопку Apply. Для установки параметров изменений другого сигнала, его предварительно необходимо выбрать в окне Signals.

5. List – окно, содержащее дискретный по времени список сигналов и их значения (своего рода таблица истинности по всем сигналам или портам ввода/вывода в Рис. 22. Окно List.

Примечание. Mинимальный шаг регистрации изменений значений сигналов устанавливается в параметрах процесса моделирования (Options.../ Simulate Options...). В окне предусмотрены различные опции связанные с фиксированием изменений сигналов и сохранения полученной таблицы в отдельном файле. 6. Process – окно, содержащее название и состояние VHDL -процессов текущего моделируемого устройства (рис. 23). Имеется возможность ограниченного вывода процессов при использовании пункта Processes в главном меню Options (возможно вывести все активные процессы (View Active Processes) или активные процессы на текущем шаге (итерации) моделирования).

Рис. 23. Окно Process

7. Wave – окно, необходимое для вывода временных диаграмм определенного набора сигналов или портов ввода/вывода (рис. 24).

Рис. 24. Окно Wave

Окно обладает всеми свойствами гибкого средства наблюдения за изменениями сигналов во временных рамках самого процесса моделирования. В совокупности с окном Signals и пунктом Add to Waveform главного меню Signals данное окно имеет возможность определения ограниченного списка сигналов подпункт Selected Signals (установка в рабочий список сигналов, выделенных в окне Signals), подпункт Signals in Region (наблюдение за активными сигналами на текущей итерации моделирования), подпункт Signals in Design (установка всех сигналов проекта), подпункт Signals from DataFlow (установка сигналов, участвующих в выбранном информационном потоке, из окна DataFlow)). Как и все функциональные окна, это окно имеет возможности для работы со списком выводимых сигналов (меню окна Cursor и Edit), позволяет управлять выводом временных диаграмм (меню окна Zoom и Options). Дополнительным вспомогательным средством является бегунок (устанавливается в любой точке на диаграмме с помощью мыши), фиксирующий время моделирования в текущем положении. Кроме этого при изменении положения бегунка, если в следующем положении меняются значения какого-либо из сигналов, соответствующие изменения регистрируются в списке изображаемых сигналов (слева от диаграмм, как это показано на рис. 24). 8. DataFlow – окно, выводящее организацию всех информационных потоков, присутствующих в моделируемом устройстве (рис. 25).

Рис. 25. Окно DataFlow

Как и большинство функциональных окон, это окно работает в совокупности с другими окнами: Signals (данное окно позволяет выбрать рассматриваемый(ые) сигнал(ы) для дальнейшей визуализации связанных с ним(ними) информационных потоков в окне DataFlow). Process (с помощью этого окна можно выбрать процесс для дальнейшей демонстрации его информационных потоков).

4. Ход работы

4.1. С помощью любого текстового редактора набрать описание цифрового устройства в соответствии с вашим вариантом. Для предупреждения ошибок необходимо, чтобы файл имел расширение *.vhd. 4.2. Создать проект в системе моделирования ModelSim и подключить к нему набранный и отлаженный в FPGA Express файл. 4.3. После корректного подключения файла описания осуществить установку системы для тестирования вашего устройства. 4.4. Провести тестирование и полный анализ вашего цифрового устройства в соответствии с вашим вариантом.

5. Указания по оформлению отчета и Контрольные вопросы

5.1. Отчет по лабораторной работе должен содержать: - наименование; - цель работы; - используемое оборудование; - теоретическую часть; - описание последовательности действий при процессе анализа и моделирования вашего варианта; - распечатку всех состояний, всех сигналов; - распечатку вашего исходного файла; - распечатку временных диаграмм и процессов; - выводы по проделанной работе.

5.2. Контрольные вопросы к лабораторной работе

1. Каковы основные функции окон Signals и Wave? 2. Насколько важна визуализация структуры информационных потоков в устройстве при проектировании?

Лабораторная работа № 5

ЗНАКОМСТВО С ЯЗЫКОМ VHDL

1. Общее описание работы

1.1. Цель работы – изучение осн

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-26; просмотров: 451; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.119 (0.011 с.) |