Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Использование FPGA Express для компиляции проекта VHDLСодержание книги

Поиск на нашем сайте

Когда проект VHDL открывается в FPGA Express, то он преобразуется во внутренний формат базы данных так, чтобы FPGA Express мог синтезировать и оптимизировать его. Когда FPGA Express оптимизирует проект, он может изменить структуру частей или всего проекта в целом. Управление идёт лишь степенью реструктуризации. Предоставляются следующие опции: Полное сохранение иерархии проекта. Перемещение целых модулей вверх или вниз по иерархии. Комбинирование определенных модулей с другими. Сжатие целого проекта в один модуль (сглаживание проекта), если это будет полезным.

Отладка в FPGA Express Для отладки необходимо осуществить следующие действия:

2. Подключить созданный файл к проекту в FPGA Express. Для подключения файла к проекту необходимо создать сам проект: Выбрать меню File / New. Ввести название проекта. При запросе файлов проекта необходимо найти файл(ы), созданный в 1 пункте с уже готовым описанием устройства (компонента). При корректном подключении файла(ов) проекта появляется окно, разделенное на две части: Design Sources и Chips (рис. 1). Где Design Sources - окно для работы с файлами проекта, Chips - окно для работы с синтезированными устройствами.

Рис.1. Окно проекта

Для удобства работы с файлом(ами) проекта в окне Design Sources выводятся название(ия), расположение(ия) файла(ов), а также наличие синтаксических и лексических ошибок или неточностей. При наведении курсор и одновременном нажатии правой кнопки мыши на любое из названий в данном окне появляется следующее контекстное меню (рис. 2): Update Project - анализ проекта на наличие неточностей или ошибок. Force Update Project - полный анализ всех фалов проекта на наличие ошибок или неточностей. Create Implementation - создание модели устройства. Edit File - редактирование файла. Identify Sources - подключение файла к проекту. New library - подключение собственной библиотеки к проекту. Project Report - отчет проекта (краткое описание в виде внешнего текстового файла).

Remove - удаление файла или библиотеки из проекта.

Рис.2. Контекстное меню

Данное контекстное меню является универсальным и единственным, для окна Design Sources. Другими словами, в зависимости от того, применимо или нет данное действие из меню к элементу проекта (исходный файл, библиотека, синтезированная модель), пункты меню будут соответственно активными или нет. Например, пункт меню Edit File применим только к исходным файлам, следовательно, при активизации меню он будет активен в отличие от пункта Create Implementation, который работает только при выборе синтезированной модели устройства.

Как и во всех приложениях с дружественным интерфейсом, каждый пункт контекстного меню дублируется простым меню и кнопками на панели.

Рис.3. Часть файла с ошибкой

Редактирование файла происходит аналогично текстовым редакторам, а единственным отличием является то, что удаление символов или строк можно производить только с помощью клавиши Back Space. После исправления для поиска других существующих ошибок в данном окне необходимо нажать правую клавишу мыши и в активном контекстном меню выбрать пункт Analyze File (поиск неточностей или ошибок). Далее после успешного редактирования желательным является сохранение текущих изменений. Если ошибки отсутствуют, то соответствующий файл будет иметь свой синтезированный вариант (т.е. модель устройства, описанную во внутреннем формате FPGA Express, как показано на рис. 4).

Рис.4. Знак синтезированного варианта устройства CODER

Синтезированный вариант является промежуточным звеном для успешного создания модели цифрового устройства.

4. Ход работы

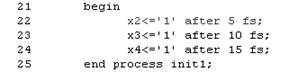

4.1 С помощью любого текстового редактора набрать описание цифрового устройства в соответствии с вашим вариантом. Для предупреждения ошибок необходимо, чтобы файл имел расширение *.vhd. 4.2 Создать проект в отладчике FPGA Express и подключить к нему набранный файл. 4.3 После корректного подключения файла описания, создать с помощью FPGA Express отчет по вашему проекту.

5. Указания по оформлению отчета и Контрольные вопросы

5.1. Отчет по лабораторной работе должен содержать: - наименование; - цель работы; - используемое оборудование; - теоретическую часть; - описание последовательности действий при отладке вашего варианта; - распечатку отчета по проекту; - распечатку вашего исходного файла; - выводы по проделанной работе.

5.2. Контрольные вопросы к лабораторной работе. 1. Что собой представляет приложение FPGA Express и каковы его основные функции? 2. Каковы на ваш взгляд достоинства и недостатки языка HDL как языка аппаратного описания? 3. Какова последовательность действий при отладке VHDL описания вашего устройства?

Лабораторная работа № 2

ОСНОВНЫЕ ВОЗМОЖНОСТИ ОТЛАДЧИКА FPGA EXPRESS

1. Общее описание работы

1.1. Цель работы – изучение возможностей синтеза и оптимизации отладчика FPGA EXPRESS.

1.2. Содержание работы

Лабораторная работа состоит из домашнего и лабораторного заданий. Домашнее задание заключается в повторении принципов отладки VHDL описаний. Лабораторное задание включает ввод вашего варианта примера программы, написанной на VHDL, и изучение принципов синтеза и оптимизации проектируемого устройства с помощью отладчика FPGA EXPRESS.

1.3. Используемое оборудование

Для выполнения лабораторной работы используется ПЭВМ типа IBM PC, цветной монитор с графическим адаптером VGA и выше, принтер.

2. Домашнее задание и методические указания по его выполнению

По методическому руководству ознакомиться и повторить назначения и возможности отладчика моделей цифровых устройств на языке VHDL.

3. Теоретическая часть

|

||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-26; просмотров: 232; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.17.77.29 (0.006 с.) |