Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Більше блоків попередньої вибірки з більш ефективною роботоюСодержание книги

Поиск на нашем сайте

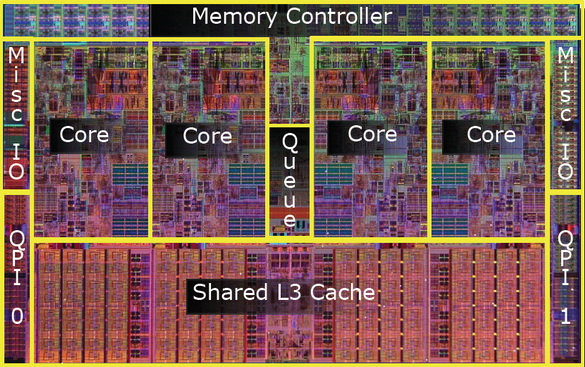

В архітектурі Conroe Intel особливо пишалася апаратними блоками передбачення. Як ви знаєте, блок пророкування - це механізм, який стежить за характером доступу до пам'яті і намагається передбачити, які дані будуть потрібні через кілька тактів. Мета полягає в тому, щоб випереджувальним чином завантажити дані в кеш, де вони будуть розташовуватися ближче до процесора, і разом з тим максимально використовувати доступну пропускну спроможність тоді, коли процесору вона не потрібна. Дана технологія дає чудові результати з більшістю настільних додатків, але в серверній середовищі вона часто приводила до втрати продуктивності. Є кілька причин подібної неефективності. По-перше, доступи до пам'яті часто складніше передбачити в серверних застосуваннях. Доступ до бази даних, наприклад, аж ніяк не лінійний - якщо в пам'яті запитується небудь елемент даних, то це не означає, що наступним буде сусідній елемент. Це обмежує ефективність блоку попередньої вибірки. Але основною проблемою була пропускна здатність пам'яті в многосокетних конфігураціях. Як ми вже говорили раніше, вона вже була "вузьким місцем" для декількох процесорів, але, крім цього, блоки попередньої вибірки приводили до додаткового навантаження на цьому рівні. Якщо мікропроцесор не виконує доступ до пам'яті, то включалися блоки попередньої вибірки, намагаючись використовувати пропускну здатність, по їх припущенню, вільну. Однак блоки не могли знати, чи потрібна ця пропускна спроможність другому процесора. Це означало, що блоки попередньої вибірки могли "відбирати" у процесора пропускну здатність, яка і так була "вузьким місцем" в таких конфігураціях. Щоб вирішити цю проблему, Intel не знайшла нічого кращого, як відключити блоки попередньої вибірки в таких ситуаціях - навряд чи найоптимальніше рішення. Як стверджує Intel, ця проблема вже вирішена, проте компанія не дає ніяких деталей з приводу роботи нових механізмів попередньої вибірки. Все, що компанія говорить: тепер не потрібно відключати блоки для серверних конфігурацій. Втім, навіть Intel нічого не змінила, переваги від нової організації пам'яті і, внаслідок цього, більша пропускна здатність повинні нівелювати негативний вплив блоків попередньої вибірки. Conroe став серйозним фундаментом для нових процесорів, і Nehalem побудований якраз на ньому. Тут використовується така ж ефективна архітектура, але тепер вона набагато більш модульна і масштабована, що повинно гарантувати успіх в різних ринкових сегментах. Ми не говоримо про те, що Nehalem революціонізував архітектуру Core, але новий процесор революціонізував платформу Intel. З усіма поліпшенням, зробленими на даному етапі (інтегрований контролер пам'яті, QPI), не дивно бачити, що зміни виконавчого ядра не такі значні. Але повернення Hyper-Threading можна вважати серйозною новиною, та й ряд невеликих оптимізацій теж повинні забезпечити помітний приріст продуктивності.

Технічні характеристики процесорів Intel (Nehalem) Core i3 Core i3 (Clarkdale) - двоядерний процесор останнього покоління, призначений для настільних комп'ютерів початкового рівня. Вперше представлений 7 січня 2010 року. Встановлюється в роз'єм LGA1156. Виробляється за 32-нм технології. Оснащений вбудованим двоканальним контролером оперативної пам'яті DDR3-1066/1333 з напругою до 1,6 В. Модулі, розраховані на більш високу напругу, не будуть працювати з цим чіпом і навіть можуть його пошкодити. Забезпечений вбудованим контроллером PCI Express 2.0 x16, завдяки якому графічний прискорювач може підключатися безпосередньо до процесора. Для з'єднання з набором системної логіки застосовується шина DMI (Digital Media Interface) c пропускною спроможністю 2 Гбайт / с. В процесори Core i3 вбудовано графічне ядро GMA HD з дванадцятьма конвеєрами і тактовою частотою 733 Мгц. Базова тактова частота для всіх моделей Core i3 - 133 МГц, номінальні частоти досягаються застосуванням множників. Сумісні набори системної логіки: Intel H55 Express, H57 Express, P55 Express, Q57 Express ОСНОВНІ ТЕХНІЧНІ характеристики CORE I3 - Мікроархітектура Nehalem - Два ядра - Кеш-пам'ять L1 - 64 Кбайт (32 Кбайт для даних і 32 Кбайт для інструкцій) для кожного ядра - Кеш-пам'ять L2 - 256 Кбайт для кожного ядра - Кеш-пам'ять L3 - 4 Мбайт, спільна для всіх ядер - Вбудований двоканальний контролер оперативної пам'яті DDR3-1066/1333 МГц - Вбудований контролер PCI Express 2.0 x16 - Вбудований графічний адаптер з тактовою частотою 733 МГц - Підтримка технології віртуалізації VT - Підтримка 64-бітних інструкцій Intel EM64T - Підтримка технології Hyper-Threading - Набір інструкцій SSE 4.2 - Набір інструкцій AES-NIS - Антивірусна технологія Execute Disable Bit - Технологія динамічної зміни частоти Enhanced SpeedStep Таблиця 2.1.2 МОДЕЛЬНИЙ РЯД

Core i5 Core i5 (Clarkdale або Lynnfield) - двох або чотирьохядерний процесор останнього покоління, призначений для настільних комп'ютерів середнього рівня. Вперше представлений 8 вересня 2009 року. Встановлюється в роз'єм LGA1156. Двоядерні Clarkdale проводиться по 32-нм технології, чотирьохядерні Lynnfield - по 45-нм технології. Оснащений вбудованим двоканальним контролером оперативної пам'яті DDR3-1066/1333 з напругою до 1,6 В. Модулі, розраховані на більш високу напругу, не будуть працювати з цим чіпом і навіть можуть його пошкодити. Забезпечений вбудованим контроллером PCI Express 2.0 x16, завдяки якому графічний прискорювач може підключатися безпосередньо до процесора. У моделях з вбудованим графічним ядром GMA HD до чіпу може підключатися одна відеокарта в режимі x16, в моделях без вбудованої графіки - дві відеокарти в режимі x8 кожна. Для з'єднання з набором системної логіки застосовується шина DMI (Digital Media Interface) c пропускною спроможністю 2 Гбайт / с. У двоядерних моделях (серія 6хх) вбудований графічний адаптер GMA HD і реалізована технологія Hyper-Threading, в чотирьохядерних (серія 7xx) графіки і Hyper-Threading немає. У моделях, номер яких закінчується на 1, тактова частота графіки становить 900 МГц, в моделях, номер яких закінчується на 0, графічне ядро працює на частоті 733 МГц. У всіх Core i5 реалізована технологія автоматичного підвищення тактової частоти Turbo Boost в ресурсномістких завданнях. Базова тактова частота для всіх моделей Core i5 - 133 МГц, номінальні частоти досягаються застосуванням множників. Сумісні набори системної логіки: Intel H55 Express, H57 Express, P55 Express, Q57 Express.

|

||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-08; просмотров: 260; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.2 (0.007 с.) |