Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Внутренняя шина и регистры процессораСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Термины- характеристики современных процессоров

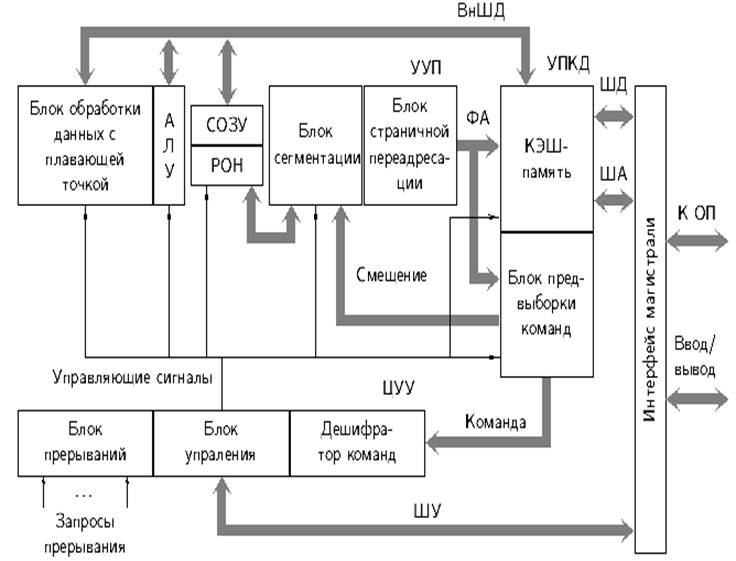

Ядро Внутренняя шина и регистры процессора Хоть процессор и получает данные из оперативной памяти с помощью некоторой ширины, это не значит, что внутри он может обрабатывать данные такой же разрядности. Количество битов данных, которые может обработать процессор за один прием, характеризуется разрядностью внутренних регистров. Регистр - это по существу ячейка памяти внутри процессора. Разрядность регистров определяет характеристики программного обеспечения и команд, выполняемых процессором. Например, процессоры с 32-разрядными внутренними регистрами могут выполнять 32-разрядные команды, которые обрабатывают данные 32-разрядными порциями, а процессоры с 16-разрядными регистрами этого делать не могут. Кроме того, в зависимости от структуры регистров различают два основных типа процессоров: RISC — Reduced (Restricted) Instruction Set Computer — процессоры (компьютеры) с сокращенной системой команд. Эти процессоры обычно имеют набор однородных регистров универсального назначения; их система команд отличается относительной простотой. В результате аппаратная реализация такой архитектуры позволяет с небольшими затратами выполнять эти инструкции за минимальное (в пределе 1) число тактов синхронизации. CISC — Complete Instruction Set Computer — процессоры с полным набором инструкций, к которым относится и семейство х86. Состав и назначение их регистров существенно неоднородны, широкий набор команд усложняет декодирование инструкций, на что расходуются аппаратные ресурсы. Возрастает число тактов, необходимое для выполнения инструкций. Практически во всех современных процессорах внутренние регистры являются 32-разрядными (исключения Itanium от Intel и Hammer от AMD).

Шина- это магистраль, связывающая некоторые компоненты компьютера между собой. Электрически шина - это провода, обеспечивающие передачу электрического сигнала. Естественно характеризовать шину скоростью, с которой по ней могут передаваться данные. Шина данных процессора Одной из самых общих характеристик процессора является разрядность его шины данных и шины адреса. Когда говорят о шине процессора, обычно имеют ввиду шину данных, которая является набором соединений, для передачи и приема данных. Чем больше сигналов одновременно поступает на шину, тем больше данных по ней передается за определенный интервал времени, и тем быстрее она работает. Разрядность шины данных подобна количеству полос автомагистрали - чем больше полос, тем больше поток машин, чем шире шина данных, тем больше данных за одинаковые промежутки времени по ней передается. В процессоре 286 для приема и передачи двоичных данных используется 16 соединений, поэтому их шина данных считается 16-разрядной. У 32-х разрядных процессоров (например, 486), таких соединений вдвое больше, поэтому за единицу времени они передают и получают вдвое больше данных, чем 16-и разрядные процессоры - разумеется, эффективность выше. Современные процессоры (начиная с Pentium) имеют 64-х разрядную шину данных, поэтому они могут передавать в системную память по 64 бита за один такт. Такая реализация позволяет ускорить обмен данными между быстрым процессором и относительно медленным ОЗУ при неизменной рабочей частоте последнего за счёт повышения пропускной способности шины данных. Разрядность шины данных процессора определяет также разрядность банка памяти. Это значит, что, например, 32-х разрядный процессор (например, 486) считывает из памяти и записывает в память 32 бита одновременно. Процессоры класса Pentium и выше считывают и записывают при операциях с памятью 64 бита одновременно. В современных процессорах внешняя шина данных 64-разрядная, а регистры и внутренняя шина процессора по-прежнему 32-разрядны. В современном процессоре (например, Pentium) для обработки информации, поступающей по внешней 64-разрядной шине данных, существует два обрабатывающих ее 32-разрядных блока, называемых конвейерами. Такой процессор напоминает два объединенных в одном корпусе 32-разрядных процессора, а 64-разрядная внешняя шина данных позволяет быстрее наполнить регистры процессора. Такая архитектура, применяющая для обработки поступивших данных несколько конвейеров, называется суперскалярной и применяется сегодня во всех современных процессорах Шина адреса Шина адреса представляет собой набор проводников, по которым передается адрес ячейки памяти, в которую или из которой пересылаются данные. По каждому проводнику передается один бит адреса, соответствующий одной цифре в адресе. Увеличение количества проводников (разрядов шины) используемых для формирования адреса, позволяет увеличить количество адресуемых ячеек. Разрядность шины адреса определяет максимальный объем памяти, адресуемой процессором. Например: процессор 8086 имел адресную шину 20 бит. Тогда он мог адресовать {2 в степени 20=1048576} байт оперативной памяти, т.е. 1 Мбайт. Таким образом, максимальный объем оперативной памяти, поддерживаемой процессором 8086, составляет 1 Мбайт. 286-ой процессор имел адресную шину равную 24 битам, адресуя, таким образом, уже 16 Мбайт. Современные процессоры имеют адресную шину равной 36 бит, что соответствует поддерживаемой оперативной памяти объемом 64 Гбайт! Процессор Pentium 4 имеет разрядность 64/32, и его адресное пространство составляет 64 Гб. Шины данных и адреса независимы, и разработчики микросхем выбирают их разрядность по своему усмотрению. Разрядность этих шин является показателем возможностей процессора: разрядность шины данных определяет возможности процессора быстро обмениваться информацией, разрядность адресной шины определяет объем поддерживаемой процессором памяти.

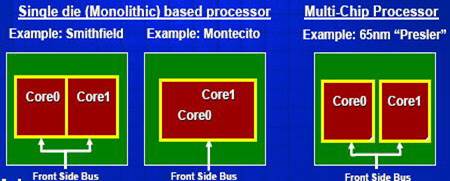

Многоядерная архитектура Количество ядер Число ядер в процессоре. Новая технология изготовления процессоров позволяет разместить в одном корпусе более одного ядра. Наличие нескольких ядер значительно увеличивает производительность процессора. Например, в линейке Core 2 Duo используются двухъядерные процессоры, а в модельном ряду Core 2 Quad - четырехъядерные. Мультиядерность в текущем понимании Intel – это один из трех возможных вариантов:

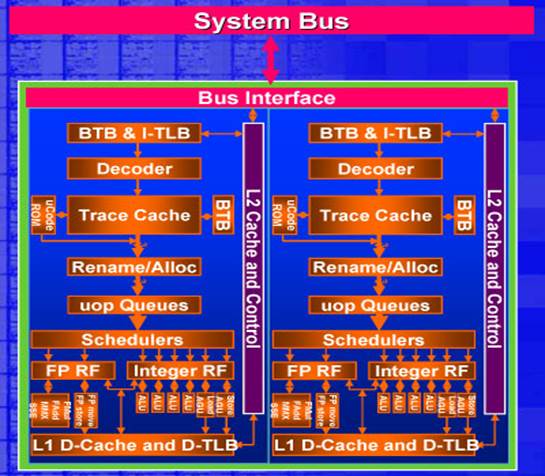

1. Независимые процессорные ядра, каждое со своей кэш-памятью, расположены на одном кристалле и просто используют общую системную шину. Это - 90-нанометровый Pentium D на ядре Smithfield. 2. Похожий вариант – когда несколько одинаковых ядер расположены на разных кристаллах, но объединены вместе в одном корпусе процессора (многочиповый процессор). Это 65-нанометровое поколение процессоров семейств Pentium и Xeon на ядрах Presler и Dempsey. 3. Ядра могут быть тесно переплетены между собой на одном кристалле и использовать некоторые общие ресурсы кристалла (скажем, шину и кэш-память). Таким является Itanium на ядре Montecito.

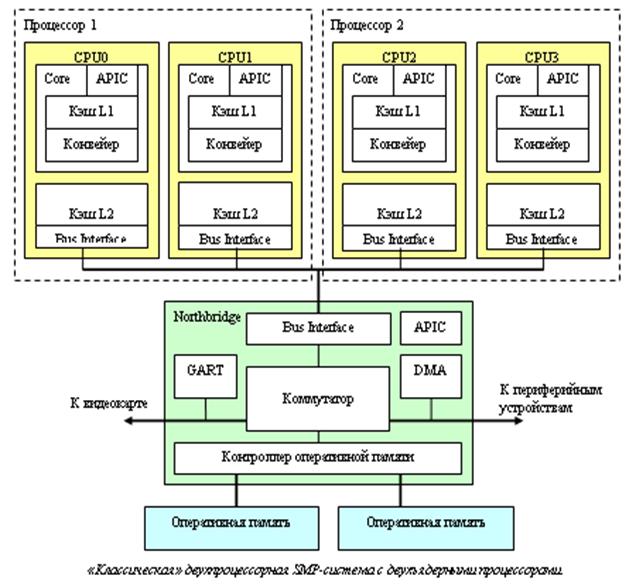

Организация «системы в целом» у Intel столь же традиционна, сколь и устройство двухъядерного процессора. В ней есть несколько «равноправных» центральных процессоров (как правило, разделяющих общую шину); есть оперативная память и есть разной степени быстродействия периферия. Весь этот комплект объединяется в единое целое специальным коммуникационным процессором – «северным мостом» (Northbridge) чипсета. Через него проходят все потоки данных, которые только зарождаются в компьютере. Образно говоря, если «процессоры» - это «головы» компьютера, то северный мост – это его сердце. Подобный «централизованный» подход, во-первых, отличается относительной простотой, а во-вторых, удобен тем, что в нём каждый компонент компьютера получается узкоспециализированным, и поддающимся модернизации независимо от других компонентов. • APIC (Advanced Programmable Interrupt Controller) – одна из важнейших схем любого компьютера. Это схема, занимающаяся сбором и обработкой возникающих в компьютере прерываний. (Как работает? Нажал пользователь клавишу на клавиатуре – контроллер клавиатуры зафиксировал это событие, занес код нажатой клавиши в свою встроенную память – и сгенерировал прерывание – выдал по специальной линии сигнал-запрос с просьбой прервать выполнение текущей программы и обработать событие «нажата клавиша на клавиатуре»). Это «классическая» задача Interrupt Controller -ов: они позволяют процессору не терять зря время, регулярно опрашивая каждое из устройств на предмет того, «а не случилось ли там чего-нибудь за последние 10 мс». Но задачи IC не ограничиваются только этим: помимо аппаратных существуют еще и программные прерывания (exceptions), которые генерирует не периферия, а сам процессор – в случае возникновения какой-либо нештатной ситуации. Реакция на каждое из прерываний задается вектором прерываний – набором адресов в памяти, описывающих «что делать дальше» процессору в случае возникновения прерывания: какие функции (обработчики прерывания) ему в этом случае необходимо выполнять. • DMA (Direct Memory Access) – это своеобразный «альтернативный процессор», который занимается в чипсете обработкой «фоновых» задач, связанных с периферией. • GART (Graphical Address Relocation Table) появился в компьютерах одновременно с шиной AGP: это небольшая схема, которая обеспечивает графическому ускорителю доступ к системной памяти процессора. Её задачи – реализация механизма виртуальной памяти для GPU, то есть отображение «линейного» адресного пространства, с которым работает ускоритель, на «реальное», произвольным образом «перетасованное» с «обычными данными». Позволяет современным 3D-ускорителям использовать не только свою видеопамять, но и «основную» системную память компьютера. Кэширование Кэширование — это использование дополнительной быстродействующей памяти для хранения копий блоков информации из основной (оперативной) памяти, вероятность обращения к которым в ближайшее время велика. Различают кэши 1-, 2- и 3-го уровней (обозначаются L1, L2 и L3 — от Level 1, Level 2 и Level 3). Кэш 1-го уровня имеет наименьшую латентность (время доступа), но малый размер, кроме того, кэши первого уровня часто делаются многопортовыми. Процессоры AMD K8 умели производить одновременно 64-битные запись и чтение, либо два 64-битных чтения за такт. AMD K8L может производить два 128-битных чтения или записи в любой комбинации. Процессоры Intel Core 2 могут производить 128-битные запись и чтение за такт. Кэш 2-го уровня обычно имеет значительно большую латентность доступа, но его можно сделать значительно больше по объему. Кэш 3-го уровня самый большой по объёму и довольно медленный, но всё-же он гораздо быстрее, чем оперативная память. Объем кэша L1 (от 8 до 128 Кб) Объем кэш-памяти первого уровня. Кэш-память первого уровня - это блок высокоскоростной памяти, расположенный прямо на ядре процессора. В него копируются данные, извлеченные из оперативной памяти. Сохранение основных команд позволяет повысить производительность процессора за счет более высокой скорости обработки данных (обработка из кэша быстрее, чем из оперативной памяти). Емкость кэш-памяти первого уровня невелика и исчисляется килобайтами. Обычно "старшие" модели процессоров обладают большим объемом кэша L1. Объем кэша L2 (от 128 до 12288 Кб) Если вы выбираете процессор для ресурсоемких задач, то модель с большим объемом кэша L2 будет предпочтительнее. Объем кэша L3 (от 0 до 16384 Кб) Как правило, кэш-памятью третьего уровня комплектуются только CPU для серверных решений или специальные редакции "настольных" процессоров. Кэш-памятью третьего уровня обладают, например, такие линейки процессоров, как Intel Pentium 4 Extreme Edition, Xeon DP, Itanium 2, Xeon MP и прочие. Частота шины

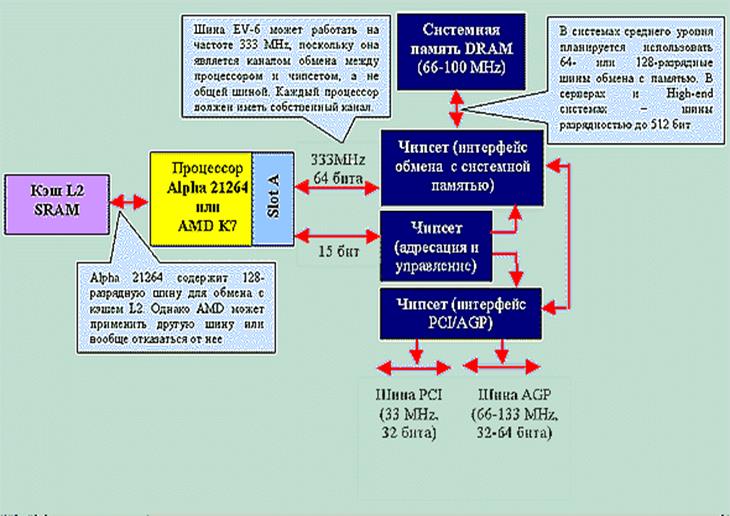

Коэффициент умножения (от 6.0 до 30.0). Значение коэффициента умножения процессора, на основании которого производится расчет конечной тактовой частоты процессора. Для указанных процессоров в поле "Частота шины" приводится эффективная, то есть увеличенная в четыре раза, частота шины. Для получения физической частоты шины нужно эффективную частоту разделить на четыре. Максимальная рабочая температура (от 54.8 до 105 C) Напряжение на ядре (от 0.65 до 1.75 В) Поддержка 3DNow Поддержка AMD64/EM64T Примеры линеек с 64-битной архитектурой: AMD Athlon 64, AMD Opteron, Core 2 Duo, Intel Xeon 64 и прочие. Процессоры с поддержкой 64-битной адресации работают с оперативной памятью свыше 4 Гб, что недоступно традиционным 32-битным CPU. Для использования преимуществ 64-битных процессоров необходимо, чтобы ваша операционная система была адаптирована к ним. Поддержка HT Это значительно повышает эффективность выполнения специфических приложений, связанных с аудио- и видеоредактированием, 3D-моделированием и т.п., а также работы в многозадачном режиме. Однако в некоторых приложениях использование этой технологии может приводить к обратному эффекту, поэтому при необходимости ее можно отключить. Поддержка NX Bit Поддержка SSE2 Поддержка SSE3 Поддержка SSE4 Поддержка Virtualization Technology Сокет Тепловыделение (от 10 до 165 Вт) Техпроцесс Для сравнения, у ядра Willamette, выполненного по техпроцессу 0.18 мкм - 42 миллиона транзисторов, а у ядра Prescott, техпроцесс 0.09 мкм - 125 миллионов. Частота процессора (от 900 до 3800 МГц) Шина EV -6(AMD) Шина компании Advanced Micro Devices (AMD). Для обмена с системной памятью. По словам основателя и исполнительного директора (CEO или Chief Executive Officer) компании Джерри Сандерса (Jerry Sanders), процессор К7, выпушенный в 1999 году в картридже, физически совместим (то есть, имеет такое же количество и расположение контактов) с патентованным разъемом Slot 1 компании Intel. При этом новый разъем компании AMD (рабочее название - Slot A) не будет электрически совместим со Slot 1, то есть AMD не собирается нарушать патенты Intel. В качестве системной шины К7 будет использовать шину ввода/вывода процессора Alpha 21264 (внутреннее название EV-6) компании Digital Equipment. Техника Что же представляет собой эта шина? EV-6 уже работает на частоте 333 MHz,. По этому показателю EV-6 более чем в три раза превосходит 100-мегагерцовые шины Socket 7 и Р6. Кроме того, хотя спецификация EV-6 не определяет специальной шины для обмена с кэшем L2, разработчики могут добавлять ее при необходимости - так, например, "верхние" модели процессора Digital 21264 имеют 128-разрядную дополнительную шину, что в два раза "шире", чем у Pentium II. Возникает вопрос: как удалось заставить EV-6 работать на такой частоте, если переход даже с 66 MHz на 100MHz сопряжен с громадными техническими сложностями. Дело в том, что EV-6, в общем-то, не является шиной в привычном понимании этого слова.

EV-6 же представляет собой просто 64-битный канал обмена между процессором и чипсетом. Каждый процессор в многопроцессорной системе должен иметь свою шину EV-6.

Обмен с системной памятью, PCI и AGP осуществляется чипсетом, причем каждая шина может работать на своей частоте.

Преимущества EV-6 очевидны. Поскольку главным "узким местом" современных процессоров является обмен с системной памятью, повышенная пропускная способность позволит уменьшить время простоя процессора при заполнении линии кэша.

Но при этом просто взять, и поднять частоту шины, увеличив, таким образом, ее пропускную способность весьма непросто. Нужно быть готовым к тому, что имеющееся оборудование наверняка не будет работать с новой частотой шины, и придется разрабатывать новое оборудование. Второй способ увеличить пропускную способность канала обмена в приведенном выше примере еще более прост! Нужно просто добавить еще один (или несколько) проводов, по которым передаются данные! При этом частота остается той же, имеющееся оборудование будет работать, а передача данных происходит параллельно по двум или нескольким проводам. В таком случае говорят об увеличении ширины шины. Если в случае одного провода за один такт периодического сигнала передают один бит, то в случае, когда шина состоит из N проводов, за один такт можно передать N бит, поэтому ширину шины измеряют в битах, а физически это соответствует количеству проводов в шине, использующихся для передачи данных. Итак, говорят о разрядности шины и измеряют ее в битах. Чем больше разрядность, чем больше и пропускная способность шины.

Самой первой шиной для подключения плат расширения была разработанная для самых первых РС шина, названная XT-Bus (еще ее иногда называют ISA8). Это была восьмиразрядная шина, а частота, на которой она работала, составляла всего лишь 4,77 МГц. Столь малая частота работы шины XT-Bus объясняется тем, что и процессор в самом первом компьютере IBM PC работал на частоте 4,77 МГц. Естественно, даже теоретическая пропускная способность такой шины 1байт х 4,77МГц = 4,77Мбайт/с (а реальная производительность шины заметно меньше), не может надолго удовлетворить потребности в пропускной способности, поэтому для новых систем в 1984 году была разработана модификация шины XT-Bus, названная ISA. Шина ISA была 16-разрядной, в отличии от своей восьмиразрядной предшественницы, кроме того частота шины ISA была поднята примерно до 8 МГц. Таким образом, пропускная способность новой шины увеличилась по сравнению с XT-Bus почти вчетверо. В ситуации, когда нужно разработать новую шину для подключения внешних устройств, всегда есть два пути. Путь первый - разработать с нуля новую шину, новый разъем, новую логику работы не имея необходимости тащить за собой недостатки прошлого. И путь второй - разработать новую шину как улучшение предыдущей, сохранив при этом совместимость. Именно второй путь обычно и избирают, если только имеется техническая возможность сделать это.

Дело в том, что разработав и внедрив

новую шину, не совместимую со старой, производитель не вызовет особой радости у пользователя, который, купив новую материнскую плату и процессор, убедится, что все прочие платы расширения, которыми он пользовался ранее, теперь можно выбросить, так как установить их в новый компьютер нельзя. И шина ISA - это улучшенная XT-Bus, сохранившая с XT-Bus совместимость. Естественно, эта совместимость выражается и в организации логики обмена по шине, и в разъеме. Т.е. шина ISA является совместимой с XT-Bus в том смысле, что старую XT-Bus плату можно установить в разъем ISA и она при этом будет работать. Итого: в разъем ISA можно вставить как 16-разрядную, специально разработанную для ISA плату, так и старую, разработанную для XT-Bus плату. Но, разумеется, новая шина удовлетворяет потребности только лишь некоторое время. И затем снова встает вопрос о разработке новой шины для подключения плат расширения. В 1988 году такие фирмы, как Wyse, AST Research, Tandy, Compaq, Hewlett-Packard, Zenith, Olivetti, NEC и Epson предложили 32 - битное расширение шины ISA, так называемую шину EISA. Поскольку дальше удлинять разъем ISA было некуда, разработчики нашли оригинальное решение: новые контакты были размещены между контактами шины ISA и не были доведены до края разъема. Специальная система выступов на разъеме и щелей в EISA-картах позволяла им глубже заходить в разъем и подсоединяться к новым контактам. (Правда, утверждают, что при большом желании можно запихнуть и ISA-карту так, чтобы она замкнула EISA-контакты). Т.е. разъем EISA содержал дополнительные контакты, которые и обеспечивали 32 - битное расширение в глубине. И в разъем EISA можно было вставлять как обычные ISA платы, т.е. обеспечивалась совместимость, так и специально разработанные EISA платы. Однако архитектура EISA не прижилась. Фактически переступив через EISA, индустрия использовала следующую разработку, шину, которая называлась локальная шина VESA, или VL-Bus - VESA Local Bus. Разъем шины VESA состоял из разъема ISA и еще одного блока, обеспечивавшего дополнительные контакты, которые позволяли реализовать по шине VESA 32-битный обмен. Кроме того, разъем VESA работал не на частоте 8 МГц, а на частоте процессора, установленного в системе, что в то время составляло 25-50 МГц! Таким образом, шина была вдвое шире (в смысле разрядности:)), чем ISA, да еще и работала на частоте, в несколько раз большей, обеспечивая огромный рывок вперед по пропускной способности!

Эпоха последовательных шин Итак, ни для кого не секрет что в наше время, идеальный внешний интерфейс, так или иначе, является последовательным. Прошли времена многожильных центрониксов, и толстенных (обухом не перешибешь) SCSI шлангов — фактически, наследия еще до PC-шных времен. Переход происходил медленно, но верно: сначала клавиатура и мышь, затем модем, затем, через годы и годы — сканеры и принтеры, видеокамеры, цифровые фотоаппараты. USB, IEE1394, USB 2. На данный момент, вся потребительская внешняя периферия перебралась на последовательные соединения. Преимущества очевидны — в наше время выгоднее заложить максимум функциональности в чип, нежели иметь дело с избыточными объемами контактов, шлангами с сотней проводов внутри, недешевыми пайкой, экранированием, разводкой и медью.

Сформулируем преимущества последовательных шин и интерфейсов: 1. Выгодный перенос все большей части практической реализации шины на кремний, что облегчает отладку, повышает гибкость и сокращает время разработки; 2. Перспектива органично использовать в будущем иные носители сигнала, например оптические; 3. Экономия пространства и снижение сложности монтажа; 4. Проще реализовывать горячие подключения и динамическую конфигурацию в любом смысле; 5. Возможность выделять гарантированные каналы; 6. Переход от разделяемых шин с арбитражем и непредсказуемыми прерываниями, неудобными для надежных/критических систем к более предсказуемым соединениям точка-точка; 7. Лучшая с точки зрения затрат и более гибкая с точки зрения топологии масштабируемость;

В будущем же следует ожидать массового перехода на беспроводные шины. Обсудим все преимущества на конкретном примере — новой стандартной системной шине PCI Express, массовое распространение которой на сегмент PC и средних/малых серверов уже наблюдается. PCI Express · Последовательная системная шина общего назначения; · Имя — PCI Express, на стадии проектирования была также известна как 3GIO (Ввод-вывод третьего поколения), причем оба названия (3GIO и PCI Express) являются зарегистрированными торговыми марками; · Дата рождения — 22 июля 2002 года — опубликована базовая спецификация протокола и сигнального уровня, а также базовая спецификация и энергопотребление карт и разъемы; · Фактически — совокупность независимых самостоятельных последовательных каналов передачи данных; · Сигнальный уровень 0.8 вольт. Каждый канал состоит из двух дифференциальных сигнальных пар (необходимо только 4 контакта): ·

· Используется избыточное защищенное от помех кодирование — каждый байт при передаче представляется десятью битами; · Пропускная способность 2.5 Гигабита (250 МБ) в секунду для одного канала в каждом направлении одновременно (полный дуплекс), однако, следует учесть, что эффективная скорость передачи данных за вычетом избыточного кодирования составляет 2 Гигабита (200 МБ) ровно; · Стандартизированы 1, 2, 4, 8, 16 и 32 канальные варианты (до 6.4 эффективных Гигабайт в секунду соответственно, при передаче в одну сторону и вдвое больше при передаче в обоих направлениях). При передаче данных они передаются параллельно (но не синхронно) по всем доступным каналам:

· Вся контрольная информация передается по тем же линиям что и данные, используется стек протоколов, из нескольких уровней, включая маршрутизацию данных:

· Стандарт предусматривает и альтернативные носители сигнала, такие как оптические волноводы; · Возможность динамического подключения и конфигурации устройств; · Возможность распознавания и использования альтернативных (улучшенных) протоколов обмена. · Термины- характеристики современных процессоров

Ядро Внутренняя шина и регистры процессора Хоть процессор и получает данные из оперативной памяти с помощью некоторой ширины, это не значит, что внутри он может обрабатывать данные такой же разрядности.

|

||||||||||||||

|

Последнее изменение этой страницы: 2021-01-09; просмотров: 1095; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.14.134.31 (0.013 с.) |

|||||||||||||||