Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Другим новшеством Р6 является архитектура двойной независимой шины.Содержание книги

Поиск на нашем сайте Процессор имеет две шины данных: одну - для системы (системной платы), другую - для кэш-памяти. Благодаря этому существенно повысилось быстродействие кэш-памяти. Для обхода узкого места — внешней шины — в Р6 применена архитектура двойной независимой шины DIB (Dual Independent Bus), реализующая, по сути, две отдельные шины. Одна из этих шин используется только для связи с кристаллом вторичного кэша, расположенным в том же корпусе микросхемы или картридже, что и процессор. Эта шина является локальной в геометрическом смысле — проводники имеют длину порядка единиц сантиметров, что позволяет использовать ее на высокой частоте тактирования, вплоть до частоты ядра. Значительный объем вторичного кэша обеспечивает удовлетворение большинства запросов к памяти сугубо локально, при этом коэффициент загрузки внутренней щины достигает 90 %. Вторая шина процессорного кристалла выходит на внешние выводы микросхемы (картриджа), и является системной, или «фасадной» шиной FSB (Front-Side Bus) процессорa P6. Эта шина работает на внешней частоте независимо от внутренней шины. Пo статистике работы с приложениями середины 90-х годов загрузка процессором внешней шины для обычных «настольных» применений составляет порядка 10 % от ее пропускной способности, а для серверных применений может достигать 60 % при четырехпроцессорной конфигурации. Таким образом, ограниченная пропускная способность внешней шины (533 Мбайт/с при 66,67 МГц и 1064 Мбайт/с при 133 МГц в пике пакетной передачи) перестает служить фактором, обесценивающим производительность процессора. Однако для современных процессоров и приложений и этой пропускной способности уже не хватает. Снижение нагрузки на внешнюю шину позволяет эффективно использовать многопроцессорную архитектуру. Системная шина P6 более эффективна для объединения процессоров по симметричной архитектуре, чем шины предыдущих процессоров, оптимизированные для обмена с памятью. Она позволяет без дополнительных схем объединять до четырех процессоров, хотя в обычных процессорах Pentium II/III возможности объединения урезаны до двух. Процессоры поколения Р5 имели только одиночную шину процессора на системной плате, и все данные, включая передаваемые в кэш и из него, передавались по ней. Основная проблема состояла в том, что быстродействие кэш-памяти было ограничено тактовой частотой шины системной платы, которая равнялась 66 МГц. В процессорах шестого поколения кэш-память может работать на тактовой частоте 500 МГц или выше, а оперативная память (SDRAM) - с тактовой частотой 66 и 100 МГц, в силу этого возникла необходимость поместить кэш второго уровня ближе к процессору. Было принято решение подсоединить к процессору дополнительную шину, называемую специализированной (или выделенной) шиной кэша. Кэш-память второго уровня была соединен с этой шиной и могла работать на любой тактовой частоте. Сначала это было реализовано в Pentium Pro, где кэш-память второго уровня была установлена в корпусе процессора и работала на его тактовой частоте, а не на частоте системной шины. Однако такое решение оказалось слишком дорогостоящим, и поэтому кэш-память второго уровня была перемещен из корпуса процессора на картридж, в который упаковывается Pentium II. В этом случае шина кэша могла работать на любой тактовой частоте, и вначале она работала на частоте, вдвое меньшей тактовой частоты процессора. При наличии кэша на дополнительной шине, непосредственно соединенной с процессором, его быстродействие соизмеримо с быстродействием процессора. Если бы быстродействие кэша ограничивалось тактовой частотой системной платы (например, 66 или 100 МГц), как в случае использования гнезда типа Socket 7 (процессор Р5), тактовая частота кэш-памяти была бы равна 66 МГц, даже если частота процессора равнялась бы 333 МГц; на более новых платах кэш "увяз" бы на тактовой частоте 100 МГц при частоте процессора 500 МГц и выше. По мере роста тактовой частоты процессора с двойной независимой шиной за счет более высоких множителей тактовой частоты системной платы быстродействие кэша увеличивается то же количество раз, что и тактовая частота процессора. Другими словами, быстродействие кэш-памяти на двойной независимой шине увеличивается пропорционально быстродействию процессора! Архитектура двойной независимой шины необходима для повышения эффективности процессора, работающего на тактовой частоте 300 МГц и выше. Со старым гнездом типа Socket 7 (для процессоров Р5) таких тактовых частот достичь было невозможно и пришлось бы нести огромные потери в эффективности из-за медленной (привязанной к тактовой частоте системной платы) кэш-памяти второго уровня. Именно поэтому тактовая частота процессоров Pentium класса Р5 не превосходит 266 МГц; процессоры Р6 работают на тактовых частотах 1000 МГц и выше. Кроме того, в архитектуре Р6 были расширены вычислительные возможности суперскаляра процессоров Р5: добавлены новые устройства выполнения команд, а команды разбиты на специальные микрооперации. Р5 имел только два модуля выполнения команд, в то время как Р6 имеет не менее шести отдельных специализированных (выделенных) модулей. Такой суперскаляр называется трехконвейерным (множественные модули выполнения команд могут выполнять до трех команд в одном цикле). Помимо всего прочего, в архитектуру Р6 встроена поддержка многопроцессорной системы, усовершенствованы средства обнаружения и исправления ошибок, а также оптимизировано выполнение 32-разрядного программного обеспечения.

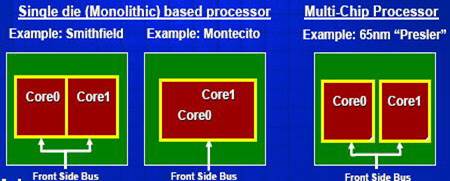

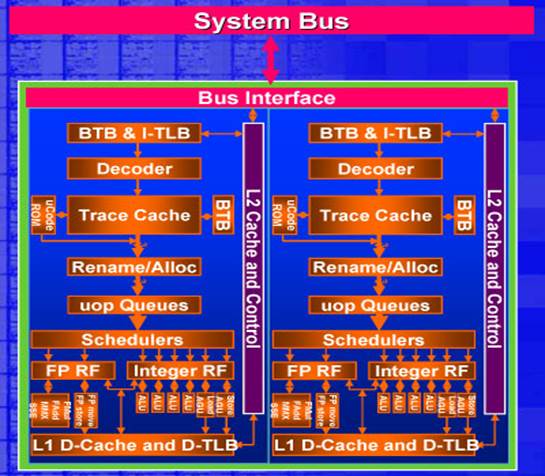

Многоядерная архитектура Количество ядер Число ядер в процессоре. Новая технология изготовления процессоров позволяет разместить в одном корпусе более одного ядра. Наличие нескольких ядер значительно увеличивает производительность процессора. Например, в линейке Core 2 Duo используются двухъядерные процессоры, а в модельном ряду Core 2 Quad - четырехъядерные. Мультиядерность в текущем понимании Intel – это один из трех возможных вариантов:

1. Независимые процессорные ядра, каждое со своей кэш-памятью, расположены на одном кристалле и просто используют общую системную шину. Это - 90-нанометровый Pentium D на ядре Smithfield. 2. Похожий вариант – когда несколько одинаковых ядер расположены на разных кристаллах, но объединены вместе в одном корпусе процессора (многочиповый процессор). Это 65-нанометровое поколение процессоров семейств Pentium и Xeon на ядрах Presler и Dempsey. 3. Ядра могут быть тесно переплетены между собой на одном кристалле и использовать некоторые общие ресурсы кристалла (скажем, шину и кэш-память). Таким является Itanium на ядре Montecito.

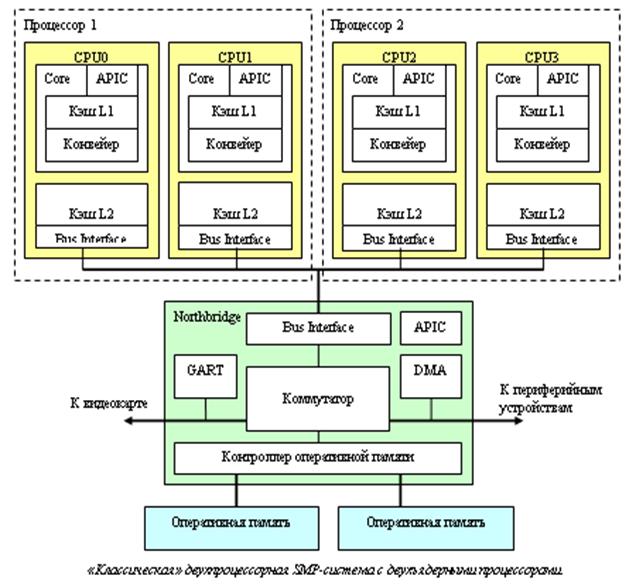

Организация «системы в целом» у Intel столь же традиционна, сколь и устройство двухъядерного процессора. В ней есть несколько «равноправных» центральных процессоров (как правило, разделяющих общую шину); есть оперативная память и есть разной степени быстродействия периферия. Весь этот комплект объединяется в единое целое специальным коммуникационным процессором – «северным мостом» (Northbridge) чипсета. Через него проходят все потоки данных, которые только зарождаются в компьютере. Образно говоря, если «процессоры» - это «головы» компьютера, то северный мост – это его сердце. Подобный «централизованный» подход, во-первых, отличается относительной простотой, а во-вторых, удобен тем, что в нём каждый компонент компьютера получается узкоспециализированным, и поддающимся модернизации независимо от других компонентов. • APIC (Advanced Programmable Interrupt Controller) – одна из важнейших схем любого компьютера. Это схема, занимающаяся сбором и обработкой возникающих в компьютере прерываний. (Как работает? Нажал пользователь клавишу на клавиатуре – контроллер клавиатуры зафиксировал это событие, занес код нажатой клавиши в свою встроенную память – и сгенерировал прерывание – выдал по специальной линии сигнал-запрос с просьбой прервать выполнение текущей программы и обработать событие «нажата клавиша на клавиатуре»). Это «классическая» задача Interrupt Controller -ов: они позволяют процессору не терять зря время, регулярно опрашивая каждое из устройств на предмет того, «а не случилось ли там чего-нибудь за последние 10 мс». Но задачи IC не ограничиваются только этим: помимо аппаратных существуют еще и программные прерывания (exceptions), которые генерирует не периферия, а сам процессор – в случае возникновения какой-либо нештатной ситуации. Реакция на каждое из прерываний задается вектором прерываний – набором адресов в памяти, описывающих «что делать дальше» процессору в случае возникновения прерывания: какие функции (обработчики прерывания) ему в этом случае необходимо выполнять. • DMA (Direct Memory Access) – это своеобразный «альтернативный процессор», который занимается в чипсете обработкой «фоновых» задач, связанных с периферией. • GART (Graphical Address Relocation Table) появился в компьютерах одновременно с шиной AGP: это небольшая схема, которая обеспечивает графическому ускорителю доступ к системной памяти процессора. Её задачи – реализация механизма виртуальной памяти для GPU, то есть отображение «линейного» адресного пространства, с которым работает ускоритель, на «реальное», произвольным образом «перетасованное» с «обычными данными». Позволяет современным 3D-ускорителям использовать не только свою видеопамять, но и «основную» системную память компьютера. Кэширование Кэширование — это использование дополнительной быстродействующей памяти для хранения копий блоков информации из основной (оперативной) памяти, вероятность обращения к которым в ближайшее время велика. Различают кэши 1-, 2- и 3-го уровней (обозначаются L1, L2 и L3 — от Level 1, Level 2 и Level 3). Кэш 1-го уровня имеет наименьшую латентность (время доступа), но малый размер, кроме того, кэши первого уровня часто делаются многопортовыми. Процессоры AMD K8 умели производить одновременно 64-битные запись и чтение, либо два 64-битных чтения за такт. AMD K8L может производить два 128-битных чтения или записи в любой комбинации. Процессоры Intel Core 2 могут производить 128-битные запись и чтение за такт. Кэш 2-го уровня обычно имеет значительно большую латентность доступа, но его можно сделать значительно больше по объему. Кэш 3-го уровня самый большой по объёму и довольно медленный, но всё-же он гораздо быстрее, чем оперативная память. Объем кэша L1 (от 8 до 128 Кб) Объем кэш-памяти первого уровня. Кэш-память первого уровня - это блок высокоскоростной памяти, расположенный прямо на ядре процессора. В него копируются данные, извлеченные из оперативной памяти. Сохранение основных команд позволяет повысить производительность процессора за счет более высокой скорости обработки данных (обработка из кэша быстрее, чем из оперативной памяти). Емкость кэш-памяти первого уровня невелика и исчисляется килобайтами. Обычно "старшие" модели процессоров обладают большим объемом кэша L1. Объем кэша L2 (от 128 до 12288 Кб) Если вы выбираете процессор для ресурсоемких задач, то модель с большим объемом кэша L2 будет предпочтительнее. Объем кэша L3 (от 0 до 16384 Кб) Как правило, кэш-памятью третьего уровня комплектуются только CPU для серверных решений или специальные редакции "настольных" процессоров. Кэш-памятью третьего уровня обладают, например, такие линейки процессоров, как Intel Pentium 4 Extreme Edition, Xeon DP, Itanium 2, Xeon MP и прочие. Частота шины

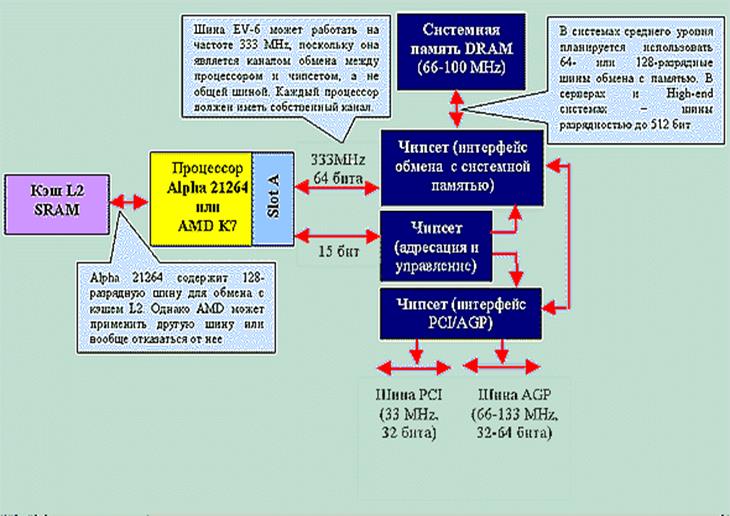

Коэффициент умножения (от 6.0 до 30.0). Значение коэффициента умножения процессора, на основании которого производится расчет конечной тактовой частоты процессора. Для указанных процессоров в поле "Частота шины" приводится эффективная, то есть увеличенная в четыре раза, частота шины. Для получения физической частоты шины нужно эффективную частоту разделить на четыре. Максимальная рабочая температура (от 54.8 до 105 C) Напряжение на ядре (от 0.65 до 1.75 В) Поддержка 3DNow Поддержка AMD64/EM64T Примеры линеек с 64-битной архитектурой: AMD Athlon 64, AMD Opteron, Core 2 Duo, Intel Xeon 64 и прочие. Процессоры с поддержкой 64-битной адресации работают с оперативной памятью свыше 4 Гб, что недоступно традиционным 32-битным CPU. Для использования преимуществ 64-битных процессоров необходимо, чтобы ваша операционная система была адаптирована к ним. Поддержка HT Это значительно повышает эффективность выполнения специфических приложений, связанных с аудио- и видеоредактированием, 3D-моделированием и т.п., а также работы в многозадачном режиме. Однако в некоторых приложениях использование этой технологии может приводить к обратному эффекту, поэтому при необходимости ее можно отключить. Поддержка NX Bit Поддержка SSE2 Поддержка SSE3 Поддержка SSE4 Поддержка Virtualization Technology Сокет Тепловыделение (от 10 до 165 Вт) Техпроцесс Для сравнения, у ядра Willamette, выполненного по техпроцессу 0.18 мкм - 42 миллиона транзисторов, а у ядра Prescott, техпроцесс 0.09 мкм - 125 миллионов. Частота процессора (от 900 до 3800 МГц) Шина EV -6(AMD) Шина компании Advanced Micro Devices (AMD). Для обмена с системной памятью. По словам основателя и исполнительного директора (CEO или Chief Executive Officer) компании Джерри Сандерса (Jerry Sanders), процессор К7, выпушенный в 1999 году в картридже, физически совместим (то есть, имеет такое же количество и расположение контактов) с патентованным разъемом Slot 1 компании Intel. При этом новый разъем компании AMD (рабочее название - Slot A) не будет электрически совместим со Slot 1, то есть AMD не собирается нарушать патенты Intel. В качестве системной шины К7 будет использовать шину ввода/вывода процессора Alpha 21264 (внутреннее название EV-6) компании Digital Equipment. Техника Что же представляет собой эта шина? EV-6 уже работает на частоте 333 MHz,. По этому показателю EV-6 более чем в три раза превосходит 100-мегагерцовые шины Socket 7 и Р6. Кроме того, хотя спецификация EV-6 не определяет специальной шины для обмена с кэшем L2, разработчики могут добавлять ее при необходимости - так, например, "верхние" модели процессора Digital 21264 имеют 128-разрядную дополнительную шину, что в два раза "шире", чем у Pentium II. Возникает вопрос: как удалось заставить EV-6 работать на такой частоте, если переход даже с 66 MHz на 100MHz сопряжен с громадными техническими сложностями. Дело в том, что EV-6, в общем-то, не является шиной в привычном понимании этого слова.

EV-6 же представляет собой просто 64-битный канал обмена между процессором и чипсетом. Каждый процессор в многопроцессорной системе должен иметь свою шину EV-6.

Обмен с системной памятью, PCI и AGP осуществляется чипсетом, причем каждая шина может работать на своей частоте.

Преимущества EV-6 очевидны. Поскольку главным "узким местом" современных процессоров является обмен с системной памятью, повышенная пропускная способность позволит уменьшить время простоя процессора при заполнении линии кэша.

|

||||||||||||

|

Последнее изменение этой страницы: 2021-01-09; просмотров: 179; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.221.161.43 (0.014 с.) |

|||||||||||||