Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Красноярский институт железнодорожного транспорта –Содержание книги

Поиск на нашем сайте Красноярский институт железнодорожного транспорта – филиал ФГБОУ ВО «Иркутский государственный университет путей сообщения» В.С. Ратушняк Е.С. Ильин МИКРОПРОЦЕССОРНЫЕ ИНФОРМАЦИОННО-УПРАВЛЯЮЩИЕ СИСТЕМЫ Учебно-методическое пособие к лабораторным работам для студентов очной/заочной формы обучения направления подготовки 23.05.05 «Системы обеспечения движения поездов» специализация №1 "Электроснабжение железных дорог" специализация №2 "Автоматика и телемеханика на железнодорожном транспорте" Красноярск КрИЖТ ИрГУПС 2018

УДК ББК

Ратушняк, В.С., Микропроцессорные информационно-управляющие системы: учебно-методическое пособие к лабораторным работам для студентов очной/заочной формы обучения для специальности 23.05.05 «Системы обеспечения движения поездов»/ В.С. Ратушняк., Е.С. Ильин - Красноярск. КрИЖТ ИрГУПС. - 2018. - 115с.

Методические указания к лабораторным работам для студентов очной/заочной формы обучения разработаны на основе рабочей программы учебной дисциплины Б1.Б.1.32 «Микропроцессорные информационно-управляющие системы» для специальности 23.05.05 «Системы обеспечения движения поездов».

Рекомендовано к изданию методическим советом КрИЖТ ИрГУПС.

Печатается в авторской редакции.

© В.С. Ратушняк, 2018 © Е.С. Ильин, 2018 © Красноярский институт железнодорожного транспорта, 2018 Содержание Введение. 4 Методические указания для подготовки студента к лабораторным занятиям.. 5 Теоретический материал. 6 РАБОТА №1 МИКРОКОНТРОЛЛЕР ATmega103: методы адресации, команды передачи данных и управления. 18 РАБОТА №2 МИКРОКОНТРОЛЛЕР ATmega103: команды обработки данных. 34 РАБОТА №3 ЦИФРОВЫЕ СИСТЕМЫ НА БАЗЕ МИКРОКОНТРОЛЛЕРА ATmega103: контроль внешних устройств через параллельные порты - работа с клавиатурой. 41 РАБОТА №4 ЦИФРОВЫЕ СИСТЕМЫ НА БАЗЕ МИКРОКОНТРОЛЛЕРА ATmega103: реализация и обслуживание подсистемы прерываний. 55 РАБОТА №5 ЦИФРОВЫЕ СИСТЕМЫ НА БАЗЕ МИКРОКОНТРОЛЛЕРА ATmega103: реализация таймерных функций. 66 РАБОТА №6 ЦИФРОВЫЕ СИСТЕМЫ НА БАЗЕ МИКРОКОНТРОЛЛЕРА ATmega103: организация последовательного обмена данными. 89 РАБОТА №7 ЦИФРОВЫЕ СИСТЕМЫ НА БАЗЕ МИКРОКОНТРОЛЛЕРА ATmega103: обслуживание АЦП и аналогового компаратора. 102 Приложение. 111 Заключение. 114 СПИСОК РЕКОМЕНДОВАННЫХ ИНФОРМАЦИОННЫХ РЕСУРСОВ.. 114

Введение Данные методические указания к лабораторным работам по дисциплине Б1.Б.1.32 «Микропроцессорные информационно-управляющие системы» предназначены для студентов специальности 23.05.05 «Системы обеспечения движения поездов». Цель методических указаний: помочь студенту в изучении материала лабораторных работ и подготовке к промежуточной аттестации. В указаниях подробно изложены темы лабораторных работ, с указанием целей, списка необходимых навыков. К каждой лабораторной работе указаны контрольные вопросы для защиты, на которые необходимо ответить для успешной защиты работы и для усвоения дисциплины в целом.

В результате освоения дисциплины «Микропроцессорные информационно-управляющие системы» студент должен достигнуть результатов образования перечисленных ниже.

Студент должен знать: 1 Виды представления числовой информации в микропроцессорных системах 2 Схемотехнику выходных портов микроконтроллера 3 Типы нагрузок, подключаемых к выводам микроконтроллера 4 Общую структуру микропроцессорной системы, этапы и содержание этапов проектирования микропроцессорной системы 5 Аппаратные средства и систему команд микроконтроллера, языки программирования, возможности интегрированной системы программирования 6 Организацию связи микроконтроллера с внешней средой и временем, вспомогательные аппаратные средства микроконтроллера.

Студент должен уметь: 1. Представлять числовую информацию в заданном виде и анализировать цифровые коды ее представления 2. Составлять схемы подключения к портам микроконтроллера различных нагрузок 3. Составлять схемы микропроцессорных устройств 4. Осуществлять программное управление элементами микроконтроллера 5. Осуществлять программное управление микропроцессорными устройствами 6. Осуществлять расчет и проектирование микропроцессорных устройств.

Студент должен владеть: 1. Навыками составления схем подключения к портам микроконтроллера различных нагрузок 2. Навыками составления схем с применением микроконтроллера 3. Навыками составления схем микропроцессорных систем 4. Основами расчета параметров работы элементов микроконтроллера 5. Основами расчета параметров работы микропроцессорных устройств 6. Основами проектирования микропроцессорных устройств.

Методические указания для подготовки студента к лабораторным занятиям

Методы и этапы работы Целью лабораторных занятий выступает обеспечение понимания теоретического материала учебного курса и его включение в систему знаний студентов, формирование операциональной компоненты готовности специалиста, развитие различных составляющих его профессиональной компетентности. Основой лабораторного практикума выступают типовые задачи, которые должен уметь решать специалист в своей профессиональной деятельности. Проведение лабораторной работы с целью осмысления нового учебного материала включает в себя следующие этапы: - постановку темы занятий и определение цели лабораторной работы; - определение порядка проведения лабораторной работы или отдельных ее этапов; - непосредственное выполнение лабораторной работы студентами и контроль преподавателя за ходом занятий и соблюдением техники безопасности; - подведение итогов лабораторной работы и формулирование основных выводов; - защита лабораторной работы. На первом занятии преподаватель знакомит студентов с общими правилами работы в лаборатории, техникой безопасности и структурой оформления лабораторной работы. Знакомит студента с процедурой защиты работы, обращает внимание студента на то, что оформленная работа должна завершаться формированием библиографического списка. Лабораторный практикум позволяет создать условия для успешного применения студентами теоретических знаний на практике, освоению техники натурного или вычислительного эксперимента, формированию у них аналитических способностей и логического мышления.

Структура оформления лабораторной работы Перед началом выполнения лабораторного практикума преподаватель информирует студентов о порядке оформления лабораторных работ. Если лабораторная работа выполняется на компьютере, отчет по решению преподавателя может быть представлен в одном из видов: - в текстовом редакторе с необходимыми рисунками, таблицами и формулами, - на листах формата А4, скрепленных между собой. Студент должен придерживаться следующей структуры оформления лабораторной работы: - титульный лист с темой лабораторной работы, датой выполнения и фамилией студента; - цель работы; - теоретическая часть (изложение основных теоретических положений изучаемой темы, формулировка законов, запись формул); - экспериментальная часть, включающая описание опытов, или результат выполнения вычислительного (виртуального) эксперимента на компьютере; - выводы (таблицы, графики, итоговые обобщения). После окончания работы студент приводит в порядок рабочее место и сдает преподавателю.

Проверка и защита лабораторных работ В ходе проверки преподаватель: - выявляет соблюдение структуры оформления лабораторной работы; - если работы сдаются в тетради, на полях четко описывает направления доработки или переработки (в случае необходимости); - делает отметку о допуске (не допуске) к защите. Защита лабораторной работы осуществляется в форме сократического диалога сразу после ее выполнения или на следующем занятии. В процессе защиты преподаватель должен: - убедиться в достаточной степени самостоятельности выполнения студентом работы, для чего задать вопросы по методике эксперимента и расчета отдельных показателей и критериев оценки полученных результатов; - убедиться в компетенциях студента, то есть в знаниях и умениях, приобретенных на лабораторных занятиях; - поставить подпись в конце оформленной работы с указанием даты. Теоретический материал В цикле работ данного курса студенты знакомятся с архитектурой 8-разрядного микроконтроллера ATmegal03, изучают систему его команд и методы адресации, осваивают интегрированную систему программирования, получают практические навыки программирования микроконтроллерных систем на языке Ассемблер. Микроконтроллер ATmegal03 является старшей моделью семейства AVR фирмы Atmel. Семейство AVR удачно воплощает современные тенденции архитектуры RISC микроконтроллеров, что в сочетании с достижениями фирмы Atmel в области создания Flash-памяти, сделало его весьма популярным на мировом рынке 8-разрядных микроконтроллеров. Семейство AVR включает около двух десятков типов 8-разрядных микроконтроллеров трех основных линий: - Tiny AVR представляют собой низкостоимостные микроконтроллеры в 8- выводном корпусе. Ихособенностью является встроенная схема контроля напряжения питания; - Classic AVR являются основной линией семейства.Быстродействие некоторых моделей достигает 16 MIPS, Flash ROM программ 2-8 Кбайт, EEPROM данных 64-512 байт, ОЗУ данных 128-512 байт; - Mega AVR представляют собой старшую модель, ориентированную на высокопроизводительную работу со сложными задачами, требующими больших ресурсов памяти. Flash ROM программ составляет 64-128 Кбайт, EEPROM данных 64-512 байт, ОЗУ данных 2-4 Кбайт. Имеются 10- разрядный АЦП и аналоговый компаратор. В составе семейства существуют модификации с низковольтным питанием (ЗВ). Благодаря универсальности, широкому набору функциональных возможностей, высоким техническим характеристикам микроконтроллеры семейства AVR находят все более широкое применение в системах управления различными объектами. Все микроконтроллеры семейства AVR имеют общие принципы функционирования, реализуют единую систему команд, используют одинаковые методы адресации. Изучаемый в данном практикуме микроконтроллер ATmegal03 является типичным представителем семейства AVR. Знакомство с ним позволит освоить основные методы проектирования, программирования и применения систем управления на базе современных RISC микроконтроллеров.

Структура и функционирование микроконтроллера ATmegal03 Структура микроконтроллера ATmega103 включает следующие функциональные блоки: - 8-разрядное арифметическо-логическое устройство (АЛУ); - внутреннюю flash-память программ объемом 128 Кбайт с возможностью внутрисистемного программирования через последовательный интерфейс; - 32 регистра общего назначения; - внутреннюю EEPROM память данных объемом 4 Кбайт; - внутреннее ОЗУ данных объемом 4 Кбайт; - 6 параллельных 8-разрядных портов; - 3 программируемых таймера-счетчика; - 10-разрядный 8-канальный АЦП и аналоговый компаратор; - последовательные интерфейсы UART и SPI; - блоки прерывания и управления (включая сторожевой таймер). На рисунке 1 изображен корпус и приведено назначение выводов микроконтроллера ATmegal03. В скобках указана альтернативная функция вывода, если она существует. Port А (РА7..РА). 8-разрядный двунаправленный порт. К выводам порта могут быть подключены встроенные нагрузочные резисторы (отдельно к каждому разряду). Выходные буферы обеспечивают ток 20 мА и способны прямо управлять светодиодным индикатором. При использовании выводов порта в качестве входов и установке внешнего сигнала в низкое состояние, ток будет вытекать только при подключенных встроенных нагрузочных резисторах. Порт А при наличии внешней памяти данных используется для организации мультиплексируемой шины адреса/данных. Port В (РВ7..РВ0). 8-разрядный двунаправленный порт со встроенными нагрузочными резисторами. Выходные буферы обеспечивают ток 20 мА. При использовании выводов порта в качестве входов и установке внешнего сигнала в низкое состояние, ток будет вытекать только при подключенных встроенных нагрузочных резисторах. Порт В используется также при реализации специальных функций. Port С (РС7..РС0). Порт С является 8-разрядным выходным портом. Выходные буферы обеспечивают ток 20 мА. Порт С при наличии внешней памяти данных используется для организации шины адреса.

Рисунок 1 – Вид корпуса и назначение выводов микроконтроллера ATmega103.

Port D (PD 7.. PD 0). 8-разрядный двунаправленный порт со встроенными нагрузочными резисторами. Выходные буферы обеспечивают ток 20 мА. При использовании выводов порта в качестве входов и установке внешнего сигнала в низкое состояние, ток будет вытекать только при подключенных встроенных нагрузочных резисторах. Порт D используется также при реализации специальных функций. Port Е (РЕ7..РЕ0). 8-разрядный двунаправленный порт со встроенными нагрузочными резисторами. Выходные буферы обеспечивают ток 20 мА. При использовании выводов порта в качестве входов и установке внешнего сигнала в низкое состояние, вытекающий через них ток обеспечивается только при подключенных встроенных нагрузочных резисторах. Порт Е используется также при реализации специальных функций. Port F (PF 7.. PF 0). 8-разрядный входной порт. Входы порта используются также как аналоговые входы аналого-цифрового преобразователя. RESET. Вход сброса. Для выполнения сброса необходимо удерживать низкий уровень на входе более 50 нс. XTAL 1, XTAL 2. Вход и выход инвертирующего усилителя генератора тактовой частоты. TOSC 1, TOSC 2. Вход и выход инвертирующего усилителя генератора таймера/счетчика. WR #, RD #. Стробы записи и чтения внешней памяти данных. ALE. Строб разрешения фиксации адреса внешней памяти. Строб ALE используется для фиксации младшего байта адреса с выводов AD0-AD7 в защелке адреса в течение первого цикла обращения. В течение второго цикла обращения выводы AD0-AD7 используются для передачи данных. AVCC. Напряжение питания аналого-цифрового преобразователя. Вывод подсоединяется к VCC через низкочастотный фильтр. AREF. Вход опорного напряжения для аналого-цифрового преобразователя. На этот вывод подается напряжение в диапазоне между AGND и AVCC. AGND. Это вывод должен быть подсоединен к отдельной аналоговой земле, если она есть на плате. В ином случае вывод подсоединяется к общей земле. PEN #. Вывод разрешения программирования через последовательный интерфейс. При удержании сигнала на этом выводе на низком уровне после включения питания, прибор переходит в режим программирования по последовательному каналу. VCC, GND. Напряжение питания и земля Микроконтроллеры AVR имеют раздельные пространства адресов памяти программ и данных (гарвардская архитектура). Организация памяти показана на рисунке 2.

Рисунок 2 – Организация памяти микроконтроллера ATmega103.

Высокие характеристики семейства AVR обеспечиваются следующими особенностями архитектуры: В качестве памяти программ используется внутренняя flash-память. Она организована в виде матрицы 16-разрядных ячеек и может загружаться программатором, либо через порт SPI; Система команд включает 120 инструкций. Все инструкции 16 и 32-разрядные; 16-разрядные память программ и шина команд вместе с одноуровневым конвейером позволяют выполнить большинство инструкций за один такт синхрогенератора (50 не при частоте FOSC=20 МГц); память данных имеет 8-разрядную организацию. Младшие 32 адреса пространства занимают регистры общего назначения, далее следуют 64 адреса регистров ввода- вывода, затем внутреннее ОЗУ данных объемом до 4000 ячеек. Возможно применение внешнего ОЗУ данных объемом до 60 Кбайт; внутренняя энергонезависимая память типа EEPROM объемом до 4 Кбайт представляет собой самостоятельную матрицу, обращение к которой осуществляется через специальные регистры ввода-вывода; Как видно из рисунке В2, 32 регистра общего назначения включены в сквозное адресное пространство ОЗУ данных и занимают младшие адреса. Хотя физически регистры выделены из памяти данных, такая организация обеспечивает гибкость в работе. Файл регистров общего назначения прямо связан с АЛУ, каждый из регистров способен работать как аккумулятор. Большинство команд выполняются за один такт, при этом из регистров файла могут быть выбраны два операнда, выполнена операция и результат возвращен в регистровый файл. Старшие шесть регистров файла могут использоваться как три 16-разрядных регистра, и выполнять роль, например, указателей при косвенной адресации (рисунок З).

Рисунок 3 – Регистры общего назначения микроконтроллера ATmega103. Следующие 64 адреса за регистрами общего назначения занимают регистры ввода-вывода. В этой области сгруппированы все регистры данных, управления и статуса внутренних программируемых блоков ввода-вывода. При использовании команд IN и OUT используются адреса ввода-вывода с $00 по $3F. Но к регистрам ввода-вывода можно обращаться и как к ячейкам внутреннего ОЗУ. При этом к непосредственному адресу ввода-вывода прибавляется $20. Адрес регистра как ячейки ОЗУ приводится далее в круглых скобках. Регистры ввода-вывода с $00 ($20) по $1F ($3F) имеют программно доступные биты. Обращение к ним осуществляется командами SBI и CBI, а проверка состояния - командами SBIS и SBIC. В таблице 1 приведен список регистров ввода- вывода.

Таблица 1 – Регистры ввода-вывода микроконтроллера ATmega103.

В пространстве регистров ввода-вывода находятся и регистры управления процессором микроконтроллера: регистр состояния, указатель стека, регистр выбора страницы, регистр управления процессором, регистр управления коэффициентом деления частот. Формат этих регистров следующий:

Регистр состояния SREG (Рисунок 4). Рисунок 4 - Регистр состояния SREG Bit7 - Разрешение всех прерываний. Для разрешения прерываний этот бит должен быть установлен (=1). Разрешение конкретного прерывания выполняется регистрами маски прерывания EIMSK и TIMSK. Если этот бит очищен (=0), то ни одно из прерываний не обрабатывается. Бит аппаратно очищается после возникновения прерывания и устанавливается (разрешая последующие прерывания) командой RETI. Bit 6 - Бит сохранения копии. Команды копирования бита BLD и BST используют этот бит как источник и приемник при операциях с битами. Командой BST бит регистра общего назначения копируется в бит Т, командой BLD бит Т копируется в бит регистра общего назначения. Bit 5 - Флаг полупереноса. Флаг полупереноса указывает на перенос между тетрадами при выполнении ряда арифметических операций. Более подробная информация приведена в описании системы команд. Bit 4 - Бит знака. Бит S имеет значение результата операции Исключающее ИЛИ(N+V) над флагами отрицательного значения (N) и дополнения до двух флага переполнения (V). Более подробная информация приведена в описании системы команд. Bit 3 - Флаг, переполнения. Этот бит поддерживает арифметику дополнения до двух. Более подробная информация приведена в описании системы команд. Bit 2 - Флаг отрицательного значения. Этот флаг указывает на отрицательный результат ряда арифметических и логических операций. Более подробная информация приведена в описании системы команд. Bit 1 - Флаг нулевого значения. Этот флаг указывает на нулевой результат ряда арифметических и логических операций. Более подробная информация приведена в описании системы команд. Bit 0 - Флаг переноса. Этот флаг указывает на перенос при арифметических и логических операциях. Более подробная информация приведена в описании системы команд.

Указатель стека - SP. Микроконтроллеры AVR оснащены 16-разрядным указателем стека, размещенным в двух регистрах ввода-вывода. Поскольку микроконтроллеры ATmega103 поддерживают объем ОЗУ до 64 Кбайт, то используются все 16 разрядов указателя стека (Рисунок 5). Рисунок 5 – Указатель стека

Указатель стека указывает на область в ОЗУ данных, в которой размещается стек подпрограмм и прерываний. Начальный адрес указателя должен задаваться программно перед вызовом подпрограмм и разрешением прерываний. Начальное значение должно быть больше $60. Указатель стека декрементируется на единицу при каждом занесении командой PUSH данных в стек, и на две единицы при занесении в стек адреса при вызове подпрограммы или процедуры прерывания. Указатель стека инкрементируется на единицу при извлечении данных из стека командой POP, и на две единицы при извлечении адреса из стека при возврате из подпрограммы (RET) или возврате из процедуры прерывания (RETI).

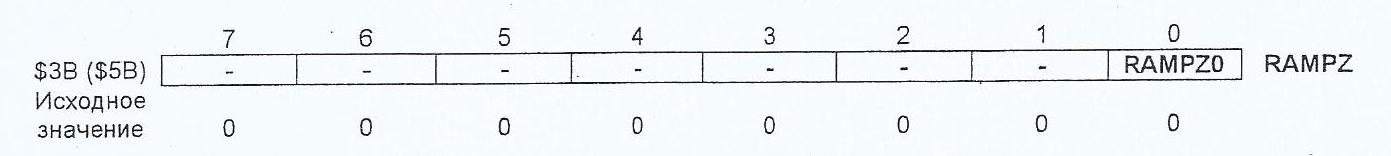

Регистр выбора страницы ОЗУ- RAMPZ. Регистр RAMPZ используется обычно для определения страницы ОЗУ данных, к которой возможно обращение посредством указателя Z. Поскольку микроконтроллеры ATmega103 не поддерживают ОЗУ объемом более 64 К, этот регистр используется только для выбора страницы в памяти программ при использовании команды ELPM. (Рисунок 6).

Рисунок 6 –Регистр выбора страницы

Имеются следующие варианты использования единственного значащего бита RAMPZ0: RAMPZ0 = 0: Команде ELPM доступна память программ с адресами от $0000 до $7FFF (младшие 64 Кбайт) RAMPZ0 = 1: Команде ELPM доступна память программ с адресами от $8000 до $FFFF (старшие 64 Кбайт). Отметим, что на команду LPM установки регистра RAMPZ не воздейсвуют. Микроконтроллер ATmega603 не содержит регистра RAMPZ и не имеет команды ELPM. Команда LPM способна перекрыть все пространства памяти программ микроконтроллера AТmega603. Регистр управления MCU – MCUCR.

Биты регистра управления MCU управляют выполнением основных функций MCU.(Рисунок 7)

Рисунок 7 – Регистр управления

Bit 7 - Разрешение внешнего ОЗУ. Установленный (=1) бит SRE разрешает обращение к внешней памяти данных и переводит работу выводов AD0-7 (Порт А), А8-15 (Порт С), WR и RD на выполнение альтернативной функции. Бит SRE также перенастраивает установки направлений в соответствующих, регистрах направления данных. Очистка бита SRE (=0) запрещает обращение к внешней памяти данных и восстанавливает нормальные установки направлений выводов и данных. Bit 6 - Режим состояния ожидания. При установленном (=1) бите SRW к циклу обращений к внешней памяти данных добавляется один цикл ожидания. При сброшенном (=0) бите SRW обращение к внешней памяти выполняется по трехцикловой схеме. Bit 5 - Разрешение режима Sleep. Установленный в 1 бит SE разрешает перевод MCU в режим sleep по команде SLEEP. Чтобы исключить перевод MCU в незапланированный режим sleep, рекомендуется устанавливать бит SE непосредственно перед выполнением команды SLEEP. Bits 4,3 - Биты выбора режима Sleep. Эти биты позволяют выбрать один из трех возможных режимов энергосбережения, как показано в таблице 2.

Таблица 2 – Выбор режима энергосбережения

Bits 2..0 - Зарезервированные биты

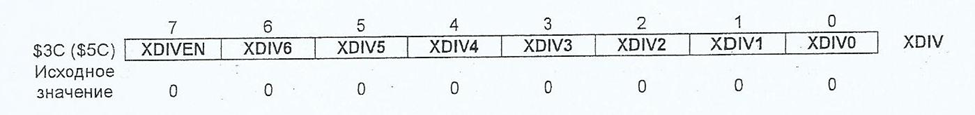

Регистр управления делением частоты кварцевого генератора – XDIV

Регистр XDIV используется для установки коэффициента деления частоты кварцевого генератора в диапазоне от 1 до 129. Эта возможность может быть использована для уменьшения энергопотребления (Рисунок 8).

Рисунок 8 – Регистр управления делением частоты кварцевого генератора Bit 7 - Разрешение деления частоты XTAL. При установленном (=1) бите XDIVEN тактовая частота CPU и всей периферии делится в соответствии с установленным битами XDIV6 – XDIV0 коэффициентом деления. Bit 6..0 - Биты выбора коэффициента деления. Эти биты устанавливают коэффициент деления тактовой частоты при установленном бите XDIVEN. Если десятичное значение этих семи битов обозначить через d, то результирующая тактовая частота CPU будет определяться по формуле:

FС LK = XTAL/(129- d)

Состояния этих битов можно изменить только при сброшенном бите XDIVEN. При установленном бите XDIVEN, записанное единовременно в биты XDIV6..XDIV0 значение будет определять коэффициент деления. При сбросе бита XDIVEN записанные в биты XDIV6..XDIV0 значения игнорируются. Поскольку делитель делит тактовую частоту поступающую на MCU, то и на периферийные устройства поступает тактовая частота с тем же коэффициентом деления. За регистрами ввода-вывода следуют 4000 адресов внутреннего ОЗУ данных. При использовании внешней памяти данных адресуются оставшиеся 60 Кбайт. Таким образом, при использовании микросхем памяти объемом 64К будут потеряны 4Кбайт. При обращении к внешней и внутренней памяти данных используются одни и те же команды, но во втором случае сигналы RD# и WR# не активизируются. Работа с внешней памятью данных разрешается установкой бита SRE регистра MCUCR. По сравнению с обращением к внутренней памяти, обращение к внешней требует дополнительно одного цикла на каждый байт. Это означает, что для выполнения команд LD, ST, LDS, STS, PUSH и POP требуется дополнительно машинный цикл. Если стек размещен во внешней памяти данных, то прерывания, вызов процедур и возвраты требуют по два дополнительных цикла, поскольку в стеке перемещается содержимое двухбайтного счетчика команд. Если при обмене с внешней памятью данных используется состояние ожидания, то на каждый байт необходимо еще два цикла. Поэтому командам пересылки данных необходимы два дополнительных цикла, тогда как при обработке прерываний, вызове процедур и возвратах требуется на четыре цикла больше, чем указано в описании системы команд. Практическое освоение системы команд и программирования на языке Ассемблер осуществляется в работах №1 и 2. Программирование ввода-вывода и подсистемы прерываний изучается в работах №3 - 7.

Введение Для обработки данных микроконтроллер ATmega103 использует группу команд, реализующих арифметические и логические операции, сдвиги и операции над отдельными битами. Арифметические операции являются операциями над 8-разрядными целыми числами. Для выполнения целочисленных операций над длинными словами служат команды сложения и вычитания с учетом флага переноса. Для выполнения операций над числами с плавающей точкой, реализации тригонометрических функций и т.д. служат библиотеки периода выполнения, входящие в состав интегрированной системы программирования «AVR Studio». Арифметические и логические команды приведены в табл.2.1. и табл.2.2.

Таблица 2.1 – Арифметические и логические команды

Операнды |

Описание | Операция |

Флаги | K-bo циклов | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ADD | Rd,Rr 0≤d≤31 0≤r≤31 | Сложить без переноса | Rd ←Rd + Rr | Z, C, N, V, H | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ADC | Rd,Rr 0≤d≤31 0≤r≤31 | Сложить с переносом | Rd ←Rd + Rr + С | Z, C, N, V, H | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ADIW | Rd,K d | {24,26,28,30} 0≤K≤63 | Сложить непосредственное, значение со словом | Rdh:Rdl ←Rdh:Rdl + К | Z, C, N, V | 2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SUB | Rd,Rr 0≤d≤31 0≤r≤31 | Вычесть без заема | Rd ← Rd - Rr | Z, C, N, V, H | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SUBI | Rd, К 16<d<31 0≤K≤255 | Вычесть непосредственное значение | Rd ← Rd - К | Z, C, N, V, H | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SBC | Rd, Rr 0≤d≤31 0≤r≤31 | Вычесть с заемом | Rd ←Rd - Rr-C | Z, C, N, V, H | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SBCI | Rd, К 16≤d≤31 0≤K≤255 | Вычесть непосредственное значение с заемом | Rd ←Rd - K-C | Z, C, N, V, H | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SBIW | Rd, К d | £{24,26,28,30} 0≤K≤63 | Вычесть непосредственное значение из слова | Rdh:Rdl← Rdh:Rdl - К | Z, C, N, V | 2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AND | Rd, Rr 0≤d≤31 0≤r≤31 | Выполнить логическое AND | Rd ←Rd • Rr | Z, N, V | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AND I | Rd, К 16≤d≤31 0≤K≤255 | Выполнить логическое AND | Rd ←Rd • К | Z, N, V | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| OR | Rd, Rr 0≤d≤31 0≤r≤31 | Выполнить логическое OR | Rd ←Rd v Rr | Z, N, V | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ORI | Rd, К 16≤d≤31 0≤К≤255 | Выполнить логическое OR с непосредственным значением | Rd ←Rd v К | Z, N, V | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| EOR | Rd, Rr 0≤d≤31 0 ≤r≤31 | Выполнить исключающее OR | Rd ←Rd © Rr | Z, N, V | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| СОМ | Rd 0≤d≤31 | Выполнить дополнение до единицы | Rd ←$FF - Rd | Z, C, N, V | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| NEG | Rd 0≤d≤31 | Выполнить дополнение до двух | Rd← $00 - Rd | Z, C, N, V, H | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SBR | Rd, К 16≤d≤31 0≤K≤255 | Установить биты в регистре | Rd ← Rd v К | Z, N, V | 1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| CBR | Rd, К 16≤d≤31 0≤K≤255 | Очистит

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2019-11-02; просмотров: 153; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.119 (4.488 с.) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||