Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Работа №4 цифровые системы на базе микроконтроллера atmega103: реализация и обслуживание подсистемы прерываний

Цель работы: изучение организации прерываний в микроконтроллере ATmega103 и обслуживания подсистемы прерываний. Введение Микроконтроллеры ATmega103 используют 23 источника прерывания. Эти прерывания и механизм сброса располагают отдельными векторами в пространстве памяти программ. Каждому прерыванию присвоен свой бит разрешения, который должен быть установлен совместно с битом I регистра статуса SREG. Младшие адреса пространства памяти программ автоматически определяются как векторы сброса и прерываний. Полный перечень векторов представлен в Таблице 4.1. Перечень отражает также уровень приоритета для каждого прерывания. Прерывания с младшими адресами имеют больший уровень приоритета: RESET имеет наивысший уровень приоритета, следующим является запрос внешнего прерывания INT0 -и т.д.

Таблица 4.1 – Векторы сброса и прерываний

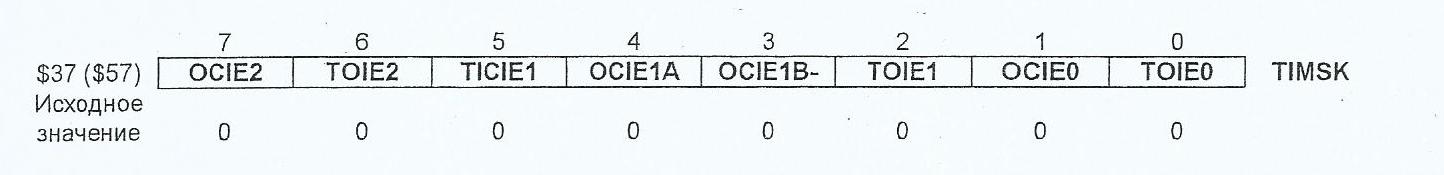

Микроконтроллеры ATmega103 содержат два специальных 8-разрядных регистра масок прерываний: регистр масок внешних прерываний EIMSK (External Interrupt Mask) и регистр масок прерываний таймеров/счетчиков TIMSK (Timer/Counter Interrupt Mask). Кроме того, в регистрах управления блоками ввода-вывода могут существовать и другие биты разрешения и биты масок.

При возникновении прерывания бит I разрешения всех прерываний (в регистре SREG) очищается и все прерывания запрещаются. Процедура прерывания может установить бит I, чтобы разрешить вложенные прерывания. Выход из процедуры обработки прерывания происходит по команде RETI которая устанавливает бит I (=1). Когда в счетчик команд загружен вектор процедуры обработки прерывания, соответствующий флаг, вызвавший прерывание, аппаратно очищается. Некоторые флаги прерываний можно очистить программно. Если условия прерывания возникли, когда соответствующий бит разрешения очищен, флаг этого прерывания будет установлен и сохранен в таком состоянии, пока прерывание не будет разрешено, или флаг не будет очищен программно. Если условия прерываний возникли, когда очищен бит разрешения всех прерываний, флаги прерываний будут установлены и сохранены в таком состоянии, пока все прерывания не будут разрешены и обработаны в порядке приоритетов. Прерывания по уровню сигнала флага не имеют и условия прерывания имеют место, пока активен внешний сигнал.

Рисунок 4.1 – Регистр масок внешних прерываний – EIMSK

Bits 7..4 - Разрешение внешних прерываний INT7.. INT4. При установленных битах INT7-INT4 и установленном бите I регистра статуса (SREG) разрешаются прерывания по соответствующим выводам сигналов внешних прерываний. Бит управления опознаванием прерывания регистра управления внешними прерываниями EICR (External Interrupt Control Register) определяет условия возникновения запроса: по нарастающему/спадающему фронту сигнала или по логическому уровню. Активность сигнала по любому из этих выводов вызовет запрос прерывания, даже если вывод назначен как выход. Это обеспечивает возможность организации программного прерывания. Bits 3..0 - Разрешение внешних прерываний INT3.. INT0. При установленных битах INT3-INT0 и установленном бите I регистра статуса (SREG) разрешаются прерывания по соответствующим входам сигналов внешних прерываний. Внешние прерывания всегда вызываются низким уровнем сигнала. Активность сигнала по любому из этих выводов вызовет запрос прерывания, даже если вывод назначен как выход. Это обеспечивает возможность организации программного прерывания. Запрос прерывания по логическому уровню, если он разрешен, будет существовать до тех пор, пока на входе будет низкий уровень сигнала.

Рисунок 4.2 – Регистр флагов внешних прерываний – EIFR

Bits 7..4 - Флаги внешних прерываний INTF7 - INTF4. В случае поступления запроса на прерывание на какой-либо из выводов INT7 - INT4 устанавливается (=1) соответствующий флаг прерывания INTF7 - INTF4. Если бит I регистра SREG и соответствующий бит разрешения (INT7 - INT4) регистра EIMSK установлены, то выполняется переход по вектору прерывания. При возврате из процедуры прерывания флаг очищается. Кроме того, флаг можно очистить, записав в него логическую 1.

Обратите внимание, что программно установить флаг внешнего прерывания, записав в него «1», невозможно! Bits 3..0 - Зарезервированные биты.

Рисунок 4.3 – Регистр управления внешними прерываниями – EICR

Bits7..0 - ISCX1, ISCX0: Биты управления опознаванием внешних прерываний INT7- INT4. Запросы внешних прерываниях на выводах INT7 - INT4 являются активными, если установлен флаг I регистра SREG и установлена соответствующая маска в регистре EIMSK. Запрос прерывания по логическому уровню или фронтам определяется в соответствии со следующей таблицей:

Таблица 4.2 – Управление опознаванием прерывания

Примечание: X может быть равен 7, 6, 5 или 4 При изменении битов ISCx1/ISCx0 прерывание должно быть запрещено очисткой бита разрешения в регистре GIMSK. В ином случае может произойти прерывание в момент изменения бита.

Входы прерываний INTx периодически опрашиваются на предмет наличия запроса. Если внешний запрос прерывания фиксируется по фронту, то для гарантированного срабатывания длительность импульса должна быть больше, чем период синхрочастоты процессора. Заметим, что частота процессора может быть меньше частоты XTAL из-за возможного наличия делителя. Запрос прерывания по логическому уровню должен продолжаться, пока выполняется текущая инструкция и он будет зафиксирован. Запрос прерывания по логическому уровню, если он разрешен, будет генерировать запрос прерывания до тех пор, пока на входе удерживается низкий уровень.

Рисунок 4.3 – Регистр масок прерывания по таймерам/счетчикам – TIMSK Bit 7 - ОС IЕ2: Разрешение прерывания по совпадению Таймера 2. При установленном бите OCIE2 и установленном бите I регистра статуса разрешается прерывание по совпадению содержимого регистра сравнения и состояния Таймера 2. Соответствующее прерывание (с вектором $0012) имеет место, если произойдет совпадение при сравнении содержимого регистра сравнения и состояния таймера/счетчика2. В регистре флагов прерывания TIFR устанавливается флаг OCF2. Bit 6 - TOIE2: - Разрешение прерывания по переполнению Таймера 2. При установленном бите TOIE2 и установленном бите I регистра статуса разрешается прерывание по переполнению Таймера 2. Соответствующее прерывание (с вектором $0014) выполняется если произойдет переполнение Таймера 2. В регистре флагов TIFR устанавливается флаг TOV2 переполнения Таймера 2.

Bit 5 - TICIE1: - Разрешение прерывания по захвату Таймера 1. При установленном бите TICIE1 и установленном бите I регистра статуса разрешается прерывание по захвату Таймера 1. Соответствующее прерывание (с вектором $0016) выполняется, если произошел захват по выводу 29, PD4(IC1). В регистре флагов TIFR устанавливается флаг ICF1 захвата Таймера 1. Bit 4 - OCIE1 A: - Разрешение прерывания по совпадению регистра А с Таймером 1. При установленном бите OCIE1A и установленном бите I регистра статуса разрешается прерывание по совпадению регистра А с состоянием Таймера 1. Соответствующее прерывание (с вектором $0018) выполняется, если имеется совпадение содержимого регистра А с состоянием Таймера 1. В регистре флагов TIFR устанавливается флаг OCF1A совпадения регистра А с Таймером 1. Bit 3 - OCIE1 B: - Разрешение прерывания по совпадению регистра В с Таймером 1. При установленном бите OCIE1B и установленном бите 1 регистра статуса разрешается прерывание по совпадению регистра В с состоянием Таймера 1. Соответствующее прерывание (с вектором $001 А) выполняется, если имеется совпадение содержимого регистра В с состоянием Таймера 1. В регистре флагов TIFR устанавливается флаг OCF1B совпадения регистра В с Таймером 1. Bit 2 - TOIE1: - Разрешение прерывания по переполнению Таймера 1. При установленном бите TOIE1 и установленном бите I регистра статуса разрешается прерывание по переполнению Таймера 1. Соответствующее прерывание (с вектором $001С) выполняется, если произойдет переполнение Таймера 1. В регистре флагов TIFR устанавливается флаг TOV1 переполнения Таймера 1. Bit 1 – OCIE 0: - Разрешение прерывания no совпадению Таймера 0. При установленном бите OCIE0 и установленном бите I регистра статуса разрешается прерывание по совпадению содержимого регистра сравнения и состояния Таймера 0. Соответствующее прерывание (с вектором $001Е) выполняется, если произойдет совпадение при сравнении содержимого регистра сравнения и состояния Таймера 0. В регистре флагов прерывания TIFR устанавливается флаг OCF0 совпадения Таймера 0. Bit 0 – TOIE 0: - Разрешение прерывания по переполнению Таймера 0. При установленном бите TOIE0 и установленном бите I регистра статуса разрешается прерывание по переполнению Таймера 0. Соответствующее прерывание (с вектором $0020) выполняется, если произойдет переполнение Таймера 0. В регистре флагов TIFR устанавливается флаг TOV0 переполнения Таймера 0.

Рисунок 4.3 – Регистр флагов прерываний по таймерам/счетчикам –TIFR

Bit 7 - OCF 2: - Флаг 2 совпадения Таймера 2 и данных OCR 2. Бит OCF2 устанавливается при совпадении состояния Таймера 2 и содержимого регистра OCR2. Бит OCF2 аппаратно очищается при обработке соответствующего вектора прерывания. Возможна очистка бита записью во флаг логической 1. При установленных битах I в регистре SREG, OCIE2 и OCF2 выполняется прерывание по совпадению Таймера 2. Bit 6 - TOV 2: - Флаг переполнения Таймера 2. Бит TOV2 устанавливается при переполнении Таймера 2. Он аппаратно очищается при обработке соответствующего вектора прерывания. Возможна очистка бита записью во флаг логической 1. При установленном бите I в регистре SREG, установленных битах OCIE2 и TOV2 выполняется прерывание по переполнению Таймера 2. В режиме PWM этот бит устанавливается, при переходе через $00. Bit 5 - ICF 1: - Флаг 1 захвата входа. Бит ICF1 устанавливается в случае захвата входа и показывает, что значение Таймера 1 переслано во входной регистр захвата ICR1. Бит очищается аппаратно при обработке соответствующего вектора прерывания. Возможна очистка бита записью во флаг логической 1. Bit 4 - OCF 1 A: - Флаг 1А совпадения выхода. Бит OCF1A устанавливается при совпадении состояния Таймера 1 и содержимого регистра OCR1A. Бит OCF1A аппаратно очищается при обработке соответствующего вектора прерывания. Возможна очистка бита записью во флаг, логической 1. При установленном бите I в регистре SREG, установленных битах OCIE1A и OCF1A выполняется прерывание по совпадению выхода Таймера счетчика1. Bit 3 - OCF 1 B: - Флаг 1В совпадения выхода. Бит OCF1B устанавливается при совпадении состояния Таймера 1 и содержимого регистра OCR1B. Бит OCF1B аппаратно очищается при обработке соответствующего вектора прерывания. Возможна очистка бита записью во флаг логической 1. При установленном бите I в регистре SREG, установленных битах OCIE1B и OCF1B выполняется прерывание по совпадению выхода Таймера 1. Bit 2 - TOV 1: - Флаг переполнения Таймера 1. Бит ТОV1 устанавливается при переполнении Таймера 1. Он аппаратно очищается при обработке соответствующего вектора прерывания. Возможна очистка бита записью во флаг логической 1. При установленном бите I в регистре SREG, установленных битах TOIE1 и TOV1 выполняется прерывание по переполнению Таймера 1. Bit 1 – OCF 0: - Флаг 0 совпадения выхода. Бит OCF0 устанавливается при совпадении состояния Таймера 0 и содержимого регистра OCR0. Бит OCF0 аппаратно очищается при обработке соответствующего вектора прерывания. Возможна очистка бита записью во флаг логической 1. При установленном бите I в регистре SREG, установленных битах OCIE0 и OCF0 выполняется прерывание по совпадению выхода Таймера 1. Bit 0 – TOV 0: - Флаг переполнения Таймера 0. Бит TOV0 устанавливается при переполнении Таймера 0. Он аппаратно очищается при обработке соответствующего вектора прерывания. Возможна очистка бита записью во флаг логической 1. При установленном бите I в регистре SREG, установленных битах TOIE0 и TOV0 выполняется прерывание по переполнению Таймера 0.

Обратите внимание, что программно установить флаг таймера-счетчика, записав в него «1», невозможно! ВЫПОЛНЕНИЕ ОСНОВНОГО ЗАДАНИЯ 1. Изучить функциональные подсистемы прерываний микроконтроллера ATmega103. 2. Запустить на инструментальном компьютере интегрированную систему программирования «AVR Studio». Создать новый проект, в нем новый файл исходного текста и сохранить его с именем demo4.asm. В файл поместить текст программы: ;************************************************* ;* ОБЯЗАТЕЛЬНОЕ ЗАДАНИЕ ; * лабораторной работы N4

;* ;******** ************************************************************************** . Include "ml03DEF.INC"; ; ************** ************** Контакты ****************************************** .EQU STACK =$80 .EQU EIMask=$01 .EQU TIMask=$01 .EQU ClockSel=3; (1<<CS00) + (1<<CS01) + (0<<CS02)

;********** **** * * * * * * * * * * * * * * * * Регистры * *** * ******************** * * .Def Zero=R3; .Def Acc=Rl6; .Def Bcc=R17; .Def Ccc=R18; .Def Dcc=R19;

.** * * * * **** * * *** * ********** Таблица прерываний ******************************* .ORG $0 jmp Start .ORG $2; вектор Int0 jmp Intr0 .ORG $4; вектор Int1 reti .ORG $6; вектор Int2 reti .ORG $8; вектор Int3 reti .ORG $A; вектор Int4 reti .ORG $C; вектор Int5 reti .ORG $E; вектор Int6 reti .ORG $10; вектор Int7 reti .ORG $12; вектор Timer2 Compare reti .ORG $14; вектор Timer2 Overflow reti .ORG $16; вектор Timer1 Capture reti .ORG $18; вектор Timer1 CompareA reti .ORG $1A; вектор Timer1 Compares reti .ORG $1C; вектор Timer1 Overflow reti .ORG $1E; вектор Timer0 Compare reti .ORG $20; вектор Timer0 Overflow jmp OverT0 .ORG $22; вектор SPI reti .ORG $24;. вектор приемника UART jmp RxUART .ORG $26; вектор “буфер передатчика пуст” UART reti .ORG $28; вектор передатчика UART reti .ORG $2A; вектор АД преобразователя reti .ORG $2C; вектор EEPROM reti .ORG $2E; вектор аналогового компаратора reti .ORG $30

;****************** ******Основная программа*********************************** Start: ldi Acc, high (Stack); инициализация стека через регистр Acc out SPH, Acc ldi Acc, low (Stack) out SPL, Acc

ldi Acc,$F0; установка направления порта D out DDRD, Acc; ldi Acc,$01; подключение внутренних подтягивающих резисторов out PortD, Acc;

ldi Acc,EIMask; разрешение прерывания INTO out EIMask, Acc; ldi Acc,TIMask; разрешение прерывания по переполнению Таймера0 out TIMSK, Acc; ldi Acc,ClockSel; out TCCR0, Acc; запуск таймера0 с предделителем clr Zero; очистка “нулевого” регистра ldi Acc, 25; out UBRR, Acc; ldi Acc, $80; out UCR, Acc; mov Acc, Zero; очистка регистра Acc ldi r30, $1E; l(Z) очистка регистров ldi r31, 0; h(Z) clearR: st -Z, r31 cpse r30, r31 rjmp clearR

sei; разрешение всех прерываний

;--------------------------------------- ------------------------------------------------------------------------------- Loop: sec adc Acc, Zero; инкремент трехбайтного числа adc Bcc, Zero; adc Ccc, Zero; cpi Ccc, 100; если старший байт равен 100, то brne Loop; rcall Stop Beep; остановить звук rjmp Loop;

;************** ********Процедура остановки таймера**************************** StopBeep: out TCCR0, Zero; отключаем маркер ret

;****** *******Обработка прерывания Таймера0**************************** OverT0: push Acc; сохранение состояния контроллера in Acc,SREG; push Acc; com Dcc; инверсия всех битов andi Dcc,$80; оставляем только бит соотв. пьезоизлучателю ori Dcc,1; out PORTD, Dcc; вывод в порт D pop Acc; восстановление состояния контроллера out SREG, Acc; pop Acc; reti

;************** *****Прием по RS232**************************************** RxUART: rcall StopBeep; Вызов процедуры остановки Таймера 0 reti ;************** ******Обработка прерывания Intr0*************************** Intr0: rcall StopBeep; Вызов процедуры остановки Таймера 0 reti .Exit

Программа demo4.asm дает пример использования прерываний в рабочей программе. Основными действиями при этом являются формирование таблицы переходов, определение начального адреса стека, создание процедур обработки прерываний. Программа Demo4.asm обеспечивает непрерывный вывод прямоугольных импульсов фиксированной частоты на пьезодинамик макета. Любое прерывание прекращает генерацию. Программа начинается с объявления констант с помощью директивы EQU и переобозначения регистра R16 с помощью директивы DEF, как и в предыдущей работе. Далее в качестве иллюстрации приведена вся таблица прерываний с указанием адресов всех доступных векторов прерываний. В данном примере разрешены прерывания по следующим событиям: - сброс микроконтроллера - внешнее прерывание №0 - переполнение таймера 0 - прием байта данных по последовательному интерфейсу UART Использование указанных периферийных устройств будет рассмотрено в следующих работах. Программа функционирует следующим образом. После инициализации, т.е. после указания вершины стека и инициализации периферийных устройств, таких как таймер0 и UART, начинается выполнение основного цикла, который продолжается, пока включено питание микроконтроллера. Механизм прерываний обеспечивает реакцию на асинхронные события, т.е. он приостанавливает выполнение основной программы, сохраняя адрес следующей исполняемой команды в стеке, и присваивает PC (счетчику команд) адрес метки прерывания. Тем самым начинает выполняться процедура обработки прерывания. По команде reti в конце процедуры прерывания, происходит восстановление из стека адреса выполняемой на момент прерывания команды в основной программе и выполнение основной программы продолжается. В случае, если в процедуре обработки прерывания выполняются арифметические операции или изменяется содержимое регистров общего назначения, необходимо сохранить состояние контроллера перед командами обработчика. Текущее состояние - это совокупность флагов и регистров общего назначения, т.е. регистр SREG и регистры R0-R31. Из регистров сохраняются только те, значения которых будет изменено в прерывании. Сохранение регистров осуществляется командой push, восстановление - командой pop. 1. Выполнить трансляцию программы и при пошаговой отладке после команды разрешения прерываний sei с помощью команды View | New IO view окно ресурсов контроллера и установить бит запроса от порта UART, наблюдать за последовательностью команд вызова процедуры и изменениями состояния стека. 2. Подключить лабораторный макет к персональному компьютер}', включить его питание, выполнить трансляцию программы и загрузить ее исполняемый код в контроллер. После загрузки слышен звуковой сигнал из пьезодинамика. Нажатие любой клавиши в первом ряду клавиатуры инициирует внешнее прерывание INT0, процедура которого выключает Таймер0, что прекращает генерацию импульсов звуковой частоты. Если нажатия клавиши нет в течении нескольких минут, звуковой сигнал прекращается автоматически. Задания 1. Составить различные процедуры обслуживания прерываний, выполняемых при поступлении внешних сигналов INT0, INT1, а также переполнении счетчиков-таймеров: - чтение данных из регистра заданного порта, - зажигание светодиода, - вывод заданного символа на семисегментный индикатор, - формирование звукового сигнала. 2. Запустить программу на выполнение. Реализовать запросы INT0, INT1 и таймеров, обеспечить вызов и выполнение соответствующих процедур обслуживания, контролируя работу программы с помощью интегрированной системы программирования и лабораторного макета.

Вопросы для защиты работы: 1. Прерывания микропроцессора ATMega 103. 2. зажигание светодиода подключенного к порту ATMega 103. 3. вывод заданного символа на семисегментный индикатор ATMega 103. 4. формирование звукового сигнала на динамике подключенном к к порту ATMega 103.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2019-11-02; просмотров: 112; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.134.104.173 (0.111 с.) |