Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Выбор и обоснование принципиальной схемы модуля сжатия речевых сигналовСодержание книги

Поиск на нашем сайте

В качестве устройства обработки речевого сигнала используется микропроцессор ADSP 2181, т.к. его применение позволит решить все задачи по обработке речевого сигнала, т.е. его сжатие, синтез, выработка сигналов управления ОЗУ. ADSP 2181 представляет собой однокристальный микрокомпьютер, оптимизированный для цифровой обработки сигналов, а также других высокоскоростных вычислительных операций. Подробное описание сигнального процессора в /8,9/. Процессор ADSP 2181 - один из самых мощных в этой серии, имеет 80Кбайт быстродействующего ОЗУ на кристалле, таймер, а также несколько последовательных и параллельных портов. Процессор состоит из двух частей: процессорного блока и блока периферийных устройств. Процессорный блок - единый для всей серии ADSP 21XX - содержит 3 вычислительных устройства: АЛУ, умножитель-сумматор и устройство сдвига; устройство управления и 2 генератора адреса /10/. Каждое из вычислительных устройств имеет свой набор входных регистров и один или два аккумулятора для результатов. Взаимодействие всех процессорных устройств между собой осуществляется с помощью 5-ти шин. Названия шин, разрядность и обозначения приведены в табл.4.1.

Таблица 4.1

Периферийные устройства - два банка быстродействующей памяти по 16К слов каждый, 2 синхронных последовательных порта (SPORT0 и SPORT1), таймер, порты прямого доступа к памяти (IDMA и BDMA), контроллер прерываний, логика управления внешней шиной. Внутренние шины процессора коммутируются в одну 14-ти разрядную внешнюю шину адреса и одну 24-х разрядную шину данных. Тип памяти, к которой обращается процессор по внешней шине, определяется сигналами выбора памяти, типы памяти приведены в табл.4.2.

Таблица 4.2

Внешн. шина адреса Внешн. шина данных Таймер Контроллер прерываний IDMA Контроллер PMA DMA PMD DMD Флаги Power Down Контроллер BDMA Контроллер Внешн. шина адреса Внешн. шина данных

Таймер Контроллер прерываний IDMA Контроллер PMA DMA PMD DMD Флаги Power Down Контроллер BDMA Контроллер

Архитектура процессора ADSP2181 имеет высокую степень параллелеризма, отвечающую требованиям цифровой обработки сигналов. За один командный цикл процессор может выполнить следующие действия: 20)cгенерировать адрес новой команды; 21)осуществить выборку и дешифрацию следующей команды; 22)выполнить одно или два обращения к памяти; 23)обновить один или два указателя адреса данных; 24)выполнить вычисления; 25)передавать данные через последовательные порты; 26)передавать данные по DMA портам. Базовая архитектура процессора приведена на рис 4.1.

Вычислительные устройства непосредственно работают с 16 - битными данными и имеют аппаратную поддержку для работы с числами повышенной точности. АЛУ выполняет стандартный набор арифметических и логических операций, а также примитивы деления. МАС выполняет умножение за один цикл, а также операции умножения/вычитания. Устройство циклического сдвига производит арифметические и логические операции. В нем реализованы операции над числами в разных форматах, в том числе и надо числами с плавающей точкой, занимающих более одного слова. Вычислительные устройства организованны "бок о бок", а не последовательно, что позволяет результату работы любого устройства быть операндами любого другого устройства в следующем цикле. Шина внутренних результатов (R) прямо соединяет вычислительные устройства с этой целью. Все три вычислительных устройства содержат входные и выходные регистры, которые доступны через внутреннюю шину (DMD). Вычислительные устройства обычно берут операнды из входных регистров и помещают результат в выходной регистр. Эти регистры обеспечивают буферизацию между вычислительными устройствами и памятью. Шина внутренних результатов позволяет использовать результат предыдущего вычисления, используя непосредственно как операнд другой операции. Это исключает задержки в случае выполнения серий различных операций. Два выделенных генератора адресов данных DAG и многофункциональный счетчик команд обеспечивают эффективное использование вычислительных устройств. Генераторы адресов данных обеспечивают адреса памяти данных, когда данные пересылаются из выходных или во входные регистры. Каждый из двух генераторов запоминает до 4 адресных указателей. Когда указатель используется для косвенной адресации, он может автоматически модифицироваться значением в заданном регистре после исполнения инструкции. Имея 2 генератора адресов, процессор может генерировать 2 адреса за один цикл, что обеспечивает исполнение двухадресных инструкций.

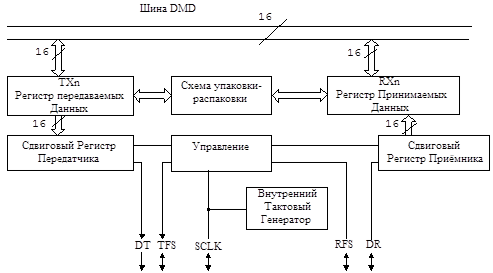

Программированный интервальный таймер, обеспечивающий периодическую генерацию прерываний.8-битный масштаб позволяет ему декрементировать содержимое 16-битного регистра-счетчика в диапазоне от каждого цикла до 256-го цикла процессора. Прерывание генерируется, когда регистр-счетчик обнуляется. Регистр-счетчик автоматически загружается из 16-битного регистра интервала и отсчет времени немедленно возобновляется. Данный процессор имеет два двунаправленных последовательных порта (SPORT) с двойной буферизацией. Эти порты используют синхронную передачу данных и используют кадровые сигналы, чтобы контролировать поток данных. Каждый порт может тактироваться от внутреннего таймера или от внешней частоты. Сигналы кадровой синхронизации могут меняться от 3 бит до 16. ADSP подключается к внешними устройствам через SPORT, рассмотрим его подробно. Последовательные порты. Для сопряжения с аппаратными средствами существует синхронные последовательные порты, или SPORT. SPORT поддерживает много последовательных протоколов обмена данными и могут обеспечить прямое соединение процессоров в многопроцессорной системе. В нашем случае для соединения ADSP с системной шиной и устройством управления. Каждый SPORT имеет пять интерфейсных линий: 27)SCLK Синхроимпульсы; 28)RFS Синхроимпульсы; 29)TFS Синхронизация приема кадра; 30)DT Передача данных; 31)DR Прием данных. SPORT получает данные через вход DR и посылает данные через вход DT. Для полнодуплексной работы он может одновременно посылать и принимать данные. Биты данных синхронизируются с синхроимпульсами SCLK. Линия SCLK является выходом, если процессор генерирует синхроимпульсы, и входом, если синхроимпульсы приходят извне. Сигналы синхронизации кадров RFS и TFS используются для индикации начала передачи слова или потока слов. Рис 4.2 показывает упрощенную блок-схему одного SPORT. Данные, подлежащие передаче, записываются из внутреннего регистра процессора в регистр RХ находящийся в SPORT, по шине DMD. Эти данные могут быть аппаратно упакованы, затем автоматически передаются в регистр сдвиговой передачи, биты из которого последовательно сдвигаются так, что они попадают на сигнал DT (синхронно с сигналом SCLK), начиная с младших бит. Приемная секция SPORT принимает данные с DR, синхронно с сигналом SCLK. Когда получено целое слово, данные могут быть автоматически распакованы, затем оно автоматически копируется в регистр RX, находящийся в SPORT, где эти данные доступны для процессора.

Блок схема последовательного порта

Рис.4.2

Рассмотрим возможности SPORT. Каждый SPORT имеет независимые секции приема и передачи (является двунаправленным). Каждая секция SPORT (и приемная, и передающая) имеет регистр данных для передачи слов данных в процессор, из процессора и регистр для сдвига посылаемых данных, получаемых данных (то есть имеет двойную буферизацию, что обеспечивает дополнительное время для обработки данных процессором).

Каждый SPORT может использовать внешние синхроимпульсы c частотой от 0 Гц до 12.5 МГц или генерировать свои в широком диапазоне частот (до 1/2 частоты процессора). Каждый SPORT поддерживает длины последовательного слова от 3 до 16 бит. Каждая секция SPORT (и приемная, и передающая) может работать: 32)как с, так и без сигналов синхронизации кадра для прима/передачи каждого слова; 33)с внутренними или внешними кадровыми сигналами; 34)с активным высоким или активным низким кадровыми сигналами; 35)с нормальным или альтернативным режимом кадровой синхронизации. Каждый SPORT поддерживает аппаратное сжатие по А-закону или в соответствии с рекомендацией CCITT G.711. Автобуферизация с одним циклом задержки. С использованием DAG, SPORT может автоматически принять и/или передать целый кольцевой буфер, с затратой лишь одного цикла на переданное/полненное слово данных. Передачи данных между SPORT и кольцевым буфером происходят автоматически в этом режиме и не требуют дополнительного программирования. Прерывания: каждая секция SPORT (и приемная, и передающая) генерирует прерывание по завершению передачи/приема слова данных или целого буфера данных, если, используется режим автобуферизации. Многоканальные возможности: SPORTO может получать и передавать данные выборочно по каналам последовательного потока бит, мультиплексированного на 24 или 32 канала. В данном случае мы получаем возможность одновременного обслуживания до 24 или 32 каналов. Альтернативная конфигурация: SPORT1 может быть сконфигурирован как два внешних запроса на прерывание, IRQ0 и IRQ1, а также как два сигнала Flag In и Flag Out, вместо последовательного порта. Запись в регистр TX переводит SPORT в состояние готовности к передаче; сигнал TFS инициализирует передачу данных. Как только передача началась, каждое значение, записанное в регистр TX, передается во внутренний регистр передачи сдвигом, и биты данных последовательно посылаются, начиная с самого младшего. Каждый бит посылается по фронту сигнала SCLK. Как только младший бит слова послан, SPORT генерирует прерывание передачи. Регистр ТХ снова доступен для записи данных, хотя передача предыдущего слова только началась. В приемной секции, биты собираются по мере их прихода. Как только полное слово данных принято, SPORT записывает его в регистр RX и генерирует прерывание приема данных. Управление конфигурацией SPORT осуществляется установкой битов в конфигурационных регистрах. Конфигурационные регистры SPORT0 размещаются по адресам 0x3FF3-3FFA. Каждый SPORТ имеет регистры приема и передачи. Эти регистры недоступны по адресу памяти, зато они имеют ассемблерные мнемоники. Регистры для передачи данных называются TX0 и RX0 для SPORT0. SPORT0 должен быть сконфигурирован под ИКМ-32 с потоком 2048 Мбит/с.

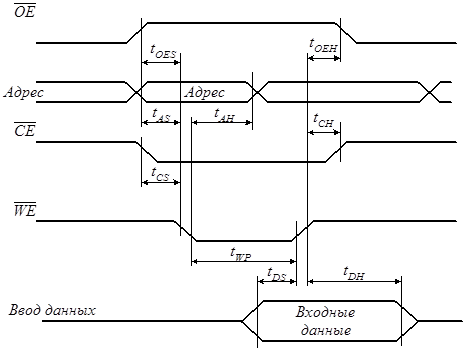

Применение в качестве ОЗУ данных ИС HY584000 фирмы Samsung позволяет обеспечить многократное считывание информации без ее разрушения. Особенностью данной микросхемы является перезапись информации при подаче на вход элемента напряжения низкого уровня. Это более удобно, так как обрыв вывода не создает на входе ИС напряжение активного уровня, что повышает надежность его работы. Данная ИС позволяет производить чтение - запись информации по одним и тем же выводам, что важно с точки зрения упрощения ИС. Выход ИС имеет три выходных состояния, т.е. информация подключается к выходным выводам только при выборе ИС. Приведем временные диаграммы управляющих сигналов, соответствующих процессу чтения из памяти (рис.4.3).

Диаграммы управляющих сигналов чтения из памяти Рис.4.3

В табл.4.3 приведены некоторые параметры управляющих сигналов чтения из памяти

Таблица 4.3 Параметры сигналов чтения из памяти

Приведем временные диаграммы управляющих сигналов, соответствующих процессу записи в память (рис.4.4).

|

||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2020-03-02; просмотров: 149; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.219.112.243 (0.013 с.) |

,

,