Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

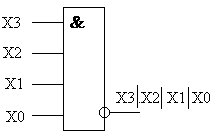

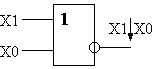

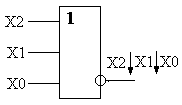

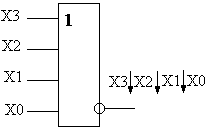

Таблица 2.3.1 Графические эквиваленты ФАЛ типовых элементовСодержание книги

Поиск на нашем сайте

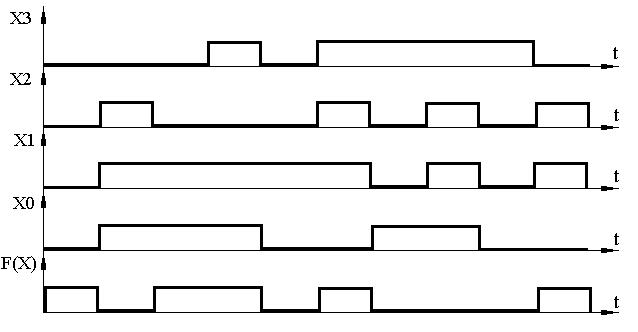

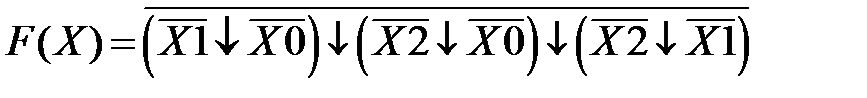

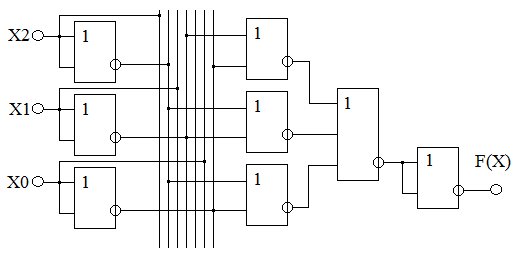

Для синтеза схемы логического устройства элементы, реализующие логические операции, необходимо располагать от входа к выходу согласно их месту в заданной ФАЛ. Пример 2.3.10. Синтезировать схему для ФАЛ

В приведенной схеме для получения сигналов, инверсных заданным, на входе устройства дополнительно используются логические элементы 2ИЛИ-НЕ, реализующие, согласно теореме

ПРИМЕР СИНТЕЗА КОМБИНАЦИОННОГО ЛОГИЧЕСКОГО УСТРОЙСТВА В БАЗИСЕ 3И-НЕ Рассмотрим выполнение задания со следующими параметрами: вар. 1 (табл. 2.6), вар. 3 (табл. 2.7), вар. 6 (табл. 2.8). Согласно заданию из таблиц 2.6, 2.7 и 2.8 выбираем: · последовательность конституент единицы: 0, 3, 4, 6, 11, 12, 13, 14; · базис логических элементов: 3И-НЕ; · последовательность проверочных кодов: 0, 7, 3, 11, 2, 14, 9, 15, 8, 6. 1. По заданным конституентам единицы составим таблицу истинности. Так как максимальная из заданных конституент равна 14, то для отображения входного кода проектируемого устройства достаточно четырех входных переменных (четырехразрядного входного кода). Т а б л и ц а 2.4.1. Таблица истинности работы устройства

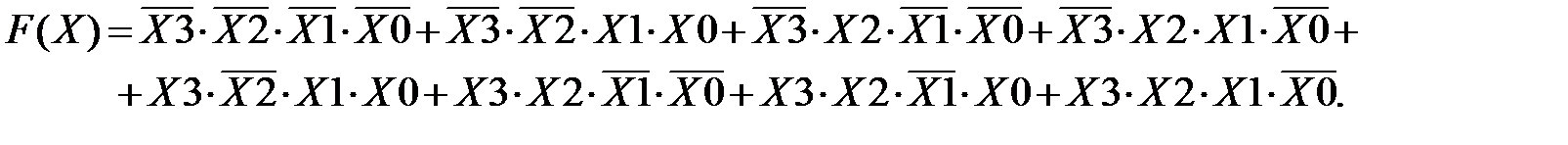

2. Используя составленную таблицу истинности, запишем СДНФ и CКНФ синтезируемого устройства. СДНФ:

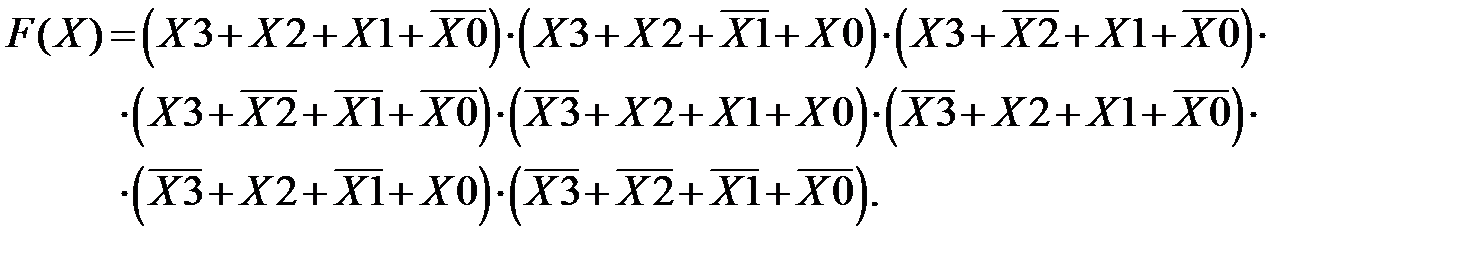

СКНФ:

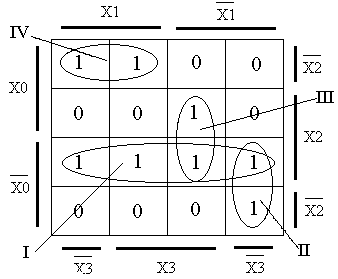

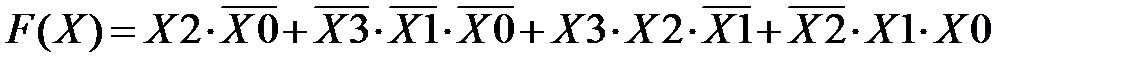

3. Минимальную дизъюнктивную форму ФАЛ получим с использованием карты Вейча. На карте Вейча (см. рис. 2.4.1) можно выделить 4 области, охватывающие все единичные значения функции. Первая область состоит из четырех элементов, описываемая произведением неизменных переменных Вторая область – из двух элементов, описываемая произведением неизменных переменных

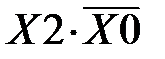

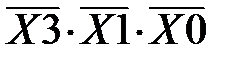

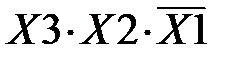

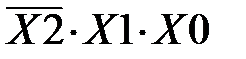

Третья область – из двух элементов, описываемая произведением неизменных переменных Четвертая область – из двух элементов, описываемая произведением неизменных переменных Окончательно получим минимизированную ФАЛ вида

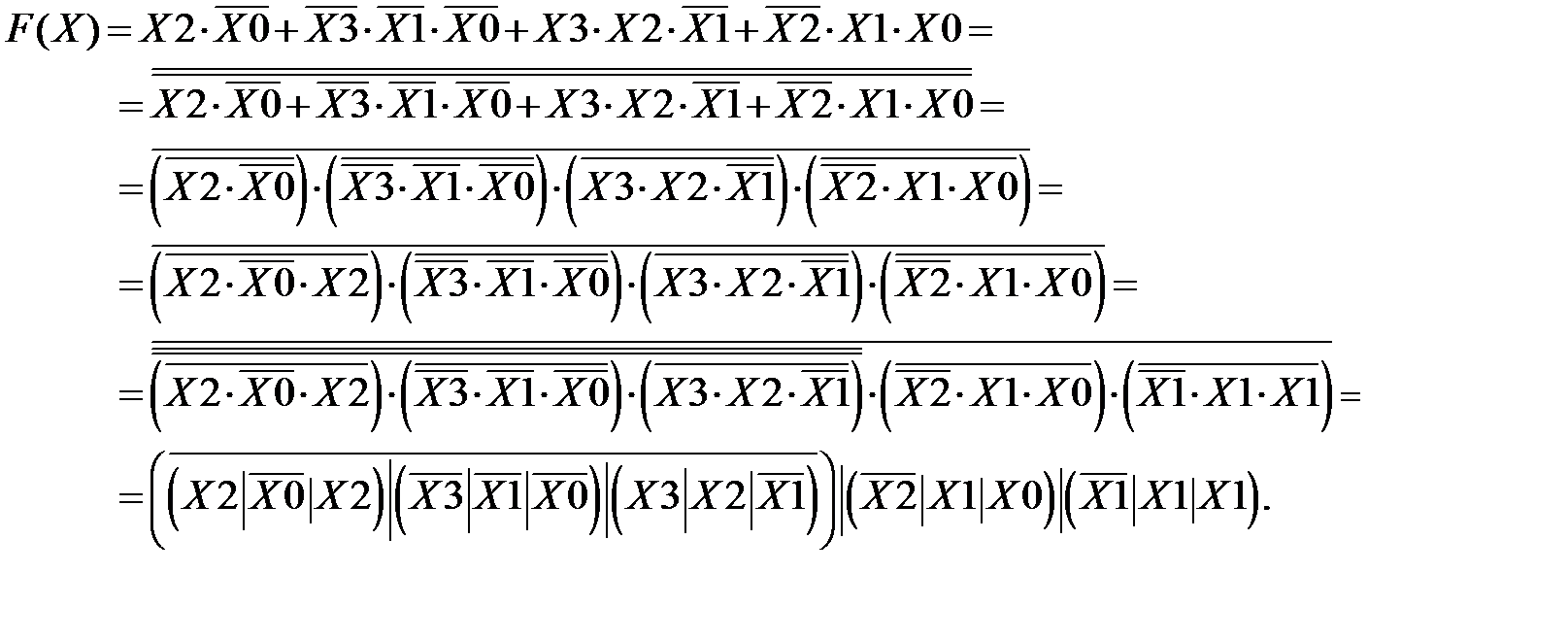

4. Приведем полученную ФАЛ к базису элементов 3И-НЕ

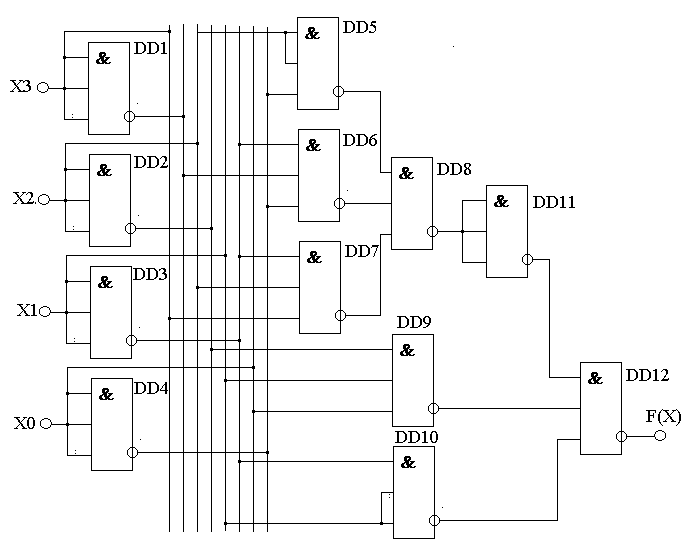

Следует отметить, что последний член выражения 5. По полученному выражению синтезируем схему логического устройства в заданном базисе 3И-НЕ (рис. 2.4.2). Для этого элементы, реализующие операцию функции Шеффера, располагают от входа к выходу согласно их месту в ФАЛ. Для получения сигналов, инверсных входным ( 6. Для получения временных диаграмм коды, заданные в таблице 7.8, последовательно подаются на входы спроектированного устройства и прослеживается сигнал, проходящий по всем элементам схемы. Эту проверку можно выполнить либо вручную, подставляя значения заданных переменных на входы устройства, либо с помощью соответствующего программного обеспечения, например, программы Multisim, использующейся при выполнении лабораторных работ. На рис. 2.4.3. приведены полученные в результате проверки временные диаграммы, поясняющие работу спроектированного устройства. Выводы по заданию 3.2 7. Выводы по заданию 2 должны содержать основные результаты, полученные при выполнении работы. Например: «В результате выполнения работы получены ФАЛ, формально описывающие заданный алгоритм функционирования устройства. Выполнена минимизация СДНФ, в результате которой найдена минимальная дизъюнктивная формы (МДФ) записи ФАЛ. Минимизация выполнена с использованием карт Вейча. МДНФ ФАЛ приведена к виду, предполагающему ее реализацию

Задание 2.3

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-21; просмотров: 282; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.119.117.77 (0.006 с.) |

.

.

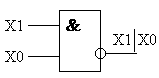

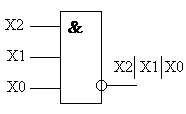

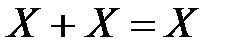

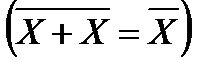

, инвертирование входного сигнала

, инвертирование входного сигнала  .

.

.

. .

. Рис. 2.4.1. Карта Вейча для заданного алгоритма

Рис. 2.4.1. Карта Вейча для заданного алгоритма .

. .

. .

.

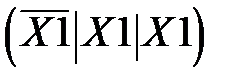

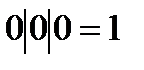

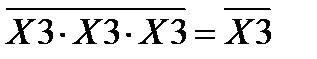

моделирует формирование логической константы, равной логической единицы (при любых значениях Х 1 данное выражение равно «лог.1»). Возможны и другие способы задания логической константы. Например заданием на всех входах элемента 3И-НЕ логического нуля:

моделирует формирование логической константы, равной логической единицы (при любых значениях Х 1 данное выражение равно «лог.1»). Возможны и другие способы задания логической константы. Например заданием на всех входах элемента 3И-НЕ логического нуля:  .

. ,

,  ,

,  ,

,  ), на входе устройства используются дополнительные элементы DD1…DD4, выполняющие роль инверторов. Например, выходной сигнал элемента DD1 определяется выражением

), на входе устройства используются дополнительные элементы DD1…DD4, выполняющие роль инверторов. Например, выходной сигнал элемента DD1 определяется выражением  , т.е. элемент выполняет функцию инвертора.

, т.е. элемент выполняет функцию инвертора.