Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Типовая Структура обрабатывающей части МПСодержание книги

Поиск на нашем сайте

А - аккумулятор СК - счетчик команд РК - регистр команд РАП - регистр адреса памяти РДП - регистр данных памяти Процесс выполнения команды состоит из 2-х циклов: цикла выборки и исполнительного цикла. Цикл выборки начинается со считывания из счетчика команд номера ячейки ОЗУ, содержащей код команды. После считывания содержимое счетчика команд сразу увеличивается на 1. Номер ячейки ОЗУ передается через регистр адреса памяти и адресную шину в дешифратор ОЗУ. Дешифратор ОЗУ выбирает ячейку ОЗУ, содержащую код команды. Код команды считывается из ОЗУ и через шину данных передается в регистр данных памяти. Из регистра данных памяти код команды передается в регистр команд где он хранится до конца выполнения команды и через аккумулятор код команды передается в АЛУ. АЛУ анализирует код команды и если не нужно дополнительного обращения к памяти переходит к исполнительному циклу. Если же нужно дополнительное обращение к памяти, то МП переходит ко второму машинному циклу, который так же начинается с цикла выборки. МП запрашивает в ОЗУ дополнительные данные и выполняет команды. Команды могут выполняться за 1,2 или 3 машинных цикла. В каждом машинном цикле происходит только одно обращение к памяти. Выполнение команды происходит под управлением сигналов, вырабатываемых устройством управления. При выполнении команды АЛУ взаимодействует с РОН. РОН используются для кратковременного хранения операндов и результатов. Триггеры состояния сигнализируют о следующих состояниях МП: обнуление аккумулятора, содержимое знакового разряда, переполнение разрядной сетки, цифры переносов из 8-го и 4-го разрядов, содержимое разряда контроля на четность и нечетность. Адресная шина является однонаправленной, а шина данных - двунаправленной. СТЕК - особый вид памяти, расширяющий функциональные возможности МП. Например при выполнении прерывающей программы в СТЕК помещается номер команды возврата и результат выполнения последней команды перед переходом к выполнению прерывающей программы.

Система команд КР 580 5 груп: 1. Команди пересилки кодів, забезпечують пересилку даних між регістрами або пам’ятю и регістрами. Команди цієї групи не формують при знаків результатів операції. 2. Арифметичні команди, забезпечують операції додавання і віднімання, зміну кодів на 1 (один операнд зберігається в акумуляторі, другий – в регістрі або комірці пам’яті, результат міститься в акумуляторі). 3. Логічні команди, реалізують операції логічного додавання, множення, інвертування, зсувів праворуч та ліворуч та інш. Вихідні операнди зберігаються у регістрах або комірках пам’яті, а результат в акумуляторі. 4. Команди передачі управління, до їх числа входять: команди безумовної передачі, команди умовної передачі, команди звернення до підпрограми, команди виходу з підпрограми. Дані команди не формують при знаків результатів операції. 5. Команди вводу виводу інформації, звернення до стекової пам’яті, деякі команди управління роботою МП.

Програмна модель МП К 1810 ВМ86

Регістри загального призначення Ax, Bx, Cx, Dx -група регістрів загального призначення. Особливістю РЗП є те, що в командах допускається вказувати їх старшу high та молодшу low половини, тобто оперувати байтами і словами. Всі РЗП беруть участь в арифметико-логічних операціях. Для деяких команд регістр АХ виконує функцію акумулятора, тобто джерело і приймач в операціях вводу-виводу. Регістр ВХ –регістр базової адреси, використовується для адресації даних у пам’ять; Регістр СХ – лічильник в операціях зсувів, в командах за циклювання; Регістр DХ – даних, приймає участь при діленні, множенні, містить адресу порту в командах вводу-виводу. Iндексно-вказівні регістри Містять значення зміщень, які використовуються для адресації у межах поточного сегменту пам’яті. Регістри SР та ВР – зберігають зміщення адреси у межах поточного сегменту пам’яті, відокремленого під стек. Регістри SІ та DІ – містять зміщення адреси у межах поточного сегменту пам’яті, відокремленого під дані. Ці регістри можуть використовуватися як РЗП: SР – адресують вершину стеку в пам’ять; ВР – забезпечує доступ до даних, які знаходяться у стеку.

Cегментні регістри Беруть участь у всіх діях ЦП, пов’язаних з адресацією пам’яті. Регістр СS – визначає початкову адресу сегмента пам’яті, виокремленого під підпрограми; Регістр DS - визначає початкову адресу поточного сегмента даних; Регістр SS – визначає сегмент виокремлений для організації стеку; Регістр ЕS– визначає початкову адресу додаткового сегменту даних. Використання цих регістрів визначається типом звернення до пам’яті.

Регістр прапорців СF – перенос РF- парність АF – допоміжний перенос ZF - нульовий результат SF - знак старшого розряду результату ТF – покроковий режим ІF – дозвіл переривання DF - напрямок ОF – переповнення DF - керує напрямком обробки даних в операціях з ланцюгами байтів при DF=1 ланцюг обробляється знизу у гору, при DF=0 – згори вниз. ІF - забороняє чи дозволяє зовнішні переривання. IF=0 – заборона, IF=1 - дозвіл ТF – задає процесору покроковий режим, при якому ЦП після виконання команди зупиняється і очікує зовнішній запуск. ОF – відзначає втрату старшого байту результату. Регістр-Вказівник Команд В ІР формується адреса команди, яка належить до виконання.

Способи адресації. Формати команд Програма – це послідовність команд, виконання яких веде до розв’язання задачі. Команда визначає операцію, яку повинен виконати МП над даними. Команда містить у явній чи неявній формах інформацію про те, де буде розміщуватися результат операції, а також адреса наступної команди. Код команди складається з декількох частин, тобто полей. Склад, призначення та розташування полей – формат команди. Формат команд МП 1810 має різну довжину від 1 до 6 байт. У першому байті записується код операції, у наступних байтах – уявлення адресної інформації. По числу полей виокремлених під адресну інформацію формати команд діляться на: - безадресні - одноадресні - двоадресні В МП 1810 використовується 8 способів адресації з яких п’ять реалізуються за допомогою пост байта. Команди МП 1810можуть адресувати (маніпулювати) один або два операнди, при чому у двохоперандних командах результат операції може бути спрямований на міcце будь-якого з операндів. У таких командах один з операндів повинен знаходитися у регістрі, тобто є команди типу: - регістр - регістр - регістр - пам’ять - пам’ять – регістр - пам’ять – пам’ять - не існує Способи адресації В МП існує декілька способів доступу до пам’яті. а) регістрова адресація операнд знаходиться в одному з РЗП або сегментному регістрі. ця адресація використовується для вказання регістрів, які беруть участь у виконанні операції. П-д: MOV BX,DX вміст регістра DX пересилаємо у регістр ВХ б) безпосередня адресація використовується в операціях з двома операндами: один з операндів знаходиться безпосередньо у вигляді команди, інший – у комірці пам’яті чи РЗП. П-д: MOV DH, 05h число 05h записується у регістр DH ADD DX, 0506h Слово 0506Н додається до регістру DХ, а результат записується до DХ в) пряма адресація в команді вказується безпосередньо адреса одного з операндів П-д: ADD DX, ADDR Addr – адреса 0804h г) відносна адресація використовується в командах переходу виклику підпрограм і управління циклами П-д: JMP 0504 h перехід за адресою 0504Н CALL 0806h Виклик підпрограми з адресою 0806Н д) непряма (косвеная) регістрова - непряма-базова адреса операнда вказує один з регістрів ВХ, ВР П-д: MOV [BX], AX пересилка вмісту АХ за адресою записаною в ВХ. - непряма-індексна адреса операнда вказує один з регістрів SІ, DІ MOV [SI], CX SUB AX, [DI] - індексно-базова об’єднує базову та індексну адресації П-д: MUL AX, [BX+DI] в регістрах ВХ та DІ зберігаються складові адреси [BX+DI] - находження адреси комірки пам’яті, в якій зберігається другий множник

Периферійні пристрої підключаються до комп'ютера за допомогою адаптерів або контролерів. Адаптер — це засіб сполучення деякого зовнішнього пристрою з визначеною шиною МПС. Контролер також виконує подібні функції, але він здатний на самостійні дії після одержання команд від машини. Складний контролер може мати i власний процесор. Сьогодні часто терміни "адаптер" i "контролер" вважають майже синонімами. Уci зовнішні інтерфейси мають у своєму складі адаптер або контролер. Мікропроцесорні комплекти КР580 i K1810 мають таю програмовні інтерфейсні контролери (адаптери): • контролер переривань — К1810ВН59 (ВН59); • контролер ПДП — КР580ВТ57 (ВТ57); • програмований таймер — КР580ВИ53 (ВИ53); • паралельний інтерфейс — КР580ВВ55 (ВВ55); • послідовний інтерфейс — КР580ВВ51 (ВВ51). Програмовний контролер переривань Під час виконання поточної (фонової) програми в комп'ютері виникають заздалегідь невідомі події, ягі вимагають миттєвої реакції на них (аварія в системі готовність ПП до передачі даних, ділення на нуль та інш.). Реакція полягає в перериванні фонової програми, переході до підпрограми обслуговування даної події та повернення програми в попередній стан. Кожна подія, яка вимагає переривання, супроводжується сигналом — запитом переривання. Переривання — важлива архітектурна особливість машини, яка дозволяє ефективно організовувати роботу процесора за наявності декількох паралельних процесів.

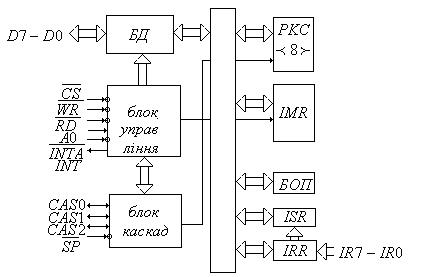

Для технічної реалізації переривань використовують програмовані контролери переривань (ПКП). До ПКП відноситься мікросхема ВН59 (аналог модуля 8259) з такими характеристиками схемотехнологія — n-МОН, напруга живлення — плюс 5 В, споживана потужність — 1 Вт. Структура ПКП ВН59 показана на рис. 11.21. До складу ПКП ВН59 входять: • двонаправлений восьмирозрядний буфер даних БД; • блок керування (входи • регістри запитів переривань IRR (входи IR7-0), керуючих слів RKC, стану • блок каскадування (вхід SP, двонаправлені виходи (СAS3-0); • блок оброблення прюритвт1в (БОП) Прогрямований контролер переривань сприймає запити на переривання від восьми ПП; за рахунок каскадування за допомогою виходів СAS3-0 число виходів для запитів може збільшитися до 64. Запити, які поступають на входи IR7-IR0, фіксуються в pericтрі запитів переривання IRR. Блок оброблення пріоритетів визначає найбільший пріоритетний запит. Блок керування формує сигнал запиту переривання INT, який поступає на такий же вхід мікропроцесора. Якщо в мікропроцесорі переривання дозволено, то він відповідає контролеру сигналом INTA, який поступає на такий же вхід ПKП. В результаті на ШД від КПК видається спочатку перший байт — код команди са11,а потім другий i третій байти, які визначають адресу підпрограми. Після цього розряд регістра запитів IRR, на який поступив запит з вищим пріоритетом, обнуляється i встановлюється одиниця у відповідному розряді регістра станів ISR. За допомогою завантаження керуючих слів ініціалізації ІСW в режимі настроювання i операційних слів OCW при обслуговуванні запитів ПКП може програмуватися на такі режими обслуговування переривань: · пріоритети зовнішніх пристроїв фіксовані; · циклічний зсув пріоритетів; · спеціального маскування, · послідовного опитування ПКП.

Генератор тактових імпульсів ДО181ОГФ84 Мікропроцесор ВМ86 являє собою синхронну цифрову схему, всі процеси в якій синхронізуються послідовністю тактових імпульсів. На відміну від ВМ80 у розглянутому МП для синхронізації використається не дві, а одна тактова послідовності. У комплекті із ВМ86 застосовується мікросхема генератора тактових імпульсів (ГТИ) типу ДО1810ГФ84. Схема ГТИ представлена на мал. Як задаючого генератор звичайно використається внутрішній кварцовий генератор КГ, що працює із кристалом кварцу, підключеним до входів XІ й Х2, Замість кварцу можливе підключення Схема генератора тактових імпульсів ДО181ОГФ84

паралельного LC-контуру до входу TANK через розділовий конденсатор. Що задає може також служити зовнішній генератор імпульсів, що підключає на вхід EF1_. Вхід F/C використається для вибору генератора, що задає: F/C = 0 відповідає внутрішньому, a F/C= 1 - зовнішньому генератору. Тактові імпульси подаються на вихід CLK; їхня частота дорівнює 5 МГЦ н утвориться розподілом частоти генератора, що задає (f зг= = 15 МГЦ) на 3. Вхід CSYNC (тактова синхронізація) використається в системах, де необхідні два або більше ГТИ, що працюють синхронно. Для синхронізації зовнішніх пристроїв, що працюють на зниженій частоті, ГТИ виробляє на виході PCLK тактові імпульси із частотою вдвічі нижче, ніж на виході CLK. Крім того, на вихід OSC подається синусоїдальна напруга кварцового генератора, що може використатися для контролю роботи генератора, що задає, або для інших цілей. Генератор тактових імпульсів формує також керуючі сигнали RESET (скидання) і READY (готове). Сигнал RESET тривалістю 50 мкс здійснює початкову установку мікропроцесора. Цей сигнал формується в ГТИ із зовнішнього сигналу RES за допомогою тригера Шмітта, що забезпечує крутий фронт сигналу, і D-тригера, що здійснює його тимчасову прив'язку до тактових імпульсів. Після надходження сигналу RESET мікропроцесор припиняє роботу й залишається в режимі очікування до закінчення цього імпульсу. Потім починається процес ініціалізації МП, що триває 10 тактів і полягає в обнулінні сегментних регістрів DS, SS й ES, регістра прапорів F і покажчика команд ІP, а також в установці значення FFFFH у регістрі програмного сегмента CS (буква Н у кінці числа позначає, що воно записано в шестнадцятиричной системі числення). Сигнал READY управляє режимом очікування МП і дозволяє забезпечити сполучення в часі роботи мікропроцесора з роботою зовнішніх пристроїв (ВУ), що мають меншу швидкодію. У ГТИ сигнал READY формується тригером синхронізації готовності, що по входах RDY1, AEN1 й RDY2, AEN2 управляється від двох зовнішніх пристроїв системи. Входи RDYl й RDY2 визначають готовність цих пристроїв, а на входи AEN1 н AEN2 подаються сигнали дозволу аналізу відповідних сигналів готовності. Якщо швидкодія всіх зовнішніх пристроїв системи погоджено зі швидкодією МП і немає необхідності в режимі очікування, то входи готовності підключаються до джерела харчування, а входи дозволу аналізу заземлюються. При цьому сигнал READY виробляється схемою синхронізації готовності під дією внутрішнього сигналу синхронізації CLK.

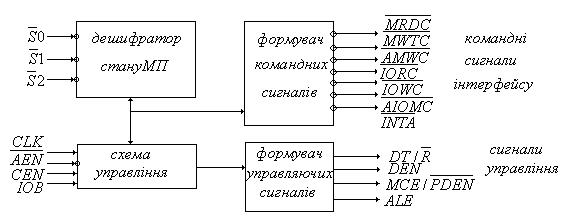

Системний контролер (СК) ДО1810ВГ88 Схема системного контролера (СК) ДО1810ВГ88 зображена на мал.

До складу схеми входять дешифратор стану МП, формувачі командних і керуючих сигналів і схема керування. На вхід CLK подаються тактові імпульси від ГТИ, а на входи AEN, CEN, ІOB - зовнішні керуючі сигнали. Сигнал AEN служить для дозволу видачі семи командних сигналів від формувача командних сигналів. Сигнал CEN дозволяє як видачу командних сигналів, так і видачу сигналів керування DEN й PDEN. Вхід ІOB служить для завдання режиму роботи системного контролера. При ЮВ=! системний контролер функціонує в режимі шини уведення - висновку, а при ЮВ = 0 - у режимі системної шини. У режимі уведення -висновку (ІOВ = 1) при виконанні команд читання-запису, яким відповідають певні коди стану МП,СК виробляє сигнали PDEN й DT/R для керування передачею інформації. Сигнал PDEN управляє видачею інформації з ВУ на шину уведення - висновку й назад, тобто виконує ту ж функцію для портів уведення - висновку, що й сигнал DEN для організації обміну з ВУ й тому командні сигнали в режимі уведення - висновку не використаються. У режимі системної шини (ІOВ=0) СК виробляє командні сигнали відповідно до коду стану МП. Ці сигнали формуються тільки після надходження сигналу AEN, що інформує системний контролер про те, що ШД вільна для передачі інформації. Сигнал МСЕ виробляється під час обробки переривань і служить для визначення моменту часу зчитування на ШД адреси веденого контролера пріоритетних переривань при каскадиюванні цих контролерів. Якщо в системі переривань є тільки один контролер, то сигнал МСЕ не використається. Призначення командних сигналів у режимі системної шини полягає в наступному. Сигнал AІOWC=0 з'являється перед командним сигналом ІOWC і служить для підготовки ВУ, інформуючи його про те, що через певний час піде сигнал висновку. Сигнал ІOWC = 0 служить для ВУ командою читання інформації зі ШД, а сигнал ІORC -0 - командою запису інформації на ШД. Аналогічним образом сигнал AMWC= = 0 з'являється перед командним сигналом MWTC і служить для підготовки пам'яті, інформуючи її про те, що через певний час надійде сигнал запису. Сигнал MWTC = 0 є для ОЗУ командою запису інформації із шини даних, а сигнал MRDC - командою витягу інформації з ОЗУ (або ПЗУ) на шину даних. Вихідний сигнал ІNTA=0 визначає момент початку обробки запиту переривання від ВУ.

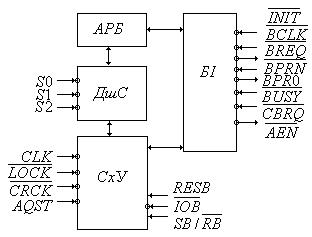

Арбітр шин К1810 ВБ89 Кожний ЦП має свій власний арбітр шин. У багатопроцесорній МПС пріоритетний доступ до системної шини здійснює ВБ89. Мікросхема містить: - схему арбітра АРБ; - дешифратор стану ДшС; - схему управління арбітражем СхУ; - блок шинного інтерфейсу БІ.

Вхідні сигнали: - S2-0 - сигнали стану МП; - CLK – вхід синхронізації; - BCLK - вхід синхронізації вхід системної синхронізації; - INIT -скид АШ; - LOCK -блокування СШ; - IOB - вибір режиму роботи з шиною вводу-виводу; - CRCK - сигнал загального блокування СШ; - AQST - любий запит; - SB\RB - вибір системної або локальної шини; - RESB -вибір режиму роботи резидентної шини. Вихідні сигнали: - BREQ, BPR0, BUSY, CBRQ - використовуються для організації схеми визначення пріоритетів; - AEN - дозвіл доступу до СШ; За допомогою АШ організують наступні схеми: 1. з послідовним пріоритетом; 2. з паралельним пріоритетом; 3. паралельним з циклічно змінюючим пріоритетом. Робота схеми

У багатопроцесорних системах, які містять як системну так і резидентну шини, кожний МП може бути підключений до однієї чи більше шин. У той же час два і більше МП можуть бути підключені до однієї шини. У першому випадку треба визначити до якої шини повинен бути підключений МП, у другому випадку – який МП має більший пріоритет тобто якому МП повинен бути забезпечений доступ до шини. Розв’язання цих питань виконує АШ. На малюнку зображені два МП (ведучий та відомий), які підключені до локальної шини ЛШ. Присутність зв’язків RQ/GT забезпечує вихід одного МП на ЛШ. Схема шинного інтерфейсу підключає локальну шину до зовнішньої шини, причому одна ЛШ підключається до будь-якого числа зовнішніх і для кожного такого підключення потрібна своя СШІ. На рис. 2 СШІ: 1-а підключає ЛШ до резидентної шини, а 2-а – до системної. СШІ містить системний контролер ВГ88, шинний формувач ВА 86, фіксатор адреси ІР82. АШ використовує входи S2- S0 для визначення того, що МП потрібна СШ і він дозволяє доступ до неї, якщо у схемі немає іншого МП з більш високим пріоритетом, який використовує СШ. Коли АШ дозволяє доступ МП до СШ (AEN=0), він стає активним. Якщо СШІ СШ відключена, то АШ пасивний і МП може використовувати тільки резидентну шину РШ. АШ вважає СШ зайнята або вільна в залежності від значення сигналу BUSY (BUSY=0 –шина зайнята, BUSY=1 – шина вільна). Захватив управління шиною, АШ зберігає її до початку виконання команди НАLТ або стан 011, 111, або коли ВРRN=1, тобто є запит з високим пріоритетом. Якщо АШ отримає вхідний сигнал LOCK=0, то він зберігатиме керування шиною на весь час дії цього сигналу. Сигнал AQST потребує арбітр звільнити шину. АШ може працювати 4-х режимах для їх завдання існує два входи: RESB та IOB. 1. режим роботи з СШ IOB=1 RESB=0 2. режим роботи з СШ пам’яті та РШ вводу/виводу IOB= RESB=0 3. режим роботи з СШ пам’яті, РШ та РШ вводу/виводу IOB= 0 RESB=1 4. режим роботи з СШ та РШ IOB=RESB=1

Система команд мікропроцесора 1810 І Команди передачі (пересилки) Відрізняють 4 типа пересилок: - загальні команди передачі даних; - команди передачі даних з участю стека (стекові команди); - команди вводу-виводу; - команди передачі ланок байтів чи слів. Ці команди не впливають на прапорці. Лекція № Загальні команди Включають команди, які здійснюють передачі регістр-регістр, регістр - пам’ять, пам’ять -регістр. а) MOV – передати, переслати MOV dst, src – здійснює передачу змісти джерела у приймач. dst – destination – приймач; src – source – джерело. В якості джерела та місця призначення може служити регістр, пам’ять або сегментний регістр. Крім того, джерелом можуть являтися данні (константи), які безпосередньо представлені у формі команди. б) XCHG – обміняти здійснює обмін байтами чи словами між джерелами. В якості джерел можуть бути регістри ти пам’ять. Сегментні регістри не використовуються при обміні. XCHG CX, [BP] XCHG AL,BL;обмін байтами регістр-регістр XCHG AX, CX;обмін словами регістр-акумулятор в) LEA, LDS, LES LEA – витягує не сам операнд, а його виконавчу адресу, тобто передає 16-розрядну адресу операнда в 16-розрядний регістр, код якого вказаний у пост байті у полі reg. Використовується при складанні підпрограм. П-д: перед викликом підпрограми виокремлений регістр ВХ завантажується адресою змінної, яка записана у пам’яті, якщо перед викликом підпрограми виконати LEA BX, ALFA ALFA – ім’я комірки пам’яті, яка містить змінну, то підпрограма буде використовувати у якості параметра змінну з ALFA. LDS, LES – використовують при зверненні до даних, які знаходяться поза поточних сегментів DS або ES, тобто необхідно змінити базову адресу сегмента. Пара 16-розрядних адрес: база сегмента та зсув – вказівник, який завантажується у пам’ять. Адреса вказівника записується у постбайти у полях mod та r/m. Зсув знаходиться у двох перших байтах, а базова адреса сегмента в третьому та четвертому. За командою LDS (LES) відбувається звернення до вказівника і здійснюється завантаження регістра DS (ES) базовою адресою, а зсув знаходиться у пост байті команди в полі reg. при виконанні цих команд в адресуємий регістр передається адреса. LEA LOAD EA- завантаження ефективної адреси (виконавчої). LEA reg/MEM- обчислюється ЕА пам’яті та її значення завантажується у вказівний регістр. LDS i LES- обчислюється ЕА пам’яті, яка додається до змісту регістра DS, а далі слово з пам’яті за отриманою адресою завантажується в адресує мий командою загальний регістр, а наступне слово з пам’яті завантажується в DS (команда LDS) або ES (LES команда) Взагалі у команді LDS вказується регістр – SI,а в команді LES – DI. LDS SI,[DI] г) LAHF i SAHF – служать для спрощення програмної сумісності МП К1810 К580 LAHF – здійснює передачу молодшого байту регістра прапорців в регістр, а SAHF – реалізує зворотну передачу, яка міститься в молодшому байті старший байт не змінюється. Стекові команди а) PUSH – служить для занесення змісту джерела у стек. Джерелом може бути регістр, сегментний регістр або пам’ять. Перед виконанням команди формується адреса верхівки стеку: (SP) – (SP)-2 PUSH SI; включення у стек регістра б) POP – служить для вилучення 16-розрядного операнда зі стеку та для пересилки його у регістр, сегментний регістр чи пам’ять. Операція завершується формуванням нової адреси верхівки стеку: (SP) – (SP)+2 POP DS;вилучення зі стеку у сегментний регістр POP DX; вилучення зі стеку у регістр Команди вводу-виводу У цих командах використовується акумулятор як джерело чи місце призначення операнда. а) IN – ввод- служить як пересилка даних з порту вводу до акумулятора (AL або AX) номер порту задається у другому байті команди або у регістрі DX. П-д: IN AC, port У другому байті знаходиться пряма адреса порта. Порт у діапазоні 00-FF. IN AX, DX;16-бітна адреса порту знаходиться у регістрі DX і максимальна адреса порту дорівнює FFFF. б) OUT – вивід – служить для пересилки даних з акумулятора (AL, AX) у порт виводу. Команди ввода/виводу з прямими адресами портів, називаються статичними, а з змінними – динамічними. JN AX, 40H;ввод слова (статичний) JN AL, DX; ввод байта (динамічний) OUT 80H, AL; вивід байта (статичний) OUT DX, AX; вивід слова (динамічний).

Лекція № Команди передачі управління (КПУ) КПУ змінюють вміст ІР – вказівника команд, а деякі і вміст регістра сегмента кодів СS. За допомогою цих команд можна змінити послідовність виконання команд у програмі, тому що регістр СS містить базову адресу поточного сегменту кодів, з якого вибираються команди, а регістр ІР – адресу, яка задає зсув команди відносно початку сегмента кодів. До цієї групи команд відносяться: 1. команди безумовного переходу і умовного переходу 2. команди виклику підпрограми та повернення до підпрограми 3. команди циклів 4. команди переривань.

|

|||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-05; просмотров: 230; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.15.15.91 (0.01 с.) |

);

);