Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Етапи мінімізації за допомогою карт КарноСодержание книги

Поиск на нашем сайте

Перемісний закон Для додавання AVB=BVA Для множення AB=BA Сполучний закон Для додавання (AVB)VC=AV(BVC) Для множення (AB)C=A(BC) Закон подвійності Для додавання Для множення Розподільний закон Для додавання (AVB)C=ACVBC Для множення (AB)VC = (AVC)(BVC) Тотожності

Формули

п-д: довести справедливість закону подвійності:

ІІІ Заключна частина уроку Підведення підсумків та завдання домашнього завдання

Лекція №7 Стандартні форми. Способи переходу від нормальної до доконаної форми Мета: Познайомити з методикою розрахунку ДКНФ Хід уроку І Повідомлення теми та мети уроку ІІ Загальна частина уроку

ЦА можна побудувати у двох базисах: І-НІ та АБО-НІ, використовуючи відповідні логічні елементи, щоб побудувати схему у тому чи іншому базисі необхідно скористатися двома методиками розрахунку: - розрахунок схеми, яка працює на елементах АБО-НІ; - розрахунок схеми, яка працює на елементах І-НІ. Схеми можуть працювати однаково як на елементах І-НІ так і на елементах АБО-НІ – все буде залежати тільки від кількості елементів, а з цього залежить надійність та вартість схеми. Методика розрахунку на елементах АБО-НІ – находження доконаної конюнктивної нормальної форми (ДКНФ), а на елементах І-НІ –доконаної диз’юнктивної нормальної форми (ДДНФ). Методика ДКНФ 1. Будуємо таблицю стану роботи пристрою (закон поведінки), де вхідними змінними є входи А, В, С, а виходом є функція F.

2. Із таблиці стану вибираємо строки, де функція приймає значення 0. 3. Елементи строки А, В, С додаються між собою, а строки множаться. Функція роботи пристрою буде мати вигляд, причому, якщо елемент строки дорівнює 0, йому присвоюється пряме значення.

4. Використовуємо формулу Де-Моргана

5. Будуємо схему.

ІІІ Заключна частина уроку Підведення підсумків та завдання домашнього завдання

Лекція №8 Методика ДДНФ Мета: Познайомити з методикою розв’язання синтезу ДДНФ Хід уроку І Повідомлення теми та мети уроку ІІ Загальна частина уроку

1. Будуємо таблицю стану роботи пристрою (закон поведінки), де вхідними змінними є входи А, В, С, а виходом є функція F.

2. Із таблиці стану вибираємо строки, де функція приймає значення 1. 3. Елементи строки А, В, С множаться між собою, а строки додаються. Функція роботи пристрою буде мати вигляд, причому, якщо елемент строки дорівнює 0, йому присвоюється інверсне значення.

4. Використовуємо формулу Де-Моргана

5. Будуємо схему.

Аналізуючи виконання схеми в одному та іншому базисі, схеми мають однакову кількість логічних елементів. Щоб скоротити схему, бо вона має несуттєві елементи, використовують спеціальну методику скорочення. ІІІ Заключна частина уроку Підведення підсумків та завдання домашнього завдання

Лекція №9 Мінімізація логічних функцій Мета: Вивчення загальних методів мінімізації Хід уроку І Повідомлення теми та мети уроку ІІ Загальна частина уроку

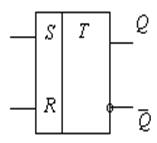

Мінімізацію можна здійснювати різними методами: - Метод Квайна - Карти Карно - Карти Вейча Перший метод є аналітичним та займає багато часу для находження елементарних функцій. Другий метод Карно-Вейча –графічний, який є більш інформативним. Суттєвість будь-якого метода скорочення елементарних функцій полягає у знаходженні сусідніх функцій. Це означає, що 2 елементарні функції повинні відрізнятися на одну змінну, тобто мати загальну частину. Таких функцій буде 8 і вони будуть построєні наступним чином: RS-тригер а) асинхронний RS-тригер називається асинхронним, якщо інформація у тригер записується без урахування синхросигналу. Т-однотактний тригер з одноступеневим управлінням, тобто має одну ступень запам’ятовування інформації.

RS-тригер можна представити у двох базисах: - І-НІ

- АБО-НІ

б) синхронний Якщо хоча б по одному із входів інформація у тригер записується примусово, тобто з надходженням синхросигналу С=1, то такий тригер має назву синхронний. Функціональна схема синхронного RS- тригера

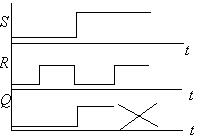

Двотактний тригер Часові діаграми RS- тригера

Для одноступеневого тригера спрацьовування відбувається по фронту, а для багатоактного – по спаду. D – тригер (тригер даних) – тригер з одним входом, який реалізує функцію часової затримки. Часові діаграми

Функціональна схема

JK – тригер – універсальний – в залежності від поєднання його входів, він може працювати як синхронний двотактний) RS, T, D тригер. Інформаційні входи J та K еквівалентні входам R та S установки тригера у стан 1 та 0. Функціональна схема

ІІІ Заключна частина уроку Підведення підсумків та завдання домашнього завдання

Лекція №11 Регістри Мета: Вивчити загальне призначення та роботу регістрів Хід уроку І Повідомлення теми та мети уроку ІІ Загальна частина уроку

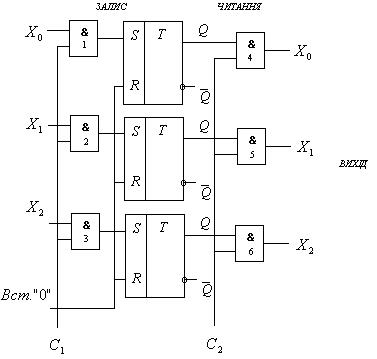

Регістр – це вузол ЕОМ призначений для тимчасового зберігання, зсуву ліворуч чи праворуч інформації та виконання над інформацією логічних операцій. Класифікація 1. за видом здійснюючих операцій · регістри прийому · регістри зсуву · регістри передачі інформації 2. за способом прийому та передачі інформації · послідовні · паралельні · послідовно-паралельні 3. за кількістю каналів, по яким інформація надходить на вхід розрядів · одноканальні · пара фазні однофазні - це регістри, до яких інформація надходить на кожний розряд по одному каналу. 4. за кількістю тактів управління, які необхідні для запису інформації · однотактні · двотактні · багатоактні Паралельний регістр Паралельний регістр побудований на RS- тригерах та комбінаційних логічних елементах. На початку роботи всі тригери встановлені у стан „000”. За допомогою сигналу установка «0» елементи І від 1-3 пропускають двійкову інформацію на вхід S- тригерів при наявності синхросигнала С1. Для передачі коду з регістрів входи R- тригерів установлюють тригер у нульовий стан, при цьому на входах елементів І 4-6 надходять сигнали передачі коду із тригерів і синхросигнал С2, за допомогою якого елементи І пропускають одиничну інформацію в наступний пристрій.

Послідовні суматори Послідовні суматори – це суматори, які дозволяють виконувати або здійснювати порозрядне додавання двох чисел починаючи з молодших розрядів до старших. Сигнал переносу враховується в наступний момент переносу, а до цього запам'ятовується в елементі затримки. Паралельний суматор Паралельний суматор - це суматор, у якому розряди що складають х и в уводяться на всі входи суматорів при наявності синхросигнала. Утворення сигналу S у кожному розряді залежить від наявності одиниці переносу в попередньому розряді.

ІІІ Заключна частина уроку Підведення підсумків та завдання домашнього завдання ТКЗ №4 Лекція №15 Схеми порівняння Мета: Вивчити призначення та побудову схем порівняння Хід уроку І Повідомлення теми та мети уроку ІІ Загальна частина уроку Арифметикологические операції в ЕОМ містять у собі порівняння двох чисел по модулю, знаку й порядку. Розглянемо порівняння двох однорозрядних чисел Таблиця стану

Рівняння

Функціональна схема:

ІІІ Заключна частина уроку Підведення підсумків та завдання домашнього завдання

Лекція №16 Перетворювачі кодів Мета: Вивчити призначення та будову перетворювача кодів Хід уроку І Повідомлення теми та мети уроку ІІ Загальна частина уроку Перетворювачі кодів – це вузли ЕОМ, на виході яких в залежності від знака числа може бути отримане двійкове число, як в прямому, так і у зворотному чи додатковому кодах.

Перемикальна функція: Функціональна схема перетворювача:

Код КОИ 7, КОИ 8 Алфавіт становить сукупність елементарних символів, за допомогою яких мовою записуються програми. Стандартний алфавіт містить: " Графічні символи (прописні й малі літери, арабські цифри, обмежники,:;() 94); " Керуючі символи 33. Для передачі даних використають 7-розрядний код. Щоб мати можливість представити в цифрових машинах інформацію, виражену символами алфавіту, необхідно самі символи закодувати певними наборами двійкових цифр. В ЕОМ застосовують системи засновані на поданні символів 7-розрядними кодами (КОИ-7) і 8-розрядними (КОИ-8). Способи кодування на стор.48 табл. 2.1: У КОИ-7 - символи розташовані по трьох кодових таблицях: КОИ-7Н0, КОИ- 7Н1, КОИ-7 С1. КОИ-7Н0 - букви російського алфавіту + спеціальні символи; КОИ-7Н1 - букви латинського алфавіту + спеціальні символи; КОИ-7С1 - додаткові керуючі символи. Для однозначності кодування графічних символів, якщо використається табл.КОИ-7Н0, перед групою символів посилає код "ВХ" або нічого, якщо КОИ-7Н1, то код символу "ВЫХ", для КОИ-7С1 - символ "АР2". П-д: буква а відповідає коду в табл. КОИ-7Н0 - 1000001. У КОИ-8 позиції двійкових цифр пронумеровані в КОИ-7 відповідає 1 для табл. КОИ-7Н0 і КОИ-7С1, а 0 для КОИ-7Н1.

Перевагою КОИ-8 у порівнянні з КОИ-7 є наявність єдиної кодової таблиці й можливість кодування до 256 символів, а не повторювати кодування однакових стовпців 0-3 таблиць КОИ-7Н0 і КОИ-7Н1. Коди для виявлення й виправлення помилок Коди для виявлення й виправлення помилок - служать для контролю правильності передачі інформації між пристроями й усередині будов машини, а також для контролю всього процесу обробки інформації на машині. Код - сукупність символів, за допомогою яких відображається інформація. Вимоги до коду: 1. Код повинен виявляти найбільше що часто зустрічаються види помилок; 2. Заданий ступінь виявлення помилки повинна досягатися мінімальним числом контрольних розрядів; 3. Процедура кодування повинна бути простій і швидкої. Код Хемминга Код Хемминга - код що дозволяє виявити й виправити одиночні помилки в переданих числах. Код складається з: m позицій, використовуваних для передачі інформації й k- як контроль (перевірки). Кожен контрольний розряд закріплюють за певною групою. Перед подачею числа в контрольні розряди записуються символи 0 або 1, залежно від парності кожної групи. 12 11 10 9 8 7 6 5 4 3 2 1

К4 К3 К2 К1 При контролі правильності прийому n- розрядного числа (12=n) виконується 4 перевірки на парність.

Після передачі числа в прийомному пристрої виробляється k перевірок на парність всіх k контрольних груп. Після кожної перевірки в спеціальний регістр помилок записуються нулі, якщо результат перевірки свідчить про відсутність помилок, і одиниці, якщо результат свідчить про наявність помилки. Отримана послідовність нулів й одиниць утворить двійкове число, що повинне вказувати номер позиції (розряду) з перекрученим символом. При відсутності помилки в цій комбінації будуть записані тільки нулі. Утворення контрольних груп: Перша група (перевірка) охоплює всі позиції коду, номер яких у двійковій системі має 1 у першому розряді (1,3,5,7,9,11,13,...) Друга перевірка - включає позиції, номер яких має одиницю в другому розряді (2,3,6,7,10,...) і т.д. П-д: Принцип визначення помилки при передачі числа в коді Хемминга. Нехай передається число 1011 (11). Це число перетвориться в 7-розрядний коригувальний код: 7 6 5 4 3 2 1 1 0 1 1 К3 К2 К1 Контрольні розряди автоматично записуються при формуванні переданого коду відповідно до правила перевірки на парність

Розрахуємо код прийнятої комбінації без перекручування символів:

Припустимо, що при передачі числа був перекручений один із символів. Визначимо номер розряду перекрученого символу в прийнятому числі. Для цього зробимо три перевірки на парність (при перевірці враховуються й контрольний розряд):

Одержимо перевірочне число 111=7. Щоб виправити помилку, необхідно символ в 7 розряді інвертувати. Процес виправлення помилок виробляється автоматично. ІІІ Заключна частина уроку Підведення підсумків та завдання домашнього завдання

Лекція №17 Мультиплексори та демультиплексори Мета: Вивчити призначення та роботу мультиплексора та демультиплексора

Хід уроку І Повідомлення теми та мети уроку ІІ Загальна частина уроку Мультиплексори Це вузли перетворюючі паралельні цифрові коди у послідовні. Мультиплексом має декілька інформаційних входів, синхронний вхід та один вихід. Число інформаційних входів та адресних пов’язані співвідношенням: Подаючи на адресні входи інформаційні входи – можна передавати паралельні коди (4-х розрядні) з цих входів на вихід у послідовному коді. Таблиця стану для чотирьох розрядного мультиплексора: Перемикаюча функція для виходу буде мати наступний вигляд: Кли необхідно передати на вхід Багато розрядні вхідні данні у паралельній формі, використовується паралельне вмикання мультиплексорів, таке обєднання має назву мультиплекс орне дерево. Демультиплексори Це вузли, які здійснюють перетворення інформації з послідовної форми у паралельну. Він має один інформаційний вхід та декілька виходів. Таблиця стану Перемикаюча функція для виходу має вигляд: Програмуємі логічні матриці Велика розрядність мікрокоманд приводить до необхідності використання великого обсягу памяті мікрокоманд (ПМК). Ефективним способом економії обсягу ПМК вважається використання ПЛМ – інтегральних комбінаційних логічних схем. Структура ПЛМ складається у вигляді 2-х матриць: матриці адрес та даних, за допомогою яких здійснюється перетворення n –розрядного входного коду в m – розрядний вихідний сигнал. Програмування матриць складається в усуненні непотрібних зв’язків за допомогою фотошаблонів чи вижигання. ПЛМ можна реалізовувати необхідні перемикаючі функції, які задають закон функціонування керуючого мікро програмного автомата. ІІІ Заключна частина уроку Підведення підсумків та завдання домашнього завдання

Лекція №18 Контрольна робота Мета: Перевірити знання з основ дискретної автоматики Обладнання: дидактичний матеріал Адміністраторська контрольна робота Спеціальність: „Обслуговування верстатів з ЧПУ та РКТ” Варіант №1 1. Програмна модель мікропроцесора і8080 (призначення регістрів). 2. Описати призначення, склад та роботу мікросхеми генератора тактових імпульсів 3. Пряма адресація. Навести приклад. 4. Записати команди для виконання наступних завдань та коментар для них: - передати дані з регістра Сl у регістр ВL. До виконання команди регістр ВL містить число 101011111, а СL-00001111; - додати вміст двох регістрів: BL i CL. До виконання команди вміст регістрів:BL=01110111,CL=11110001. Записати значення прапорців.

Адміністраторська контрольна робота Спеціальність: „Обслуговування верстатів з ЧПУ та РКТ” Варіант №2 1. Структурна схема мікропроцесора і8086 її складові та принцип роботи. 2. Описати призначення, склад та роботу мікросхеми контролера системної шини. 3. Регістрова адресація. Навести приклад. 4. Записати команди для виконання наступних завдань та коментар для них: - переслати вміст комірки памяті DS:[100EH] у регістр CX та здійснити обмін двох регістрів CX i BX; - виконати віднімання вмісту комірки памяті з адресоюES:2002H та числа 40Н з урахуванням позики від попередньої операції

Адміністраторська контрольна робота Спеціальність: „Обслуговування верстатів з ЧПУ та РКТ” Варіант № 3 1. Програмна модель мікропроцесора і8086 (призначення регістрів). 2. Описати призначення, склад та роботу мікросхеми арбітра шин. 3. Непряма адресація. Навести приклад. 4. Записати команди для виконання наступних завдань та коментар для них: - завантажити сегментний регістр початковим значенням 4000Н. (примітка: щоб завантажити сегментний регістр будь-яким значенням, треба записати його у РЗП, а потім передати у сегментний регістр); - виконати команду ділення подвійного слова, що зберігається у регістрах BX,AX, на слова в регістрі DX.

ІІ семестр 2 часть Вступление. Общие принципы построение микропроцессорных систем (МПС) МПС называют информационно - вычислительных средств, туда входит один или несколько микропроцессов (МП). На основе МПС реализуют микрокомпьютеры, ПК, информационные сети и т.д МПС состоит из: 1) Процессор, который выполняет основные функции управления и обработку информации. 2) Запоминающее устройство – предназначенные для хранения программ и данных. 3) Устройство ввода – вывода, которые обеспечивают взаимосвязь с внешними устройствами. Структурная схема МПС.

ЦП – центральный процессор RAM – оперативная память КПП – контролер прикладн. программ ПУ – периферийное устройство Организация шин Шина – это информационный канал, который объединяет все функциональные блоки МПС и обеспечивает обмен данными в виде двоичных чисел. Конструктивно шина представляет собой n – проводников и один общий проводник (земля). Данные по шине передаются в виде слов – группы бит. Все блоки МПС соединены с единой параллельной шиной (это шина, в которой n – бит информации передается по отдельным линиям одновременно), которая называется системна шина. Системная шина содержит ША, ШУ, ШД ША – является однонаправленной, она предназначена для передачи адреса ячейки памяти или устройство ввода – вывода (увв).

ШД – является двунаправленной. Она предназначена для передачи данных между блоками МПС.

ШУ – предназначена для передачи управляющих сигналов, хотя направления управляющих сигналов может быть разной, ШУ не является двунаправленной, и т. к для сигналов разного направления используется отдельные линии.

Лекция №1 Архитектура микропроцессора (МП) Определяет составные части и взаимодействия между ними. Архитектура включает в себя: 1) Структурная схема МП 2) Программная модель МП (описание, функции регистров). 3) Информация об организации памяти (способы адресации памяти и ёмкости). 4) Описание организации процедур ввода – вывода. Существует 2 типа архитектур 1) Фоннеймановская, особенностью, которой является то, что программы и данные находятся в общей памяти, доступ к которой осуществляется по одной шине. 2) Гарвардская, особенность заключается в том, что память данных и память программ разделены и имеют одну шину данных и одну шину команд, что повышает быстродействие микропроцессора. Процессор – это основная часть, компьютера, которая интерпретирует и выполняет команды, т.е реализует процесс обработки данных. Процессор, который выполняет в вычислительной системе основные функции наз. Центральным (ЦП). Специализированный процессор, который предназначенный для управления внешнего устройство называется контролером. Процессор состоит из устройства управления (УУ), арифметика – логического устройства (АЛУ) и блока интерфейса (для объединения с внешней средой). Внешняя среда – память и периферийное устройство.

АЛУ имеет универсальный двоичный комбинационный сумматор, регистр для временного хранения двух операндов (данные, числа) и результата операции, а также флаговый регистр. В РЗУ (регистра – запоминающее устройство) хранятся начальные результаты, адресат данных, константы, которые необходимы в процессе выполнения команд. УУ – последовательно считывает коды команд с памяти и размещает его регистры команд. БУ (блок управления) – существуют аппаратные микропрограммные и комбинированные. Аппаратные построены на основе схемной логики. Микропрограммные – программной логики. Комбинированные – используют оба способа. Интерфейс – это совокупность шин сигналов, вспомогательных микросхем и алгоритмов, предназначенных для обмена информации между устройствами (блоками).

Лекция №2 Принципы построение МПС. Память.

В основу МПС положено 3 принципа: 1) Принцип магистральности – определяет характер связей между функциональными блоками МПС. 2) Принцип модульности – состоит в том, что система строится на основе ограниченного количества типов конструктивно и функционально законченных модулей. В каждый момент времени к системной шине МПС подсоединено лиш 2 модуля передаючих и принимающий информацию 3) Принцип микропрограмного управления – состоит в возможности осуществления элементарных операций - микрокоманд (команды сдвига, пересылок информации и логических операций).

Память. Постоянно – запоминающее устройство (ПЗУ) и оперативное запоминающее устройство (ОЗУ) образуют систему памяти, предназначения информации в виде двоичных чисел. ПЗУ предназначено для хранения программ управления, констант, таблиц; ОЗУ – для хранения промежуточных результатов вычисления. Для (вр) обращения к ячейки памяти необходимо выдать её адрес на ША. Память состоит из 4 – х типов сегментов по 64 кбайта каждый (не более). ОЗУ включает в себя первые три четверти памяти, а ПЗУ – ¼ - последнюю часть. Все ячейки памяти пронумерованы последовательно от 000 до 111. Структура памяти из восьми однобайтных ячеек.

000 5F(16) Адресация: Процессор обеспечивает доступ к байтам или словам памяти. Рассмотрим 1025(10) Для записи в память необходимо число представить в 16 – ричную систему счисления. 210 2 9 28 27 26 25 24 23 22 21 20 1024 512 256 128 64 32 16 8 4 2 1 0 1 0 1 0 0 0 0 0 0 0 1 (2) 0401(16) Для этого потребуется 2 байта или 1 слово. Старшая часть – 04 Младшая часть – 01 Данные в памяти хранятся в обратной последовательности: Младая часть – по меньшему адресу, старшая – по большему.

Сегмент – область памяти которая начинается с любого адреса, красного 16. Существуют 4 основных сегмента: 1) Сегмент кодов – содержит коды команд, которые будут выполняться сегментным регистром кодов (СS) и указателем команд (IP). Регистр CS определяет начальный адрес сегмента кодов, а регистр IP – смещение в сегменте (расстояние от начала сегмента до ячейки, в которой находится адрес команды). 2) Сегмент данных. 3) Стековый сегмент.

Лекция №3 Однокристальные МП восьмиразрядные i8080. Структурная (система) схема.

Структурная схема содержит: Устройство управления (УУ) – генерирует управляющие сигналы для всех облаков схемы. Дешифратор команд (ДШК) – формирует сигналы для УУ. Регистр команд (РК) – содержит машинный код команды (8 разрядов). АЛУ – выполнят арифметика – логические операции над двоичными числами. Аккумулятор (А) – представляет собой восьмиразрядный регистр, в котором хранится один из операндов, а также результат операции. Временный аккумулятор (ВА) и временный регистр (ВР) – буферные восьмиразрядные регистры. Регистр флагов представляет собой 5 или 6 триггеров, которые устанавливаются в единичное или нулевое состояние в зависимости от результата операции, выполненного в АЛУ.

S – знак Z – ноль АС – вспомогательный дополнительный перенос Р – паритет точности С – перенос Мультиплексор (М) – соединяет РОН с системной шиной. Регистры общего назначения (РОН) – всего 6 штук: A, B. C, D, E, K, H, L. В них хранятся данные и промежуточные результаты. Указатель стека (SP) – 16 – разрядный регистр, в котором хранится адрес выполняемой команды. После выборки из памяти программ очередного байта команды содержимое IP увеличится на 1. Схема инкремента/ декремента (СИД) – позволяет без участи АЛУ увеличить или уменьшить на единицу содержимое регистра IP, SP, или РОН. БА – буферный регистр адреса БД – буферный регистр данных Схема работает следующим образом: При включении питания или при формировании сигнала КУІУЕ содержимое IP устанавливается в 0 и начинается машинный цикл выборки команды из памяти. Содержимое ячейки памяти по нулевому адресу через буферный регистр данных и внутреннюю шину микропроцессора поступает в PK, а затем в ДШК. Этот сигнал вместе с сигналом синхронизации формируют управляющие импульсы для каждой микрооперации.

Лекция №4 Программная модель МП I8080 Пр. модель – совокупность программно – доступных регистров, т.е. тех регистров, содержимое которых можно прочитать или изменить с помощью команд. В пр. мод входит: аккумулятор, РОН, регистр флагов (F), указатель стека (SP) и указатель команд (IP).

Функциональные возможности регистров BC DE одинаковы. Особенность I8080 в том, что РОН объединяют в регистровые пары. Пара HL – это регистр памяти МП. Пары BC и DE используются для косвенной адресации памяти. В команде указываются регистр или пара содержащая адрес ячейки памяти. Указатель команд или программный счетчик предназначен для хранения адреса ячейки памяти, которая содержит код следующей команды. Программа действий МП записана в памяти в виде последовательности кодов команд. Для перехода к следующей команде содержимое счетчика увеличивается на единицу в момент выборки команды из памяти. Таким образом, в конце выполнения команды в счетчике команд хранится адрес следующей команды. Указатель стека – это регистр, который хранит адрес последней занятой ячейки стека. Стеком или стековой памятью наз. область памяти, которая организована по принципу «последним пришел – первым вышел». Каждая команда выполняется на протяжении командного цикла, который состоит из: цикла выборки команды и цикла выполнения команды.

Интервал, на протяжении которого осуществляется одно обращение к памяти или к внешнему устройству наз. машинный цикл состоит из нескольких машин. циклов. М.Ц. разбивается на некоторое количество тактов (3 – 5), на протяжении которого выполняется одна микрооперация в процессоре. В зависимости от действий выполняемых МП различают (следующее) 10 М.Ц. 1) Выборка (чтение первого байта команды). 2) Чтение памяти (чтение 2 и 3 байта команды, чтение операнда). 3) Запись в память. 4) Чтение стека. 5) Запись в стек. 6) Ввод данных из внешнего устройства. 7) Вывод данных на внешнее устройства. 8) Прерывание. 9) Отанов. 10) Прерывание при останове.

Каждый МЦ процессора идентифицируется байтом, называемым байтом состояния. Этот байт выдается на ШД в начале каждого МЦ и сопровождается выдачи синхросигнала.

|

=1

=1

=A

(AVB)(AV

=A

(AVB)(AV

по всіх видах операцій

по всіх видах операцій