Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Понятие прерывания. Виды прерываний. Схемы обработки.

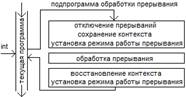

Прерывание – прекращение линейного выполнения задач и принудительная передача управления от выполняемой программы ОС-ме при возникновении какого-либо события. Этапы обработки прерывания: 1) Установление факта прерывания и его идентификация; 2) Запоминание состояния прерванного процесса (аппаратное сохранение); 3) Передача управления в обработчик прерывания; 4) Программное сохранение информации о прерванном процессе; 5) Обработка прерываний; 6) Программное восстановление контекста прерванного процесса; 7) Возврат управления прерванной программе (аппаратное восстановление). Данный механизм обработки прерываний выполняется независимо от архитектуры вычислительной системы и реализуется при помощи аппаратно-программных средств. Прерывания можно разделить на 2 основные группы: 1) Внешние (асинхронные) – возникающие вне МП (прерывания клавиатуры, таймера и других внешних устройств); 2) Внутренние (синхронные) – возникающие внутри МП и являющиеся синхронными с его операциями (деление на 0, нарушение правила адресации и пр.).

Основные функции механизма прерываний: 1) распознавание и классификация прерываний; 2) передача управления обработчику; 3) корректный возврат в прерванную программу. Для быстрого перехода в обработчик прерывания используются таблицы, содержащие перечень всех прерываний и адреса их обработчиков. Для корректного возврата из процедуры обработчика необходимо сохранение контекста задачи в спец. области памяти или системный стек.

Физическая структура микропроцессора

В состав микропроцессора Pentium обычно входят следующие физические компоненты: Core — ядро МП; Execution Unit — исполняющий модуль; Integer ALU — АЛУ для операций с целыми числами (с фиксированной запятой); Registers — регистры; Floating Point Unit — блок для работы с числами с плавающей запятой; Primary Cache — кэш первого уровня, в том числе кэш данных (Data Cache) и кэш команд (Code Cache); Instruction Decode and Prefetch Unit и Branch Predictor - блоки декодирования инструкций, опережающего их исполнения и предсказания ветвлений; Bus Interface — интерфейсные шины, в том числе 64- и 32-битовая, и выход на системную шину к оперативной памяти. Функционально МП можно разделить на две части: операционную часть, содержащую устройство управления (УУ), арифметико-логическое устройство (АЛУ) и микропроцессорную память (МПП) (за исключением нескольких адресных регистров); интерфейсную часть, содержащую адресные регистры МПП; блок регистров команд — регистры памяти для хранения кодов команд, выполняемых в ближайшие такты; схемы управления шиной и портами. Обе части МП работают параллельно, причем интерфейсная часть опережает операционную, так что выборка очередной команды из памяти (ее запись в блок регистров команд и предварительный анализ) выполняется во время выполнения операционной частью предыдущей команды. Современные микропроцессоры имеют несколько групп регистров в интерфейсной части, работающих с различной степенью опережения, что позволяет выполнять операции в конвейерном режиме. Такая организация МП позволяет существенно повысить его эффективное быстродействие.

32. РЕГИСТРЫ Регистры — это последовательностные устройства, предназначенные для приема, хранения, простых преобразований и передачи двоичных чисел. Под простыми преобразованиями понимаются сдвиг чисел на заданное количество разрядов, а также преобразование последовательностного двоичного кода в парачлельный и параллельного в последовательностный., разовыми элементами регистров являются триггеры, когорые дополняются комбинационными логическими элементами для реализации различных связей между разрядами регистра и управления приемом и передачей операндов. Основное функциональное назначение регистров — оперативная память для многоразрядных двоичных чисел.

В зависимости от способа приема и передачи двоичной информации различают параллельные, последовательные, последовательно-параллельные, параллельно-последовательные и универсальные регистры. В параллельных регистрах или регистрах памяти вывод всех разрядов числа производится одновременно один такт. Для построения -разрядного регистра памяти требуется триггеров. Параллельные регистры служат основным функциональным элементом для построения оперативных запоминающих устройств. В последовательных регистрах ввод/вывод информации осуществляется через один информационный вход и один выход поразрядно со сдвигом числа. Поэтому последовательные регистры называют сдвигающими (или сдвиговыми). За один такт вводимая или выводимая информация сдвигается на один разряд вправо или влево. Сдвигающие регистры, реализующие по команде управления сдвиги информации вправо или влево, называют реверсивными. Последовательно-параллельные регистры имеют один информационный вход для последовательного ввода числа в режиме сдвига и выходные вентили для выдачи -разрядного числа параллельным кодом. Такие регистры выполняют преобразование последовательного кода в параллельный. В параллельно-последовательные регистры информация вводится параллельным кодом за один такт через тактируемые входные вентили, а выводится из них последовательно по одному разряду в каждом тактовом интервале. Тем самым реализуется операция преобразования параллельного кода в последовательный. Универсальные регистры сочетают в себе возможности вышеперечисленных типов регистров и, кроме того, обеспечивают режимы отключения входов и выходов (третье логическое состояние) регистра от общей информационной шины, перекоммутацию местами входов и выходов регистра и тем самым переключение функций прием передача информации в общую информационную шину. Технические параметры регистров определяются параметрами их основного фуикциоиального узла — триггера и разрядностью операнда. Параллельные регистры. При построении параллельных регистров обычно используются простейшие асинхронные -триггеры и синхронные RS- и На рис. 6.22 представлены варианты параллельных регистров, отличающиеся типом триггеров и составом входных выходных информационных. Регистр на основе асинхронных -триггеров (рис.) перед занесением очередного -разрядного числа входов требует предварительного сброса всех триггеров в нулевое состояние. Сброс производится сигналом. Ввод информации в регистр происходит по сигналу. . Если на некотором входе, то н данный триггер (с инверсным управлением) переключается в состояние «1». Если на входе то триггер, сохраняет состояние. Вывод информации из регистра производится по сигналу, определяющему состояния выходов. Если, то на всех выходах устанавливаются уровни «логической 1», а при имеем. Основной недостаток данного регистра — необходимость предварительной очистки регистра, из-за чего обновление информации осуществляется за два такта. В регистре также на основе асинхронных -триггеров предварительная очистка не требуется, поскольку обновление информации в нем происходят установкой триггеров состояние "1" и «0» за один такт.

Для этого на входе регистра требуется вдвое больше логических элементов и лнний связи. В схеме показан способ выдачи информации в прямом коде (команда и/или в обратном коде (команда. Асинхронные -триггеры в сочетании со входными вентилями (рис. 6.22,а, в) но существу образуют варианты синхронных -триггеров. На рис. 6.22,в показана схема параллельного регистра на основе синхронных -триггеров. Здесь в качестве входных используются логические элементы, входящие в схему -триггеров. Ввод информации происходит на интервале синхронизации при.

Рис. 6.22. В качестве выходных использованы логические элементы И—ИЛИ—НЕ, которые формируют выходные сигналы согласно выражению

т. е. при информация из регистра выдается в прямом коде, а при — в обратном. Если выражение (6.16) тождественно преобразовать к одной из форм

то выходную цепь регистра (рис. 6.22,в) можно реализовать на логических элементах ИСКЛЮЧАЮЩЕЕ ИЛИ (рис. 6.22,г). Выбор способа ввода информации в регистр или ее вывода обычно обусловлен требованиями быстродействия и условиями реализации регистра в цифровом устройстве. Сдвигающие регистры. Рассмотрим последовательные, последовательно-параллельные и параллельно-последовательные регистры, которые должны выполнять операцию сдвига при последовательном вводе и/или выводе информации. Сдвиг числа реализуется перезаписью состояний между соседними триггерами регистра в направлении сдвига. Таким образом, каждый разряд регистра одновременно принимает информацию из предыдущего разряда и передает информацию в последующий. Во избежание явления гонок эти процессы должны быть разделены во времени. Это достигается включением элементов линий задержек в связи между разрядами либо использованием двухтактных триггеров. В интегральной схемотехнике статические сдвигаюющие регистры строятся преимущественно на двухтактных D- и -триггерах. При однонаправленном сдвиге информации достаточно реализовать непосредственные связи между выходами предыдущего и входами последующего триггера -типа (рис. 6.23,а, б). В сдвигающем регистре на -триггерах (рис.) для передачи информации между разрядами требуется связь между, а в случае использования -триггеров (рис.) — двойные связи;.

Рис. 6.23. В остальном структуры, принцип работы и параметры данных регистров аналогичны. Ввод информации может производиться последовательно со входа X с последующим сдвигом информации вправо на один разряд по каждому синхроимпульсу С либо параллельно со входов А по сигналу асинхронной записи числа в предварительно очищенный региар (сигналом асинхронного сброса триггеров в состояние) По положительному фронту синхроимпульса происходит запись информации со входов D и X в триггеры первых ступеней М. Выходные уровни триггеров при этом остаются неизменными (см. рис. 6.23,в). По отрицательному фронту синхроимпульса входы ступени М блокируются и записанная в них информация передается в триггеры ступени S. Происходит переключение выгодных уровней -трнггеров. Таким образом, реализуется чисто последовательный регистр со сдвигом числа вправо (показано стрелкой на рис. 6.23,в, вход — X, выход —), последовательно-параллельный (вход — X, выходы —) и параллельно-последовательный (входы —, выход —). Кроме того, при замыкании выхода последнего разряда с последовательным входом X (штриховая линия) реализуется кольцевой сдвигающий регистр. Информация в кольцевой регистр вводится параллельным кодом со входов и затей циркулирует в замкнутом кольце под действием тактовых синхроимпульсов С. Кольцевые регистры удобно использовать для построения, например, тактовых генераторов цифровых устройств. В реверсивных сдвигающих регистрах для обеспечения возможности сдвига информации в обоих направлениях выход каждого разряда должен быть связан через логические элементы переключения направления сдвига со входами предыдущего и последующего разрядов. Пусть направление сдвига задается логическим уровнем сигнала Е так, что при осуществляется сдвиг вправо., а при происходит сдвиг влево;. Тогда триггер реверсивного сдвигающего регистра должен управляться сигналом который формируется логическим элементом И—ИЛИ—НЕ (рис. 6.24, а) либо на логических элементах.

Рис. 6.24. Для сигнала в соотношении (6.17) используется сигнал последовательного входа при сдвиге вправо или при построении кольцевого сдвигающего вправо регистра. Аналогично, в качестве сигнала используется последовательный вход У при сдвиге влево или, для кольцевого сдвигающего влево регистра. На рис. 6.24, б показан тождественный согласно выражению (6.17) вариант схемы управления разрядом реверсивного сдаигающего регистра. На рис. 6.25 показан вариант реверсивного сдвигающего регистра на основе -триггеров. Сигнал на входах определяется аналогично согласно выражению (6.17), а на выходах всегда благодаря инверторам во входных цепях. Параллельный ввод информации в асинхронном режиме в сдвигающие регистры возможен, например, через несинхронизируемые входы R и S. Синхронный параллельный ввод реализуется через систему логических элементов управления сдвигом. Так как в данном случае предусматриваются состояния регистра (параллельный ввод, сдвиг вправо, сдвиг влево), одного двоичного управляющего сигнала Е уже недостаточно для управления ими. Пусть два управляющих режимом работы сигнала кодируют состояние регистра в соответствии с табл. 6.4.

Тогда входы D и С разряда определяются следующими логическими уравнениями:

Рис. 6.25. Соответствующий сдвигающий регистр на основе -триггеров показан на рис. 6.26. Здесь — входы параллельного ввода информации, X — последовательный вход для сдвига вправо, Y — последовательный вход для сдвига влево. Динамические регистры — регистры, для которых определена верхняя граница временного интервала хранения информации без восстановления. Чаще всего в них физическим носителем информации является заряд некоторой емкости или зарядовый пакет в объеме полупроводника [4; 14]. Для управления зарядом используют МДП-транзисторы, обладающие весьма большим сопротивлением в запертом состоянии Ом). Используя логические элементы на МДП-транзисторах, можно по заданному алгоритму управлять зарядом и напряжением на некоторой паразитной емкости. На рис. показана схема -тактного динамического регистра на -МДП-транзисторах, каждый разряд которого выполнен на шести транзисторах. Каждый разряд содержит два тактируемых ключа на транзисторах соответственно — эквивалентные входные емкости ключей. Пусть на вход разряда поступает от разряда логический сигнал, которому соответствует электрический сигнал, и все остальйые емкости разряжены. Таблица 6.4

|

|||||||||

|

Последнее изменение этой страницы: 2016-08-16; просмотров: 3346; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.221.85.33 (0.037 с.) |

Зачастую прерывания можно использовать для обращения к супервизору ОС (21h). Однако такая схема используется только в самых простых программных средах. В современных ОСр управление супервизором происходит по другим схемам.

Зачастую прерывания можно использовать для обращения к супервизору ОС (21h). Однако такая схема используется только в самых простых программных средах. В современных ОСр управление супервизором происходит по другим схемам.