Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Аппаратные и программные прерывания. Внутренние и внешние прерывания.Содержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

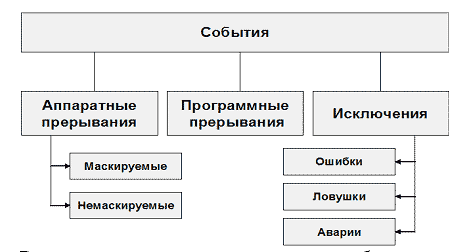

Прерывание (interrupt) — сигнал, сообщающий процессору о наступлении какого-либо события. При этом выполнение текущей последовательности команд приостанавливается, и управление передаётся обработчику прерывания, который реагирует на событие и обслуживает его, после чего возвращает управление в прерванный код. В зависимости от источника возникновения сигнала, прерывания делятся на:

Аппаратные прерывания делятся на:

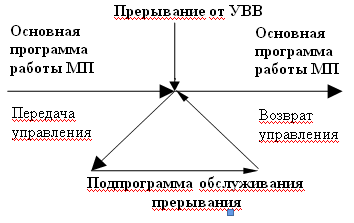

Ввод-вывод по прерываниям подразумевает, что действия по обмену информацией инициируют сами периферийные устройства, генерируя сигнал прерывания. При восприятии сигнала прерывания микропроцессор приостанавливает выполнение текущей программы, временно запоминает ее состояние (как минимум, запоминается содержание PSW, РС) идентифицирует прерывающее устройство и осуществляет обмен информацией. После завершения обмена восстанавливается состояние прерванной программы и возобновляется ее выполнение. В данном режиме на ввод-вывод расходуется гораздо меньше времени микропроцессора, чем в программно-управляемом ВВ, поэтому система может выполнить больше полезной работы или обслужить больше периферийных устройств.

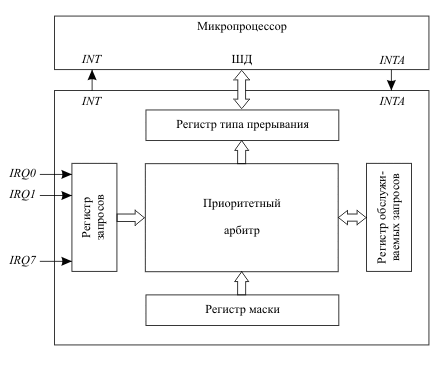

Ввод-вывод по прерываниям, однако, требует усложнения аппаратных средств – создания системы прерываний. Структура контроллера приоритетных прерываний имеет вид

Обозначения:

При поступлении запроса на прерывание IR(N) от периферийного устройства (ПУ) контроллер прерываний посылает запрос на прерывание (INT) в центральный процессор. Процессор разрешает обработку прерывания, формируя сигнал подтверждения #INTA, который, поступая в контроллер прерываний, вызывает формирование на шине данных вектора прерывания. Вектор определяют программу обработки. Обработка прерывания произойдет после завершения выполнения текущей команды процессором. Контроллер прерываний позволяет управлять прерываниями от устройств, разрешая или запрещая некоторые из них (путем маскирования), а так же позволяет менять приоритеты. Режим работы контроллера управляется процессором через шину контроля. 8. (!)Одноуровневая система прерывания. Аппаратное и программное обеспечение. Основным недостатком программно-управляемого ввода-вывода является нерациональное использование машинного времени микропроцессора. Оно, в основном, тратится на циклы ожидания изменений во входном коде при поддержке портов безусловного ввода или на циклы ожидания готовности порта при поддержке портов условного ввода-вывода. Число циклов ожидания может быть очень большим из-за низкой скорости работы большинства внешних устройств. Полностью исключить циклы ожидания и связанные с ними потери машинного времени позволяет ввод-вывод по прерываниям. Порты, использующие этот вид обмена, не имеют средств для пересылки в микропроцессор сигнала готовности по шине данных. На основе сигналов готовности они формируют запросы на обслуживание IRQ. Функциональная схема включения таких портов в микропроцессорную систему с учебным микропроцессором представлена на рис.4.17. Эта схема реализует так называемую одноуровневую векторную систему прерываний. Она включает в себя порты 1…N, реализующие асинхронный ввод-вывод на внешнем участке обмена, элемент «ИЛИ», приоритетный шифратор и порт ввода вектора прерывания. Пусть в исходном состоянии все запросы на обслуживания IRQ1…IRQN равны нулю, то есть отсутствуют. Пусть далее появляется запрос от порта ввода No1 IRQ = 1. Этот запрос через элемент «ИЛИ» передается на вход запроса прерываний INT процессора. Процессор, реагируя на этот запрос, выполняет следующие действия:

Рис.4.17.Функциональная схема одноуровневой векторной системы прерываний Рис.4.18.Типовая блок-схема программы обслуживания прерывания Каждый из портов этой системы имеет свою собственную программу обслуживания порта, вызываемую одной из команд вида RST X. Конкретный вариант команды рестарта называют вектором соответствующего прерывания. Вектор формируется приоритетным шифратором из запросов IRQ1… IRQN и выставляется на шину данных по сигналу Программа обслуживания прерывания в одноуровневой векторной системе обычно строится по типовой блок-схеме (рис.4.18). При практическом использовании прерываний следует иметь в виду особенность исполнения команды разрешения прерываний EI. Она исполняется не в момент получения ее микропроцессором, а лишь после выполнения следующей команды. В нашем случае это означает, что прерывания вновь будут разрешены лишь после возврата в основную программу. В одноуровневой системе все запросы на прерывания практически равнозначны. Приоритет сказывается лишь при одновременности поступления запросов. Иногда удобнее иметь многоуровневую систему прерываний, в которой запросы с более высоким приоритетом могут прерывать работу программ обработки прерываний, имеющих низшие приоритеты. Векторную многоуровневую систему прерываний реализуют с помощью специализированной БИС – контроллера приоритетных прерываний. Следует отметить, что ввод-вывод по прерываниям, в конечном итоге, также обеспечивает асинхронную передачу кодов на внутреннем участке обмена. Роль недостающего сигнала асинхронного протокола (STB) или (ACK) здесь выполняет сформированный системой вектор прерывания.

9. (!)Многоуровневая система прерывания. Аппаратное и программное обеспечение. В многоуровневых системах прерываний подпрограмма обслуживания прерывания более низкого уровня может быть прервана подпрограммой обслуживания прерывания более высокого уровня. Иными словами, реализуется режим прерывания во время прерывания. Структура таблицы векторов прерываний:

Обращение к элементам таблицы осуществляется по 8-разрядному коду - типу прерывания

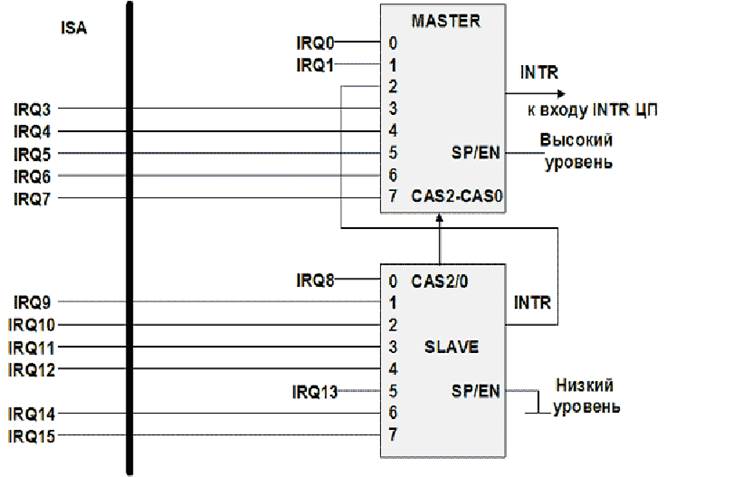

Однако несколько контроллеров прерываний могут быть включены последовательно. На современных компьютерах (начиная с 286) один (ведущий) контроллер прерываний подключен непосредственно к процессору, а второй (ведомый) своим выходом INT подключен ко входу IRQ2 ведущего контроллера. Итого получается 15 входов прерываний от IRQ0 до IRQ 15 (IRQ2 не может быть использован). При подаче сигнала на прерывание от контроллера к процессору по линии INTR-INT, одновременно по линиям данных из контроллера прерываний в процессор поступает номер вектора прерывания, который образуется путем сложения IRQ с некоторым базовым номером, который присваивается ВIOSом контроллеру в процессе загрузки (значения по умолчанию 08h для ведущего контроллера и 70h для ведомого). Таким образом, например, номер вектора прерывания для клавиатуры будет 08+1=9 h, для жесткого диска 70 h +6=76 h. Контроллер прерываний допускает перепрограммирование для установки различных режимов формирования очереди запросов, изменения приоритетов прерываний, изменения базовых номеров контроллеров. Такое перепрограммирование осуществляется через два байтовых порта 20 h и 21 h. По умолчанию IRQ отдельного контроллера имеют приоритеты в соответствии с их номерами (IRQ0 – наивысший, IRQ7 – наинизший). Пример каскадного включения двух контроллеров прямого доступа к памяти

|

||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 1857; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.191.68.112 (0.007 с.) |

. Использование приоритетного шифратора позволяет обслуживать одновременно поступившие запросы от разных портов в соответствии с заранее определенной системой приоритетов.

. Использование приоритетного шифратора позволяет обслуживать одновременно поступившие запросы от разных портов в соответствии с заранее определенной системой приоритетов.