Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Синтез комбінаційної схеми, реализуючої функції збудження тригера БФРСодержание книги

Поиск на нашем сайте

Як випливає зі структурної схеми одного розряду регістра (рис. 5), комбінаційна схема, що реалізує функції збудження (одну або дві), містить (q+1)-у схему обчислювачів і схему коммутатора, і, таким чином, синтез вхідної КС (КС1 на рис. 3) зводиться до синтезу окремих схем обчислювачів для кожного розряду регістра, а також загального для них комутатора. Для синтезу КС, реализуючої функцію порушення тригера виду, необхідно мати у своєму розпорядженні наступну інформацію: - опис МО, тобто вид вираження Fг. р = 1,q, в операторі присвоювання Q(t+1):= Fr(A1,A2…..Аk,Q(t)) (5) де Q - однобітова змінна з пам'яттю, що відбивала стан на виході даного тригера: - элементна база (тип тригера, логічний базис, конкретне значення коефіцієнтів навантажень по вході і по виходу і т.п.).- Далі складається таблиця виду табл. 2, стовпчики в який можна розділити на 3 групи: -з іменем вхідних змінних А1..,, Ак (їхні розряди не обов'язково збігаються і не обов'язково є присутнім усі змінні), а також змінні Q(t). Що поступили на входи чисельника в момент t: - з ім'ям змінної Q(t+1), значення котрої, відповідно до конкретного вираження для Ег, буде замінено даним тригером у момент t+1: -з іменами перемінним (функцій збудження), відповідні інформаційним входам тригера.

Таблиця 2

Заповнюється табл. 2 у такий спосіб. Перша група стовпчиків заповнюється построчно у виді послідовних значень двоічного коду, починаючи зі значення 00...0 закінчуючи значенням 11….1, перебираючи в такий спосіб усі можливі комбінаційні значення вхідних перемінних (включаючи Q(t)). Потім для кожної комбінації вхідних перемінних є значення Q(t+1) і заповнюється стовпчик з ім'ям Q(t+1). Після цього можна перейти до заповнення останньої групи стовпчиків: зіставляємо построчно значення Q(t) і Q(t+1) до враховуємо обернену таблицю переходів (табл. 2) для дfнного тригера, тобто тут проставляоємо такі значення функцій порушення, що забезпечують перехід Q(t) –Q(t+1). Тепер можна перейти до синтезу комбінаційної схеми р- го обчислювача 1-го розряду регістра. Синтез здійснюється відомими засобами, причому вхідні перемінні - це Аі - Ак і Q(t)), а вихідні – функції збудження тригера.

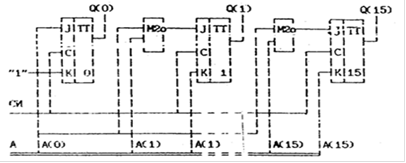

Приклад. Нехай треба побудувати фрагмент БФР на JK-тригері МS-типа, здійснюювачого мікрооперації У4. Yg:Pr(0:15):=ЯКЩО А(0) ТО (А(0:15) + Рr(0:15)) Множина розрядів регістра розіб'ємо на два сегменти: <0> і <1:15>. Синтезуємо схему окрема для нулевого і 1-го розрядів регістра (і=1.15). Для цього складемо табл 3 і 4 використовуючи правила заповнення (див. вище), причому замість перемінної 0 запишемо Рr(1) (1- номер). Останні дві колонки в табл. 3 і 4 заповнені в відповідності з оберненою таблицею переходів тригера JК-типа (табл.1). Тут Функціями збудження є перемінні J та К. сигнали яких діють на входах тригера в момент t до надходження сінхроімпульсу на регістр. Отримані табл.3 і 4 - це таблиці істинності для КС, що реалізують функції порушення тригерів нульового і 1-го розрядів регістра. Мінімізуя спільно функції J та K для кожного розряду, одержимо (і=1,15):

Таблиця 3

Таблиця 4

СИНТЕЗ ШИНИ ТА КОМУТАТОРА Шина - це пристрій, що подає собою сукупності ліній зв'язку і комбінаційної схеми, що формує визначені значення сигналів, що діє на цих лініях, під керуванням тієї або інший МО. Шина інтепретує перемінну без пам'яті В, яка у загальному випадку описуються в такий спосіб:

У1: В:= Ф (А1, А2…. Ак, R) (7) де А1. А2, Ак - вхідні для БФР перемінні; R – вихідна перемінна з пам'яттю, що інтерпретується регістром, значення якої не змінюється протягом такту, коли діє МО у1: Ф - Функція, що Формує значення розрядів змінної для передачі їх у зовнішню щодо даного БФР середовище. Відзначимо розходження вхідних і вихідних перемінних без пам'яті: перші є зовнішніми щодо даного БФР і тому ' при його побудові інтепретуються тільки лініями зв'язку, а другі є внутрішніми для БФР і інтепретуються шиною.

МО у1 входить у підмножину У2, що визначає роботу КС2 (рис.3). Очевидно, структура КС2 подібна структурі КС1 поданої на рис.5 одним розрядом: КС2 також складається із обчислювачів (Фа+1…..Фм) і комутатора, керованого сигналами Уа+1...Ум. Відмінність КС2 від КС1 визначаються відсутністю залежності перемінної У від її значень у попередній момент часу. КС2 не має особливостей КС1, тобто вузла пам'яті і додаткового обчислювача: у тої ж час варто мати на увазі, що при роботі БФР на магістраль на виході КС2 необхідно застосувати буферний каскад. При синтезі КС2 у загальному випадку також необхідна сегментація, але вже щодо розрядності перемінної В. Синтез КС2 декілька відрізняться від. синтезу КС1, що визначається розходженням вихідних перемінних цих схем: крім того, результат перетворення вхідних перемінних у КС1 виявляється на слідуючем такті, а в КС2 - у даному такті. Відповідно до цього і заповнюється табл. 5. Відзначимо тільки, що стовпчик "В" заповнюється построчно значеннями, обчисленими по (7) для представника j-го сегмента (деякого i-го розряду) для даної МО иэ підмножини У2: Відмітемо також, що номера розрядів для вхідних перемінних А не обов'язково збігаються з i-м. Аналогічно (6) можуть бути описані КС обчислювачів, що вироблюють функції порушення Fі. і для інших МО.

Рис.6. Фрагмент схеми обчислювача

Для реалізації КС обчислювачів може бути використаний досить широкий арсенал засобів [2-7]: найпростійші логічні элементи I-НІ (АБО-НІ), мультіплексори (МП), дешифратори (ДШ), арифметико-логічні пристрої (АЛП), логічні матриці, що програмуються (ПЛМ), постійні пристрої, що запам'ятовують (ПЗУ), причому ДШ, ПЛМ, ПЗУ дозволяють реалізувати систему рівнянь виду (6) тобто будувати декілька обчислювачів. Об'єднання функцій збудження здійснюється відповідно до формул виду (2) для тригера з одним інформаційним входом, або виду (2) та (.3) - для тригера з двома інформаційними входами. Фізично ці формули реалізуються відповідно одною або двома схемами І-АБО: конкретна реалізація схеми визначається її складністю і заданим критерієм оптимальності. Таким чином проводиться синтез обчислювачів для КС1, що відносно коммунікатора для КС1, то його синтез проводиться так. Таблиця 5

Очевидно, табл. 5 являє собою таблицю істинності, і подальший синтез по ній здійснюється звичайними засобами [2-7]. Аналогічно заповнюються таблиці і для інших МО з У2 і синтезуються відповідні обчислювачі 1-го розряду. Потім ці рішення тиражуются на всі розряди.3--го сегмента. Роздивимося синтез комутатора. Вище було відзначено, що обидві комбінаційні схеми, КС1 і КС2, мають у своєму складі комутатор. Комутатор реалізує логічну функцію І-АБО, причому Функція І дозволяє вибрати одну з множини вихідних перемінних обчислювачів, а АБО - об'єднати результати вибору. Технічна реалізація функції І-АБО може бути здійснена декількома засобами: - за допомогою мультиплексора; - на двох'ярусній схемі І - НІ: - на схемах І (І-НІ) із відкритим колектором: - на схемах І (І-НІ) із трьома станами. Перші два засоби припускають явну реалізацію комутатора, причому на мультиплексор (на його адресні входи) повинні надходити сигнали МО в двоїчно кодованому виді.. При третьому і четвертому засобах комутатор реалізується неявно - він "убудовується" в обчислювач, що досягається введенням у схему обчислювача керуючого сигналу (МО у1) і монтажним об'єднанням виходів обчислювачів. При третьому засобі сигнал, що управляв, у1 вводиться в елементи І-НІ першого ярусу обчислювача, а елементи І-НІ другого ярусу схем обчислювачів є схемами з відкритим колектором. При четвертому засобі сигнал У1 управляє станом "Включений /Виключений" елементів І-НІ другого ярусу схем обчислювачів. Відзначимо, що в більшості випадків вхід керування станом елемента є інверсним.

У випадку невеличкого числа простих. обчислювачів можливо ще більше спрощення схем КС1 - монтажне об'єднання виходів елементів першого ярусу усередині обчислювачів із подальшим монтажем об'єднанням виходів обчислювачів.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-07-11; просмотров: 60; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.144.11.146 (0.007 с.) |