Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Блоки, необхідні для реалізації 1-го завдання на up-2Содержание книги

Поиск на нашем сайте

В роботі вам доведеться використовувати кнопку на UP-2 для створення тактового сигналу clk. В цих кнопках можливе тремтіння контактів (дребезг контактов), коли при однократному натисненні генерується кілька імпульсів і відповідно кілька передніх фронтів, що приводить до повторних спрацьовувань пристроїв синхронних по фронту. Для усунення такого явища можна використовувати блок debounce, який долучено до завдань. Підключення блоку debounce:

Сигнал синхронізації для модуля debounce можна взяти з блоку подільника частоти clk_div, який також додається до завдань. На вхід clk блоку clk_div подається сигнал частотою 25 МГц з входу FPGA. На вхід pb блоку debounce підключається кнопка. Значення кнопки без тремтіння контактів береться з виходу pb_debounced. Для використання блоків в проекті необхідно скопіювати їх файли в каталог проекту. Теоретичний матеріал Теоретичний матеріал до виконання лабораторної роботи викладено в відео лекціях, які можна переглянути за адресами: http://vk.com/video-67410598_170435832 http://vk.com/video-67410598_170435836 http://vk.com/video-67410598_170435842 http://vk.com/video-67410598_170435849 http://vk.com/video-67410598_170435854 http://vk.com/video-67410598_170435867 http://vk.com/video-67410598_170435872 http://vk.com/video-67410598_170435876 http://vk.com/video-67410598_170435883 http://vk.com/video-67410598_170435885 http://vk.com/video-67410598_170435891

Слайди лекцій доступні за адресами: http://vk.cc/34wwOm http://vk.cc/34wxb3 http://vk.cc/34wxtV http://vk.cc/34wxHa http://vk.cc/34wy55 Завдання на лабораторну роботу

Завдання 1. Варіант 0. Створіть 4-розрядний, синхронний по фронту, паралельний регістр з можливістю граничного сканування (boundary scan). У якості тригерів можна використовувати синхронні по фронту D-тригери з Quartus II. Регістр повинен мати 4-розрядну шину вхідних даних (data_in), 4-розрядну шину вихідних даних (data_out), вхід сканування (scan_in), вихід сканування (scan_out), вхід дозволу сканування (scan_enable), вхід синхронізації clk. Якщо scan_enable=0, пристрій повинен працювати, як звичайний паралельний регістр. Якщо scan_enable=1, пристрій переходить в режим сканування, тобто перетворюється на регістр зсуву, в який можна у послідовному режимі (один біт за такт) завантажувати дані через вхід scan_in і зчитувати дані через вихід scan_out. Створіть в Quartus II мегафункцію перемножувача (LPM_MULT) двох 4-бітних чисел з 8-ми розрядним виходом. Підключіть до кожного входу перемножувача створений раніше регістр. Підключіть до виходу перемножувача 8-ми розрядний регістр (створений з двох 4-х розрядних). Виведіть входи scan_in та scan_enable на перемикачі UP-2. Виведіть вхід clk на кнопку UP-2. Виведіть вихід scan_out на один з сегментів індикатора UP-2. Переведіть пристрій в режим граничного сканування. Завантажте числа у вхідні регістри. Переведіть пристрій в нормальний режим роботи і подайте одиничний тактовий імпульс, щоб результат множення записався у вихідний регістр. Знову переведіть пристрій в режим сканування і виведіть побітово вміст вихідного регістру на сегмент індикатора.

Варіант 1. Створіть 6-ти розрядний паралельний регістр з синхронним по фронту завантаженням, для здійснення якого необхідно подати одиницю на вхід дозволу синхронного завантаження we1 та подати тактовий імпульс на вхід clk. Також реалізуйте можливість синхронного по рівню завантаження, яке буду відбуватися по низькому рівню сигналу на вході n_we2. З тригерів можна використовувати лише базові синхронні по фронту тригери з Quartus II, що не мають входу дозволу запису, але мають входи асинхронного зкидання і встановлення. Перевірте функціонування регістру на платі UP-2, вивівши вхідну шину даних регістру на 6 перемикачів плати, входи we1 та n_we2 на 2 перемикачі плати, вхід clk на кнопку плати та вихідну шину даних на сегменти індикатора.

Варіант 2. Створіть синхронний по фронту 5-ти розрядний регістр зсуву з можливістю синхронного по фронту паралельного завантаження та можливістю вибору напрямку зсуву. Регістр повинен мати вхід синхронізації clk, 5-ти розрядну шину вхідних даних (data_in), 5-ти розрядну шину вихідних даних (data_out), вхід дозволу паралельного завантаження (we), вхід вибору напрямку зсуву вправо-вліво (dir), вхід послідовного завантаження даних s_in. Якщо дані зсуваються в сторону старших розрядів, дані з входу s_in записуються в молодший розряд. Якщо дані зсуваються в сторону молодших розрядів, дані з входу s_in записуються в старший розряд. З тригерів можна використовувати лише базові синхронні по фронту тригери з Quartus II, що не мають входу дозволу запису. Перевірте роботу регістру на платі UP-2, вивівши вхідну шину даних на кнопки плати, входи we, dir та s_in на перемикачі плати, вхід clk на кнопку плати та вихідну шину на сегменти індикатора плати.

Варіант 3. Створіть 5-ти розрядний регістр зсуву з можливістю синхронного по рівню паралельного завантаження та можливістю вибору напрямку зсуву. Регістр повинен мати вхід синхронізації зсуву clk, 5-ти розрядну шину вхідних даних (data_in), 5-ти розрядну шину вихідних даних (data_out), вхід дозволу синхронного по рівню паралельного завантаження (we), вхід вибору напрямку зсуву вправо-вліво (dir), вхід послідовного завантаження даних s_in. Якщо дані зсуваються в сторону старших розрядів, дані з входу s_in записуються в молодший розряд. Якщо дані зсуваються в сторону молодших розрядів, дані з входу s_in записуються в старший розряд. З тригерів можна використовувати лише базові синхронні по фронту тригери з Quartus II, що не мають входу дозволу запису, але мають входи асинхронного зкидання і встановлення. Перевірте роботу регістру на платі UP-2, вивівши вхідну шину даних на кнопки плати, входи we, dir та s_in на перемикачі плати, вхід clk на кнопку плати та вихідну шину даних на сегменти індикатора плати. Варіант 4. Реалізуйте передачу даних по послідовному каналу. Приблизна схема:

Створіть 8-розрядний регістр зсуву з паралельним завантаження по низькому рівню сигналу n_we. Створіть ще один 8-розрядний регістр зсуву. Підключіть вихід старшого розряду першого регістру до входу послідовного завантаження другого регістру. Сполучіть входи синхронізації обох регістрів. Щоб гарантувати, що затримка на лінії даних більша ніж затримка на лінії синхронізації, можна використати два послідовного ввімкнених інвертора на лінії даних (як зображено на рисунку), або налаштувати констрейни синтезу. Думаю для вас більш зручний буде перший варіант. Перевірте роботу пристрою на платі UP-2. Підключіть вхідну шину даних першого регістру до перемикачів плати, вихідну шину даних другого регістру до сегментів індикатора плати, Вхід дозволу завантаження даних першого регістру і спільний вхід синхронізації підключіть до кнопок плати. Виставте слово даних на перемикачах, завантажте його в перший регістр. Подайте 8 тактових імпульсів. За показами індикатора переконайтесь, що вміст першого регістру переписався у другий регістр.

Варіант 5. Створіть формувач імпульсу, тривалість якого задається 3-х розрядним цифровим кодом. Приблизна схема:

Регістр зсуву створіть на базі синхронних по фронту тригерів Quartus II. Мультиплексом можете синтезувати, як мегафункцію. На вхід синхронізації подайте частоту 1 Гц, яку можна отримати шляхом ділення частоти 25 МГц, що подається на один з входів FPGA за допомогою блоку CLK_DIV, який додається до завдань. Перевірте функціонування пристрою на платі UP-2, підключивши 3-х розрядну шину коду, що задає тривалість імпульсу до перемикачів плати, підключивши вхід запуску імпульсу до кнопки плати, а вихід на якому формується імпульс до сегмента індикатора плати. Тривалість імпульсу в секундах можете контролювати візуально за допомогою годинника (або за допомогою осцилографа, що знаходиться в 201, 327, або 339 ауд).

Варіант 6. Створіть схему конвеєрного перемножувала чотирьох 4-розрядних чисел. Структурна схема:

Для реалізації перемножувала 4-х чисел на базі двохвходових перемножувачів необхідно послідовно ввімкнути 3 таких перемножувала. Конвеєрна реалізація дозволить збільшити максимальну частоту роботи приблизно вдвічі. Перемножувачі можете створити, як мегафункцію Quartus II. Паралельні регістри необхідно створювати на базі синхронних по фронту тригерів Quartus II. Перевірте роботу приладу в симуляторі Quartus II. Реалізуйте схему перемножувача чотирьох 4-х розрядних чисел без конвеєра у вигляді послідовного з’єднання 3-х перемножувачів (з регістрами на входах і виході приладу). Синтезуйте обидві схеми в Quartus II. За допомогою Timing Analyzer Classic переконайтесь, що максимальна робоча частота конвеєрної версії вища.

Завдання 2. Спільне для всіх варіантів. Створити регістровий файл процесору MIPS:

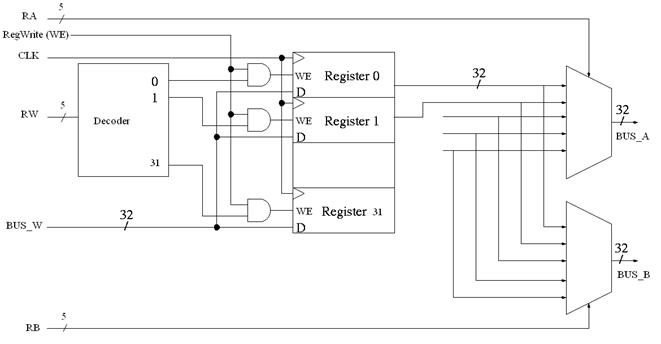

Регістровий файл зберігає вміст 32-х регістрів загального призначення процесору MIPS. Розрядність кожного регістру – 32 біти. Кожен регістр має номер від 0 до 31. Регістр з номером 0 завжди повертає 0 і записати будь-яке інше число в нього неможливо. Це особливість архітектури MIPS, яка використовується для спрощення виконання деяких інструкцій процесору. Фактично, процесор з архітектурою MIPS містить 31 регістр загального призначення, які можна використовувати для збереження даних користувача (програміста), а 0-й регістр завжди повертає нуль. Як видно з наведеного рисунку, регістровий файл має наступні входи та виходи: 1-бітний вхід тактового сигналу clk; 5-бітний вхід RW, що задає номер регістру в який буде записане число з 32-розрядного входу даних BusW у випадку активного (високого) рівня на 1-бітному вході дозволу запису RegWrite, 5-бітні входи RA, RB, що задають номери регістрів, вміст яких виводиться на 32-розрядні виходи даних BusA, BusB. Для запису даних в певний регістр, необхідно виконати наступну послідовність кроків: 1. Подати на вхід даних BusW число, яке хочемо записати в певний регістр; 2. Подати на вхід RW номер (адресу) регістру, в який буде проводитись запис; 3. Сформувати активний (високий) рівень на вході дозволу запису RegWrite; 4. Подати активний (передній) фронт на тактовий сигнал clk. В кожен момент часу з регістрового файлу можна зчитати вміст двох регістрів. Це необхідно, наприклад, для зчитування двох операндів для арифметико-логічного пристрою. Вміст регістру з номером, поданим на вхід RA, виводиться на вихід BusA. Вміст регістру з номером, поданим на вхід RB, виводиться на вихід BusB.

Реалізація регістрового файлу процесору MIPS наведена на рисунку нижче. У якості мультиплексорів можете використовувати мегафункції Quartus II.

Роботу створеного регістрового файлу необхідно перевірити шляхом симуляції. Спробуйте записати випадкові числа в усі 32 регістри (включаючи нульовий регістр). Після цього зчитайте значення з усіх регістрів. Переконайтесь, що для кожного регістру (крім нульового) зчитані і раніш записані числа є однаковими, а нульовий регістр завжди повертає 0.

|

||||

|

Последнее изменение этой страницы: 2016-04-23; просмотров: 348; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.137 (0.018 с.) |