Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Восьмиразрядный таймер/счётчик с поддержкой режима ШИМ

Назначение и особенности

Таймер/счётчик T0 – это универсальный восьмиразрядный счётный модуль с двумя независимыми модулями совпадения и с поддержкой ШИМ (PWM). Он позволяет формировать заданные промежутки времени (для работы в режиме реального времени). А также может служить генератором периодических сигналов. Рассмотрим основные характеристики таймера/счётчика.

Упрощенная блок-схема

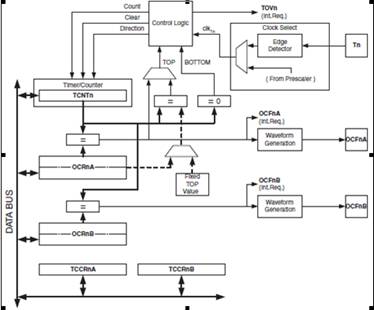

Упрощенная блок-схема восьмиразрядного таймера/счётчика приведена на рис. 9. Доступные для центрального ядра регистры и цепи передачи данных на схеме показаны полужирными линиями.

Рис. 9 - Блок-схема 8-разрядного таймера/счётчика Регистры

Как счётный регистр таймера/счётчика (TCNT0), так и оба регистра совпадения (OCR0A, и OCR0B) представляют собой восьмиразрядные регистры. Наличие запроса на прерывание (на рис.10 он сокращённо обозначен «выз. прерыв.») всегда можно определить по состоянию соответствующее флага прерываний в регистре TIFR. Каждое прерывание может быть индивидуально замаскировано при помощи регистра маски прерываний таймера TIMSK. Регистры TIFR и TIMSK на рис. 9 не показаны. Таймер/счётчик может работать как от внутреннего тактового генератора через предварительный делитель, так и от внешнего тактового сигнала, поступающего на вход T0. Схема выбора источника тактового сигнала пропускает тактовые импульсы выбранного источника на вход таймера/счётчика, и каждый импульс этого сигнала увеличивает (или уменьшает) его значение. Если не выбран ни один из источников тактового сигнала, таймер/счётчик останавливается. Сигнал на выходе схемы выбора источника тактового сигнала (clkT0) называется сигналом синхронизации таймера. Содержимое регистров OCR0Aи OCR0Bпостоянно сравнивается со значением таймера/счётчика. Результат сравнения может использоваться генератором для генерации сигнала ШИМ или прямоугольных импульсов переменной частоты на одном из выходов OC0Aили OC0B. В момент совпадения в одном из каналов устанавливается соответствующий флаг OCF0Aили OCF0B, который может использоваться для генерации запроса на прерывание по совпадению. Используемые обозначения

При описании счётчиков используются специальные обозначения для всех его важных состояний. Эти обозначения приведены в табл. 1.

Обозначения для основных состояний 8-разрядного счётчика

Таблица 1

Модуль счёта

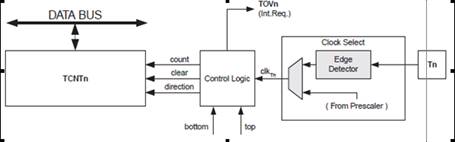

Основой восьмиразрядного таймера/счётчика является программируемый реверсивный счётный модуль. На рис. 10 показана блок-схема счётного модуля и его управляющие сигналы.

Рис. 10 - Блок-схема счётного модуля

Рассмотрим внутренние сигналы: ♦ count – увеличивает или уменьшает содержимое TCNT0 на 1; ♦ direction – выбор между уменьшением и увеличением; ♦ clear – очистка TCNT0 (установка всех битов в ноль); ♦ clkT0 – тактовая частота таймера/счётчика; ♦ top – возникает при достижении TCNT0 максимального значения; ♦ bottom – возникает при достижении TCNT0 минимального значения (нуля). В зависимости от режима работы таймера, каждый импульс тактового сигнала (clkT0) очищает, увеличивает или уменьшает значение счётчика. Сигнал clkT0может быть получен как от внешнего, так и от внутреннего источника тактового сигнала. Это определяется битами выбора тактового сигнала (CS02:0). Когда не выбран ни один источник тактового сигнала (CS02:0 = 0), таймер останавливается. Центральный процессор может обращаться к значению регистра TCNT0 независимо от того, присутствует ли сигнал clkT0 или нет. Команда записи, поступающая от центрального процессора, имеет приоритет над всеми другими операциями (очистки счётчика или операциями счёта). Режимы работы таймера определяются установкой битов WGM01 и WGM00 регистра TCCR0Aи битом WGM02 регистра TCCR0B. Есть тесная связь между выбранным режимом работы счётчика и частотой сигнала на выходе OC0A. Флаг переполнения таймера/счётчика (TOV0) устанавливается в соответствии с режимом работы, выбранным при помощи битов WGM01:0. Флаг TOV0 может использоваться для генерации прерываний центрального процессора.

Модуль совпадения

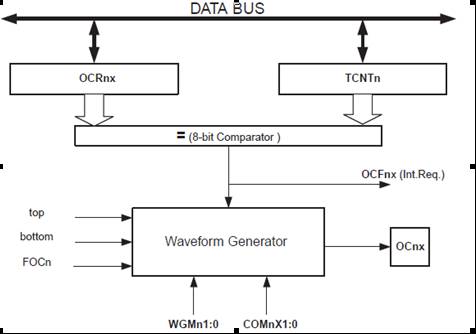

Основа модуля – восьмиразрядный компаратор, который непрерывно сравнивает содержимое регистра TCNT0 с содержимым каждого из двух регистров совпадения (OCR0Aили OCR0B). Каждый раз, когда содержимое TCNT0 оказывается равным содержимому OCR0Aили OCR0B, компаратор вырабатывает сигнал совпадения. Этот сигнал устанавливает соответствующий флаг совпадения (OCF0Aили OCF0B) в следующем тактовом цикле. Если соответствующее прерывание разрешено, установка флага совпадения вызывает прерывание. Флаг совпадения автоматически сбрасывается при запуске процедуры обработки прерывания. Флаг также может быть очищен программно путём записи в него логической единицы. В режиме генератора частот сигнал совпадения используется для генерации выводного сигнала совпадения используется для генерации выводного сигнала в соответствии с выбранным режимом работы, который определяется битами WGM02:0, а также битами выбора режима сравнения (COM0x 1:0). Сигналы max и bottom используются генератором частот в некоторых случаях для получения критических значений в отдельных режимах работы. На рис. 11 показана блок-схема модуля совпадения. На рисунке буква x – это условное обозначение. Для разных модулей совпадения x равно либо A либо B.

Рис. 11 - Блок-схема модуля совпадения Регистры OCR0xимеют двойную буферизацию в любом режиме широтно-импульсной модуляции (ШИМ). В режиме Normal и режиме СТС (Сброс при совпадении) двойная буферизация отключается. Двойная буферизация синхронизирует момент обновления регистра OCR0xс моментом достижения таймером верхнего или нижнего пределов. Синхронизация предотвращает возникновение ассиметричных ШИМ-импульсов, то есть импульсов, длина которых равна нечётному количеству тактов. Таким образом обеспечивается высокое качество сигналов ШИМ. Доступ к регистру OCR0xможет показаться слишком сложным. На самом деле это не так. Если двойная буферизация разрешена, центральный процессор обращается к регистрам OCR0xчерез буфер. Если буферизация отключена, центральный процессор обращается к регистрам OCR0xнепосредственно.

|

||||||||||||

|

Последнее изменение этой страницы: 2021-01-08; просмотров: 340; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.12.166.61 (0.007 с.) |