Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Тема №3. Устройство сравнения двоичных чиселСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

ТЕМА №3. УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ Описание принципа работы заданной структурной электрической схемы устройства сравнения двоичных чисел

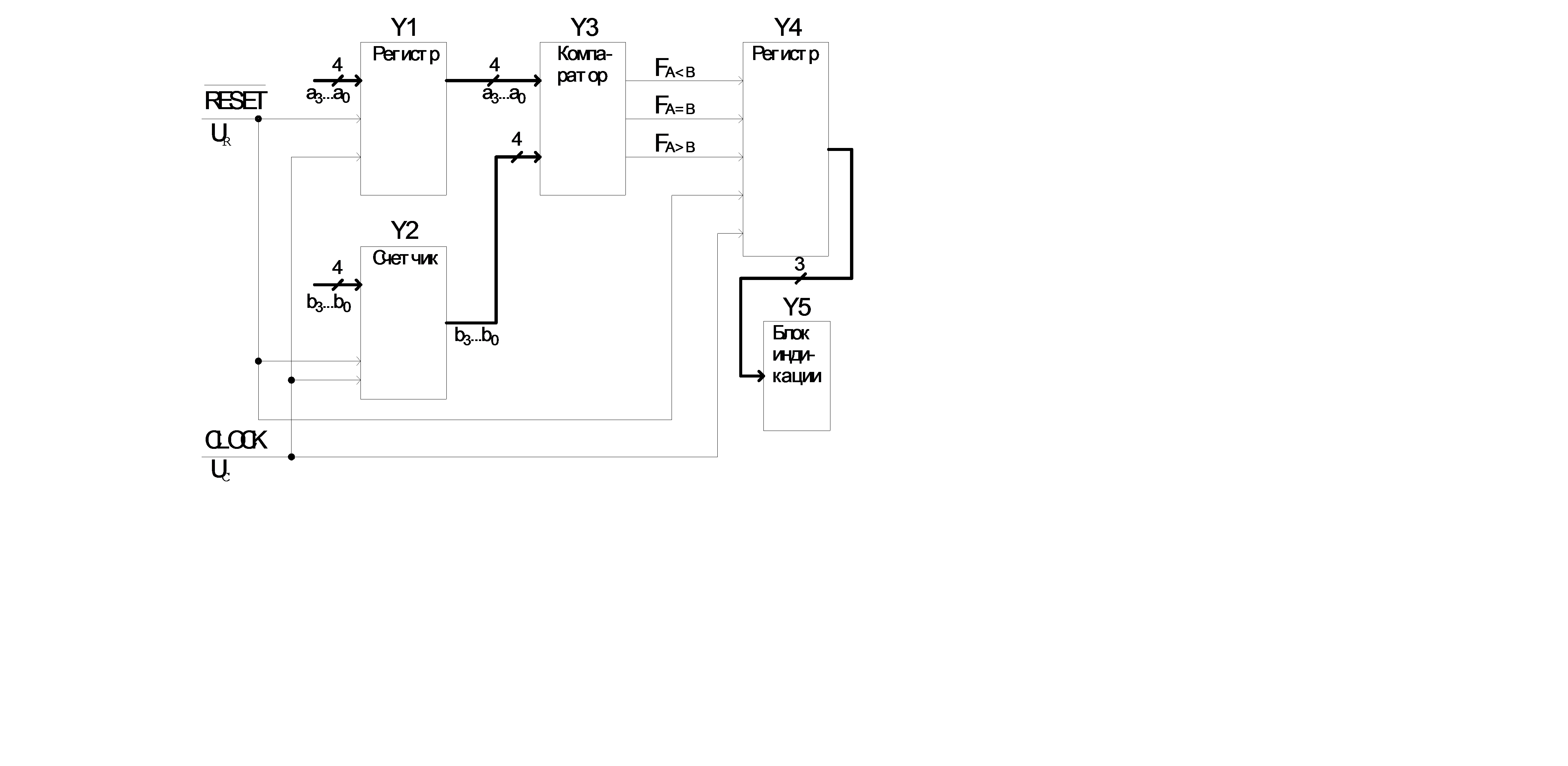

Структурная электрическая схема устройства сравнения двоичных чисел представлена на риунке 3.1.

Рисунок 3.1 – Устройство сравнения двоичных чисел. Схема электрическая структурная

Рассмотрим назначение узлов, входящих в структурную схему устройства сравнения. Компаратор Y3 предназначен для сравнения четырехразрядных двоичных чисел А и B, представленных разрядами a3…a0 и b3…b0. На выходах компаратора формируются сигналы, фиксирующие результат сравнения. Регистр Y1 предназначен для параллельного ввода четырехразрядного операнда A в двоичной СС, значение которого может менятся в пределах от 0 до F в шестнадцатеричной СС. Счетчик Y2 предназначен для параллельного ввода операнда B в двоичной СС, значение которого также может менятся от 0 до F. Регистр Y4 предназначен для фиксации результата сравнения, который представляет собой трехразрядное слово. Блок индикации Y5 предназначен для индикации результата сравнения с помощью светодиодных индикаторов. Работа устройства синхронизируется тактовыми импульсами Uс. Процесс функционирования устройства поясняется временной диаграммой, которая представлена на рисунке 4.2.

Рисунок 3.2 – Временная диаграмма, поясняющая процесс функционирования устройства сравнения

В момент времени t1 по отрицательному фронту тактового импульса (рисунок 4.2) начинается ввод операндов А и В в регистр Y1 и счетчик Y2 (рисунок 4.1). К моменту времени t2 ввод заканчивается, и начинается процесс сравнения в компараторе. Этот процесс в худшем случае завершается к моменту времени t3. Затем по положительному фронту тактового импульса результат сравнения фиксируется в регистре Y4 и одновременно поступает в блок индикации Y5. Например, при сравнении равных операндов A = B = 1101(2) на выходе FA = B компаратора Y3 вырабатывается единичный сигнал, а на выходах FA < B и FA > B вырабатываются нулевые сигналы1).

Задание на проектирование к теме №3

Описать принцип построения и разработать в основном базисе логическую схему четырехразрядного компаратора двоичных чисел. Разработать логическую схему суммирующуего четырехразрядного счетчика с коэффициентом пересчета Кпер, заданным в таблице 3.1. Разработать принципиальную электрическую схему устройства сравнения по заданной структурной схеме (рисунок 3.1) на микросхемах схемотехники КМОП, серии которых указаны в таблице 3.1.

Таблица 3.1 – Исходные данные для проектирования устройства сравнения двоичных чисел

Описать работу принципиальной электрической схемы устройства сравнения в течениие одного периода сигнала синхронизации Uс при сравнении заданных в таблице 3.1 операндов A и B.

Варианты заданий на проектирование к теме № 5

В соответствии с номером варианта разработать цифровое устройство обработки данных, выполняющее заданные функции.

Вариант № 4.1

– Прием по шине параллельной передачи данных восьмиразрядного двоичного кода; – формирование разряда четности; – хранение девятиразрядного двоичного кода (девятый разряд четности); – выдача девятиразрядного кода на линию последовательной передачи данных младшими разрядами вперед.

Вариант № 4.2

– Прием по шине параллельной передачи данных девятиразрядного двоичного кода; – проверка принятой информации на четность со световой индикацией ошибки; – хранение информационных разрядов; – выдача восьмиразрядного кода на линию последовательной передачи данных младшими разрядами вперед. – Вариант № 4.3

– Прием по линии последовательной передачи данных девятиразрядного двоичного кода младшими разрядами вперед (девятый разряд – разряд нечетности); – проверка принятой информации на нечетность со световой индикацией ошибки; – хранение информационных разрядов; – выдача восьмиразрядного двоичного кода на шину параллельной передачи данных.

Вариант № 4.4

– Прием по линии последовательной передачи данных двух четырехразрядных двоичных кодов (последовательно); – хранение принятой информации; – сравнение четырехразрядных двоичных кодов; – индикация большего четырехразрядного двоичного числа; – хранение результата; – выдача на шину параллельной передачи данных большего кода.

Вариант № 4.5

– Прием по шине параллельной передачи данных двух четырехразрядных двоичных кодов (последовательно); – хранение принятой информации; – сравнение четырехразрядных двоичных кодов; – индикация меньшего четырехразрядного двоичного кода; – хранение результата; – выдача на линию последовательной передачи данных меньшего двоичного кода.

Задание на проектирование к теме № 4

Разработать и описать структурную электрическую схему устройства обработки данных, выполняющего заданные функции. Разработать логическую схему блока управления на основе распределителя импульсов. Описать назначение и принцип построения устройств контроля по модулю 2 (варианты 5.1…5.3) или компараторов (варианты 5.4 и 5.5). Выбрать микросхемы схемотехники КМОП серий 1564, 1554, либо 1594, 5564 для реализации узлов устройства. Описать выбранные микросхемы (привести их условные графические обозначения, таблицы состояний, указать выполняемые функции и режимы работы). Разработать принципиальную электрическую схему устройства обработки данных и временные диаграммы работы (пример для варианта № 5.5 приведен в приложении Е). Описать работу принципиальной электрической схемы устройства обработки данных в течение одного периода сигнала синхронизации

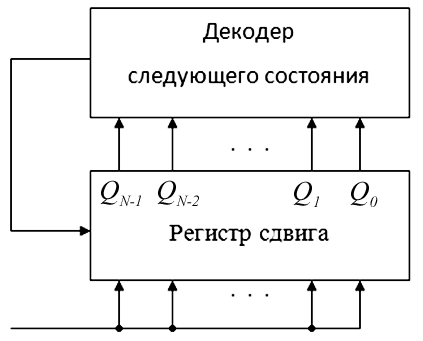

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ Схема, которая генерирует заданную последовательность бит синхронно с импульсами синхронизации, называется генератором последовательностей. Такие генераторы используются как: 1. Счетчики; 2. Генераторы псевдослучайных последовательностей; 3. Генераторы заданной последовательности и заданного периода; 4. Генераторы кодов. Генераторы последовательностей являются одним из наиболее интересных применений регистров сдвига. Блок-схема генератора последовательностей показана на рисунке 1

Рис. 1 Блок-схема генератора последовательностей

Выход декодера следующего состояния Y- это функция от QN-1, QN-2, …, Q0, т.е. Синтез генераторов последовательностей рассмотрим на примерах. Пример 1. Синтезировать генератор следующей последовательности … 1101011 …. Решение. При синтезе генератора заданной последовательности необходимо определить число разрядов регистра сдвига и комбинационную схему декодера следующего состояния. Минимально возможное число триггеров N в регистре сдвига для генерирования последовательности длинной S бит определяется из того, что

В данном примере S=7, поэтому минимально возможное значение N=3. Однако это не значит, что это число триггеров является достаточным. Если данная последовательность ведет к семи различным состояниям регистра, то тогда три триггера будет достаточно, в противном случае число триггеров придется увеличить. Запишем состояние регистра в виде таблицы 1.

Таблица 1

Допускаем, что данная последовательность генерируется на выходе Q2. В таком случае на выходах Q1 и Q0 будет та же последовательность, только задержанная на один и два такта, соответственно. Из таблицы 1 видно, что не все состояния регистра отличаются от других (первая и вторая строки одинаковы, а также четвертая и шестая), что означает - число триггеров регистра N=3 не является достаточным. Поэтому примем число N=4 и построим таблицу аналогичную табл. 2. Поскольку в данном случае все состояния регистра являются отличными (разными), добавим в эту таблицу колонку, в которой запишем требуемую последовательность на входе регистра, Y.

Таблица 2

с помощью карты Карно, рис 1 с помощью карты Карно, рис 1

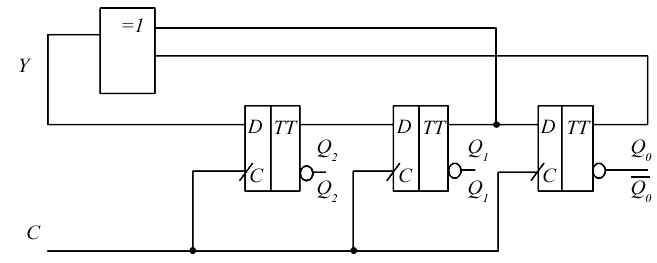

Рис. 1. Упрощение ФАЛ декодера следующего состояния Упрощенная схема генератора последовательности … 1101011 … показана на рис. 2

Рис. 2 Логическая структура генератора последовательности … 1101011 …. Пример 2. Синтезировать генератор последовательности … 1101001…. Решение. Минимально возможное число триггеров регистра N=3. Проверим является ли это число достаточным. Для этого построим таблицу 3.

Таблица 3

Из таблицы 3 видно, что все состояния регистра являются неодинаковыми, т.е. число триггеров N=3 является достаточным для реализации генератора, и поэтому добавим в эту таблицу колонку с требуемой на входе регистра последовательностью. Схему декодера получим, упрощая функцию

На рисунке 3 показана упрощенная схема генератора последовательности … 1101001….

Рис. 3 Логическая структура генератора последовательности … 1101001….

Длина последовательности, генерируемой генератором, рис. 3, равна Генераторы, которые генерируют последовательности длины

называются генераторами последовательностей максимальной длины. Такие генераторы широко используются для генерирования помехоустойчивых кодов.

Синтезировать и построить генератор последовательности.

Выполнить моделирование в среде схемотехнического моделирования Multisim.

ТЕМА №7. Синтез цифрового автомата Мили.(на10) . Последовательная схема имеет входной калал - Z, вход синхронизации и выходной канал - W. Поступающие на вход Z данные делятся на группы, содержащие по четыре двоичные цифры, которые не перекрывают друг друга. Проверяются логической схемой и при обнаружении комбинаций хххх, хххх, хххх, хххх на выходе появляется 1. Сигнал на выходе должен иметь длительность, равную длительности синхронизирующего импульса. При всех других комбинациях четырех двоичных цифр сигнал на выходе должен быть равен 0.

Выполнить моделирование в среде схемотехнического моделирования Multisim.

[1]) В пояснительной записке следует приводить пример умножения для чисел A и B согласно заданному варианту. [2]) В пояснительной записке следует анализировать пример умножения для чисел A и B согласно заданному варианту. [3]) В пояснительной записке следует приводить пример суммирования для чисел A и B согласно заданному варианту. ТЕМА №3. УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-02-10; просмотров: 821; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.17.135.12 (0.008 с.) |

. Пример оформления задания к теме № 5 приведен в приложении Б.

. Пример оформления задания к теме № 5 приведен в приложении Б.

. Это схема подобна схеме кольцевого счетчика (Y=Q0) или счетчика Джонсона (

. Это схема подобна схеме кольцевого счетчика (Y=Q0) или счетчика Джонсона ( ). Кольцевой счётчик и счётчик Джонсона являются частными случаями генераторов последовательностей.

). Кольцевой счётчик и счётчик Джонсона являются частными случаями генераторов последовательностей. (1)

(1)

с помощью карты Карно.

с помощью карты Карно.

.

. (2)

(2)