Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Создание тестового модуля проекта в форме временных диаграммСодержание книги

Поиск на нашем сайте

Для автоматического формирования основы файла тестовой последовательности необходимо активизировать режим создания нового модуля исходного описания проекта, воспользовавшись кнопкой

Рис. 1. Диалоговая панель установки исходных параметров тестового модуля проекта

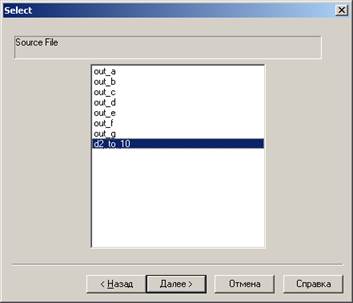

Установка значений всех необходимых исходных параметров создаваемого модуля завершается нажатием клавиши Далее (Next), которая находится в нижней части диалоговой панели (рис. 1). В результате чего на экране отображается следующая диалоговая панель, содержащая список модулей исходного описания проекта. В предлагаемом списке следует выделить элемент (файл, содержащий схему), с которым ассоциируется создаваемый тестовый модуль, поместив курсор на соответствующую строку и щелкнув левой кнопкой мыши. Сделанный выбор подтверждается нажатием клавиши Далее (Next), расположенной в нижней части диалоговой панели.

Рис. 2. Диалоговая панель выбора объекта для генерации тестового файла

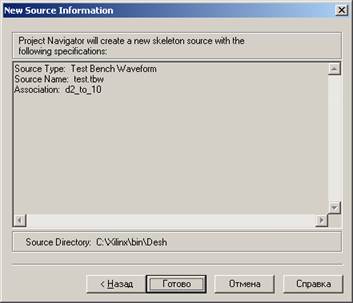

При успешном создании основы тестового модуля открывается информационная панель, показанная на рис. 3. В этой панели отображаются значения всех параметров создаваемого модуля. Если необходимо изменить значение какого-либо параметра, то кнопка Назад (Back) позволяет вернуться к предыдущей диалоговой панели. Процесс создания основы тестового модуля завершается нажатием кнопки Готово (Finish), находящейся в нижней части информационной панели (рис. 3).

Рис. 3. Информационная панель параметров создаваемого тестового модуля проекта.

Выбор объекта завершается нажатием клавиши Готово, после чего открывается диалоговая панель инициализации временных параметров (рис. 4). Временные параметры, необходимые для формирования тестовых сигналов, различаются для синхронных и асинхронных устройств. Программа HDL Bencher автоматически определяет тип устройства, для которого разрабатываются тестовые последовательности.

Для синхронного устройства необходимо, прежде всего, проконтролировать и при необходимости изменить выбор основного тактового сигнала, в поле Single clock, используя выпадающий список интерфейсных сигналов устройства. Затем следует выбрать единицы измерения временных параметров, используя выпадающий список возможных значений поля Time scale. Далее нужно определить длительность состояний высокого и низкого логических уровней периода тактового сигнала в поле редактирования Clock high time и Clock low time соответственно. Кроме того, в поле редактирования Input setup time следует указать минимальное значение времени установки входных сигналов, а в поле Output valid delay максимальное значение задержки выходных сигналов. Программа HDL Bencher автоматически определяет, чем тактируется устройство - фронтом (Rising edge), спадом (Falling edge) тактового сигнала или тем и другим (Dual edge), но разработчик может выбрать это вручную, используя соответствующие кнопки диалоговой панели (рис. 4). При создании тестов для комбинационных устройств нужно указать только значения временных интервалов между моментами подачи входных воздействий и контроля выходных сигналов Check outputs и Assign Inputs. Эти параметры позволяют исключить возможные конфликты в моменты изменения входных и выходных сигналов.

Рис. 4. Диалоговая панель инициализации временных параметров утилиты HDL Bencher исправить картинку

Процесс установки требуемых значений временных параметров завершается нажатием кнопки ОК, расположенной в нижней части диалоговой панели (рис. 5), после чего в рабочей области окна программы HDL Bencher отображаются заготовки временных диаграмм (рис. 5).

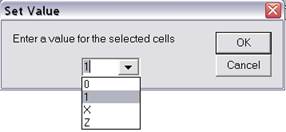

Рис. 5. Заготовки временных диаграмм В верхней строке рабочей области окна программы HDL Bencher расположена временная шкала, деления которой соответствуют периодам тактового сигнала. В левом столбце отображается список названий интерфейсных сигналов устройства. Справа от названия сигнала приведена пиктограмма, обозначающая его тип: тактовый; входной; выходной и двунаправленный соответственно. Сигналы векторного типа отображаются в виде шин соответствующей разрядности. Изменить значение сигнала в какой-либо момент времени можно несколькими способами. Чтобы переключить значение сигнала на противоположное (из состояния низкого логического уровня в высокое или наоборот), достаточно поместить курсор в требуемое место временной диаграммы и щелкнуть левой кнопкой мыши. Чтобы выбрать значение сигнала из списка возможных состояний, следует щелчком правой кнопки активизировать контекстно-зависимое всплывающее меню, в котором выбрать строку Set Value. В результате выполнения указанных действий на экран выводится диалоговая панель, содержащая поле выбора значения сигнала (рис. 6). Для установки требуемого значения сигнала следует нажать кнопку управления выпадающим списком возможных состояний, в котором выбрать затем соответствующую строку, после чего подтвердить выбор нажатием кнопки ОК (рис. 6).

Рис. 6. Диалоговая панель выбора значения сигнала

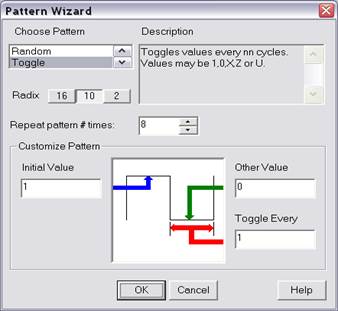

Чтобы сформировать последовательность значений для выбранного сигнала, можно воспользоваться соответствующим "мастером" Pattern Wizard. Для его активизации необходимо поместить курсор мыши в исходную точку временной диаграммы и дважды щелкнуть левой кнопкой, после чего воспользоваться появившейся кнопкой Pattern. В диалоговой панели "мастера" Pattern Wizard, показанной на рис. 7, следует выбрать алгоритм переключений сигнала в поле Choose Pattern и указать: начальное значение в поле редактирования Initial Value, альтернативное значение в поле Other Value, интервал переключения в поле Toggle Every и количество формируемых периодов сигнала в поле Repeat pattern. После нажатия кнопки ОК, расположенной в нижней части диалоговой панели (рис. 7), сформированный фрагмент временной диаграммы отображается в рабочей области. Команды меню Edit и контекстно-зависимого всплывающего меню позволяют копировать в буфер и затем вставлять в нужное место выбранные фрагменты временных диаграмм.

Рис. 7 Диалоговая панель "мастера" Pattern Wizard

На изображении временных диаграмм присутствует указатель конечной точки тестовой последовательности (вертикальная синяя линия), положение которого устанавливается автоматически или "вручную". Выбор режима определения окончания тестового вектора осуществляется с помощью команды Configuration из всплывающего меню Options, в результате выполнения которой на экран выводится диалоговая панель, показанная на рис. 8. Параметр Automatically determine end oftest bench управляет выбором режима, в котором выполняется установка маркера конечной точки тестового вектора. По умолчанию используется значение "включено", соответствующее автоматическому режиму, при котором указатель располагается в начале тактового интервала, следующего за моментом последнего изменения входных сигналов. При перемещении маркера с помощью мыши происходит переключение из автоматического режима в "ручной".

Рис. 8 Диалоговая панель параметров конфигурации программы HDL Bencher

Параметр VHDL Compatibility, представленный в этой же диалоговой панели в виде двух кнопок, позволяет выбрать стандарт языка VHDL, в соответствии с которым формируется описание тестовой системы. По умолчанию установлен режим совместимости со стандартом IEEE VHDL Std 1076-1993. Завершив редактирование временных диаграмм тестовых сигналов, следует сохранить их, используя команду Save Waveform из меню File. При этом, если указатель окончания тестовой последовательности был установлен до момента последнего изменения входных или контроля формирования выходных сигналов, выводится панель предупреждения, в которой предлагается перенести маркер в соответствующую позицию.

По окончании формирования тестового файла следует выделить строку с его названием в окне исходных модулей Навигатора проекта, поместив на нее курсор мыши и щелкнув левой кнопкой. В результате в окне процессов отображается интерактивный список этапов моделирования проектируемого устройства. Содержание окна процедур в этом режиме определяется видом семейства ПЛИС, выбранного для реализации проекта, но независимо от типа используемого кристалла первым в списке является этап функционального моделирования. На рис. 9 показан вид рабочей области Навигатора проекта, в которой отображаются этапы моделирования в процессе проектирования устройства на базе ПЛИС семейств CPLD при использовании средств синтеза XST VHDL. Строка Simulate Behavioral VHDL Model соответствует этапу функционального моделирования, a Simulate Post-Fit VHDL Model полного временного.

Рис. 9. Отображение этапов моделирования устройств, разрабатываемых на базе ПЛИС семейств CPLD, в рабочей области Навигатора проекта пакета WebPACK ISE

Все этапы моделирования проекта выполняются в пакетном режиме. Поэтому далее основное внимание уделяется описанию параметров инициализации программы ModelSim и временной модели, с помощью которых осуществляется управление процессом моделирования. Состав этих параметров зависит от языка описания аппаратуры HDL и средств синтеза, используемых в процессе проектирования. В последующих разделах данной главы будут рассмотрены параметры процессов моделирования проектов, разрабатываемых на основе кристаллов семейств CPLD с применением средств синтеза XST VHDL.

|

||||||||||

|

Последнее изменение этой страницы: 2017-02-07; просмотров: 269; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.137.178.186 (0.011 с.) |

на оперативной панели или командой New Source из раздела Project основного меню Навигатора проекта. В открывшейся диалоговой панели, показанной на рис. 1, в качестве типа нового модуля следует выбрать Test Bench Waveform. Далее необходимо задать его имя и указать место расположения файла на диске в поле редактирования Location.

на оперативной панели или командой New Source из раздела Project основного меню Навигатора проекта. В открывшейся диалоговой панели, показанной на рис. 1, в качестве типа нового модуля следует выбрать Test Bench Waveform. Далее необходимо задать его имя и указать место расположения файла на диске в поле редактирования Location.